简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

AXI(Advanced eXtensible Interface)协议的乱序传输(Out-of-Order)机制是现代高性能SoC设计的核心特性之一。本文深入探讨AXI如何通过ID标识符和通道独立性实现高效的数据乱序传输,显著提升总线利用率和系统并发性能

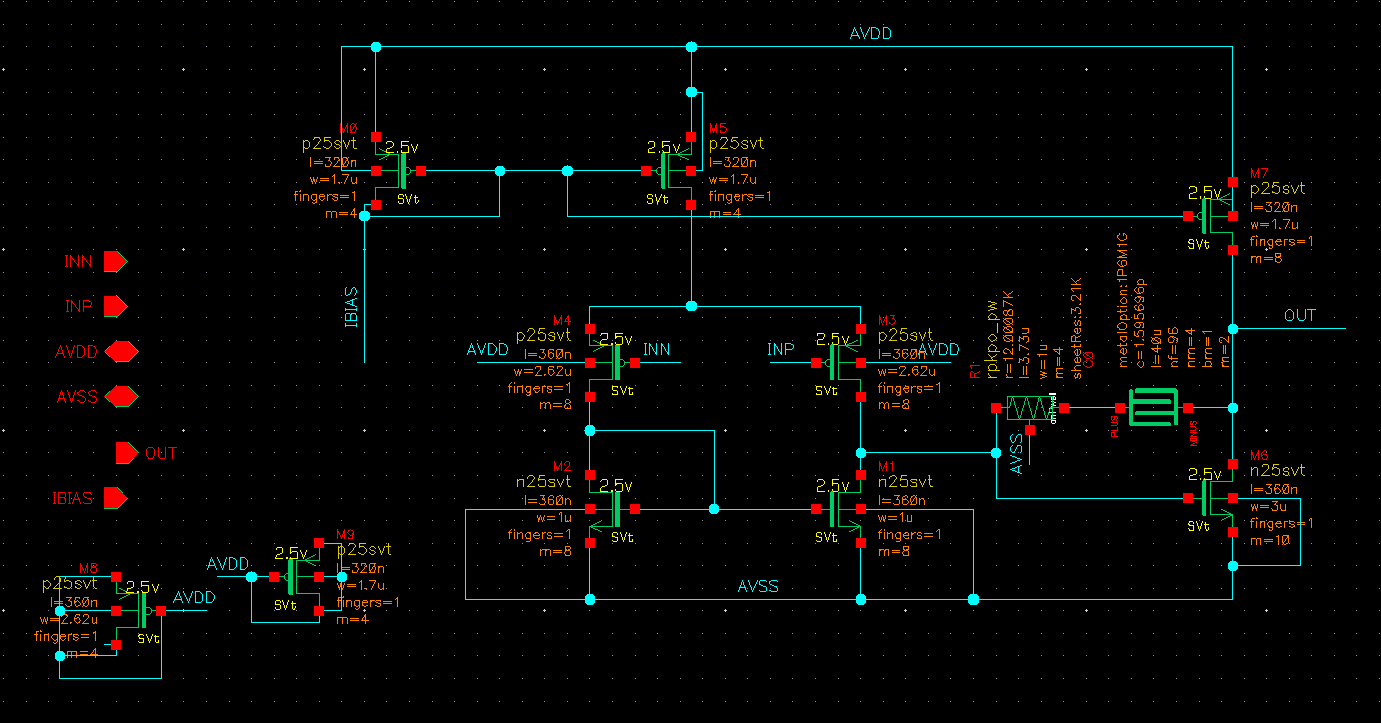

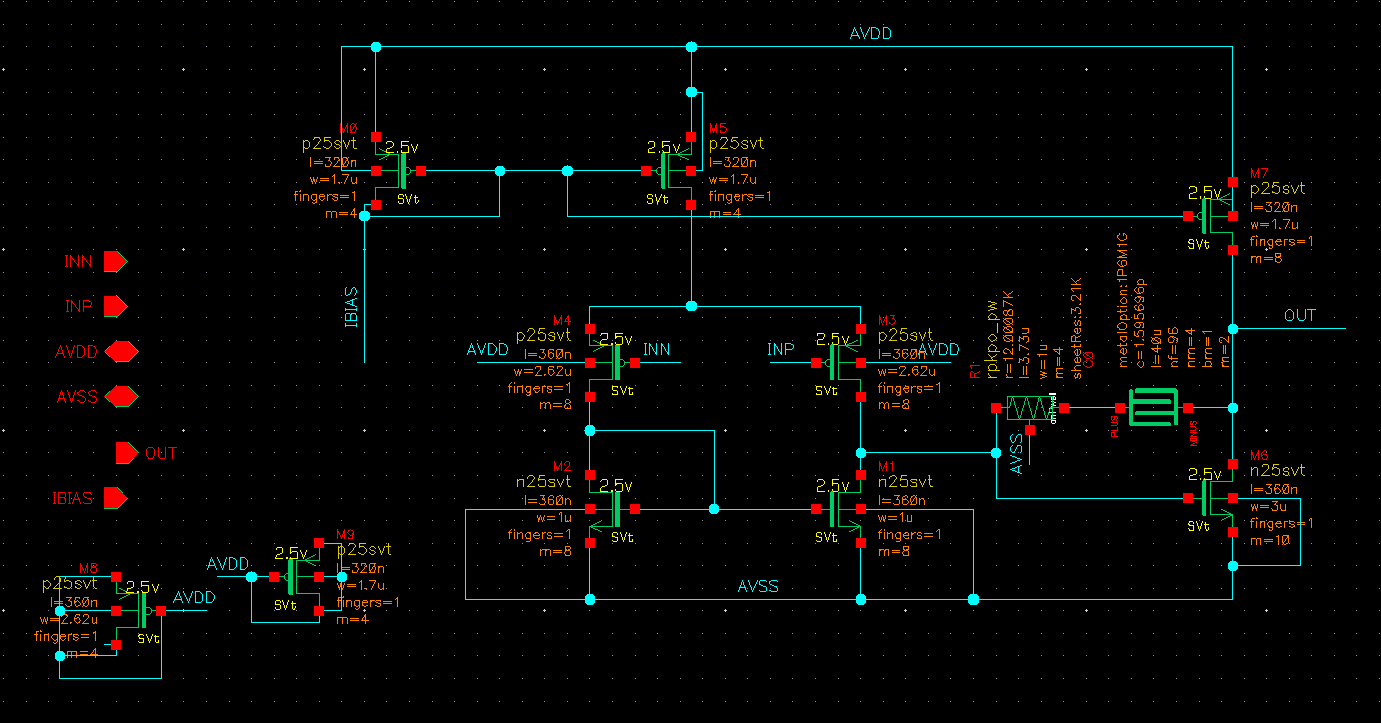

本文详细记录了反相放大器从版图设计到后仿真的全流程,涵盖器件布局、金属连线规则、DRC/LVS检查等核心步骤,并通过寄生参数抽取(PEX)深入分析版图寄生效应对性能的影响。实验对比前仿与后仿结果(增益、GBW、相位裕度),验证了版图优化的有效性,提供减少寄生电阻/电容的实用方法,助力提升电路稳定性和工艺稳健性。

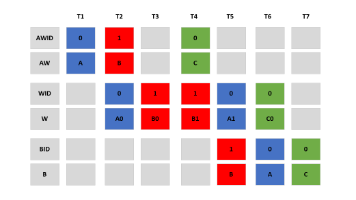

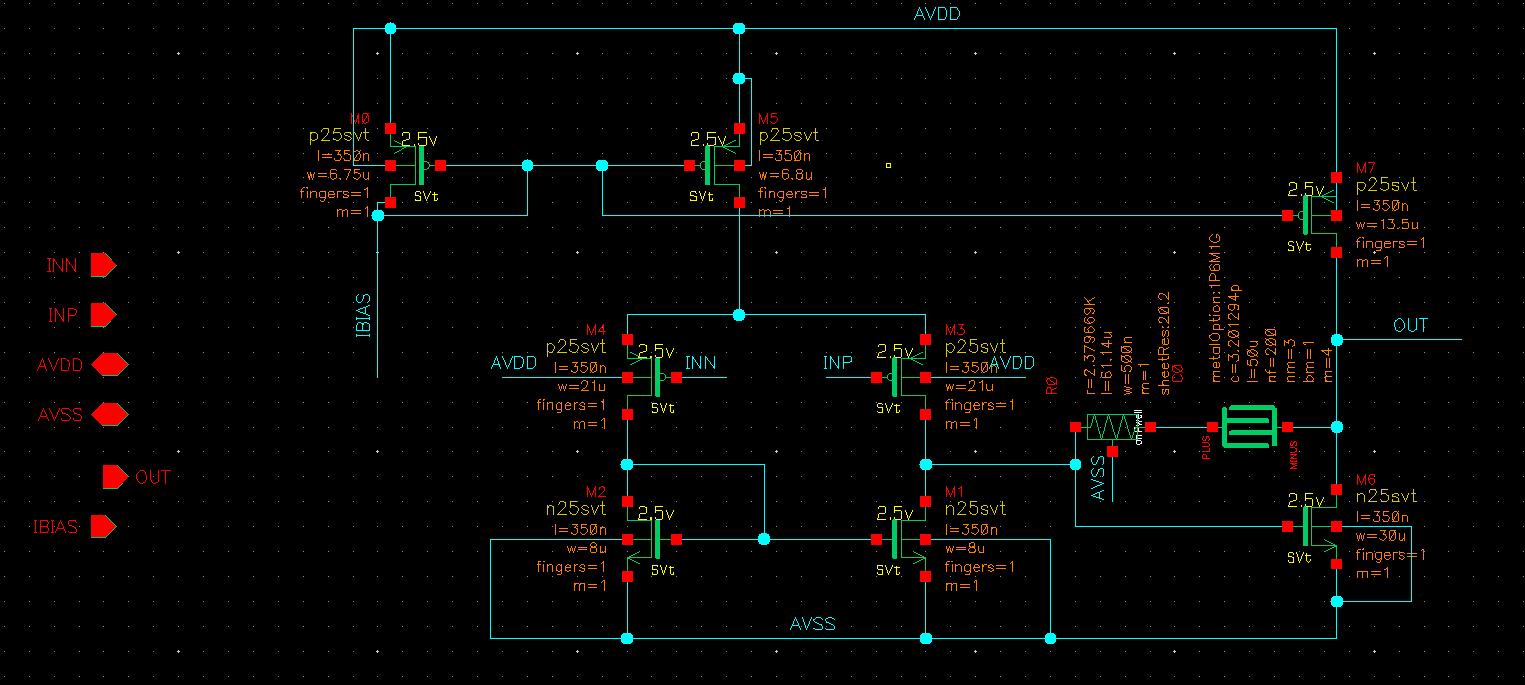

本文以两级运算放大器设计为核心,系统讲解了输入级、输出级及密勒补偿电路的设计原理,并通过DC、AC、PSRR、CMRR、压摆率等多维度仿真验证其性能。实验覆盖五种工艺角分析,揭示增益与带宽的权衡关系,提出降低功耗、优化相位裕度的策略,为高性能运放设计提供理论与实践结合的完整参考。

本文系统性地探讨了六种典型除法器实现方案,涵盖硬件级位操作算法与数值优化方法,重点解决定点数处理中的精度控制与舍入误差问题,文档提供可直接运行的Python参考实现,包含位操作可视化说明和算法复杂度分析,适合嵌入式系统开发者、硬件算法工程师及对数值计算感兴趣的研究人员参考。

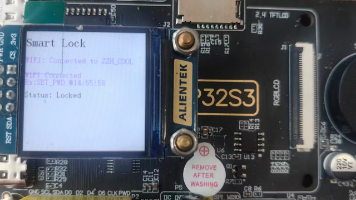

本项目是一个自学实战项目,综合性强,难度高。基于 ESP32 和 FreeRTOS 构建的商业级双端智能门禁 IoT 系统。它采用严格的 MVC 架构与事件驱动模型,在单片机上实现了本地硬件无阻塞交互与 MQTT 云端管控的毫秒级无缝融合,并具备断电记忆、防暴自锁和云端网络对时审计功能

本项目是一个自学实战项目,综合性强,难度高。基于 ESP32 和 FreeRTOS 构建的商业级双端智能门禁 IoT 系统。它采用严格的 MVC 架构与事件驱动模型,在单片机上实现了本地硬件无阻塞交互与 MQTT 云端管控的毫秒级无缝融合,并具备断电记忆、防暴自锁和云端网络对时审计功能

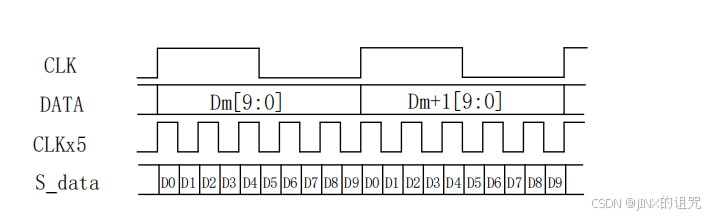

本文以FPGA与USB高速通信为核心,聚焦 Cypress FX2(CY7C68013)芯片的应用,通过Slave FIFO模式实现从理论到实践的完整开发流程。提供完整Verilog代码、可直接复用于项目开发

文章以ODDR, OBUFDS以例,介绍了 Vivado 语言模板块的使用,同时综合了HDMI的TMDS编码、串行数据发送,TFT显示等模块,主打显示的的小工程,值得FPGA发烧友学习

本文详细记录了反相放大器从版图设计到后仿真的全流程,涵盖器件布局、金属连线规则、DRC/LVS检查等核心步骤,并通过寄生参数抽取(PEX)深入分析版图寄生效应对性能的影响。实验对比前仿与后仿结果(增益、GBW、相位裕度),验证了版图优化的有效性,提供减少寄生电阻/电容的实用方法,助力提升电路稳定性和工艺稳健性。