简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

源同步FPGA输入时序分析的模型以下为源同步FPGA输入时序分析的模型的示意图,在之前的文章中介绍过,在此介绍一下各个时钟延时的含义。Tco:到上游器件接口的数据延迟,这个延迟其实包括时钟源到寄存器D端的延迟、寄存器内部的延时Tco、Q端到输出接口的延迟,在这里统称为Tco。Td_bd:数据延迟路径,板级布线的延迟(PCB)Td_fi:FPGA内部到寄存器D端延迟,这部分的延时FPGA的综合工具类

目录边缘对齐采样时序图更改PLL参数综合布线report timing路径分析两种约束模型第一种模型实际操作添加约束路径分析第二种模型顶层代码添加时钟约束解决办法input delay约束综合布线结果总结往期系列博客边缘对齐采样边缘对齐采样的方式进行input delay约束,在系列第八讲中介绍过,在边缘对齐采样的情况下,容易出现保持时间余量不足的情况,这是由于在发射时钟的下一个时钟作为采样时钟去

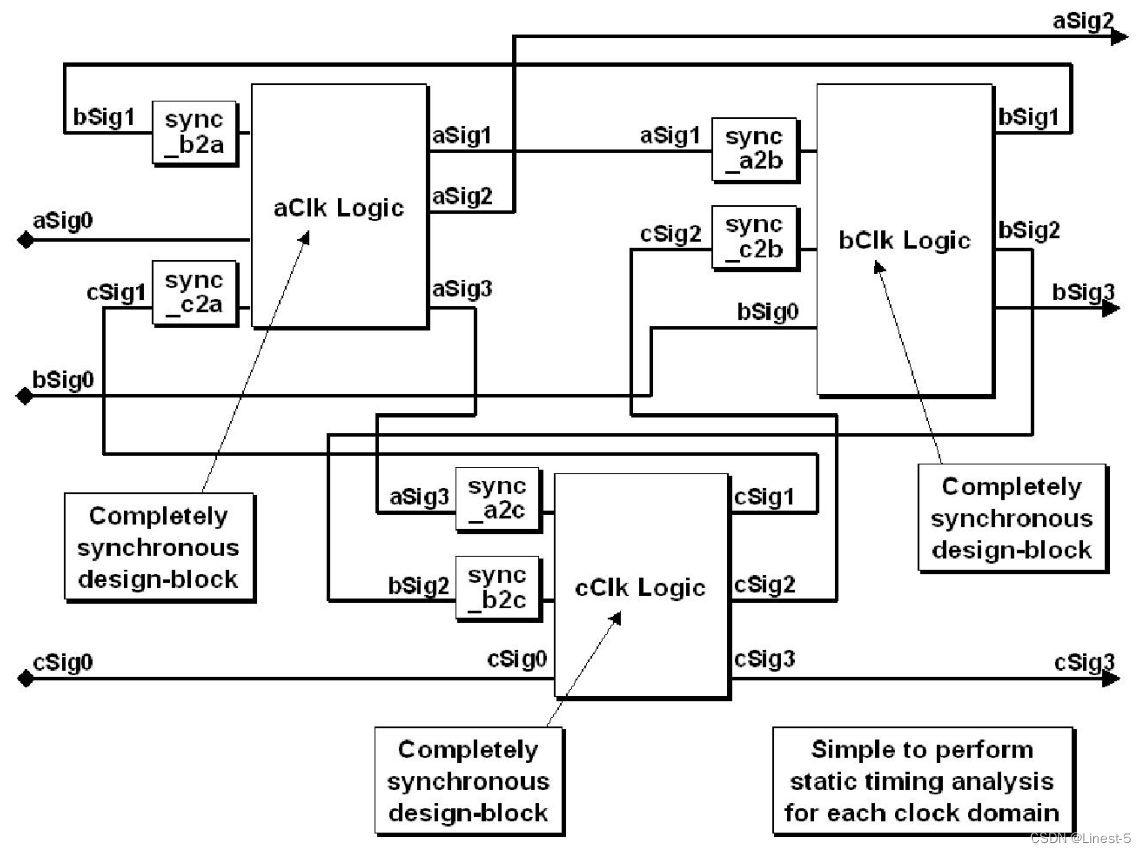

目录命名约定和设计划分时钟和信号命名约定没有命名约定的多时钟/多源模块每个时钟域的时序验证面向时钟的设计划分时钟分区模块的时序分析使用 MCP 方法进行分区多时钟门级仿真问题同步器门级 CDC 仿真问题从门级仿真中去除 X 传播的策略关闭时序检查的模拟器命令将触发器建立和保持时间更改为 0复制和修改新的触发器模型使用多个 SDF 文件总结与结论单 bit CDC 技术多 bit CDC 技术推荐的

目录DDR采样简述第一种模型(不带PLL)实际操作总结约束实际工程顶层代码时钟约束input delay约束查看时序报告解决办法添加原语原语解释查看时序报告时序分析总结往期系列博客DDR采样简述在之前分析了SDR采样,也就是单边采样,接下来介绍DDR采样,也就是双边采样,在实验应用中,DDR采样也是很广泛的,比如CMOS、DRAM、ADC、千兆以太网等,都是DDR接口的,因此也需要去分析时序是否正

目录状态机介绍状态机类型Moore 型状态机Mealy 型状态机状态机设计流程自动售卖机状态机设计:3 段式(推荐)实例实例状态机修改:2 段式实例状态机修改:1 段式(慎用)实例状态机修改:Moore 型实例实例有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。状态机不仅是一种电路的描述工具,而且也是一种思

目录说明1、理论基础2、matlab仿真3、仿真图像4、程序代码说明本文为转载,为了方便自己以后学习,原文链接如下基于MATLAB的混频测试1、理论基础就是高中学习的公式。从公式中可以看出,两个信号相乘后,可以得到两个信号频率和和差的叠加,就比如在信号处理时,如果外部输入信号是5MHz,系统本振信号是10MHz,那经过这一系统后,可以得到5M和10M信号的叠加,如果经过一个低通滤波器,比如滤掉1

出现这样的问题是由于代理服务器连接失败导致的。解决办法也很简单,如下:1、点开电脑设置:点击电脑屏幕左下角的开始,点开设置。2、打开Windows设置之后,点击网络和Internet。3、点击代理选项,分别关闭图片中的选项:自动检测设置、使用设置脚本、使用代理服务器。最后浏览器就能正常连接网络啦~...

在工程实验中常见的错误

离散傅里叶正变换:表面上看是对时域采样数据进行 N点离散傅里叶正变换, 实质上求的是被采样信号周期性拓展得到的周期信号的傅里叶系数再乘以点数 N。离散傅里叶逆变换:表面上看是对频域采样数据 X(k) 进行 N 点离散傅里叶逆变换, 实质上是用 X(k) / N 作为傅里叶系数对复指数信号进行加权合成一个周期信号, 再对一个周期进行采样得到 N 个时域采样数据。...

目录问题描述调试过程总结问题描述在第一次使用AX7103这块黑金的板子,打算先做个helloworld的串口打印实验来验证板子的可行性,在创建工程BD如图所示,很简单的一个uart打印实验。添加约束文件并生成比特流文件后,将硬件信息导入到SDK中,并新建一个新的工程,直接调用helloworld模板就可以了,于是出现了如标题所示的报错。不能停止MicroBlaze,MicroBlaze处于复位状态