简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

参考:https://blog.csdn.net/u012654584/article/details/104921700

时钟频率(Clock Frequency)频率决定了NPU芯片及其MAC单元每秒运行的周期次数(赫兹,Hz)。厂商在公布TOPS时,使用的是NPU的峰值运行频率(即能达到的最高频率)。目标跟踪的过程本质上是利用一个已经训练好的检测模型(比如YOLOv8),对视频的每一帧进行目标检测,然后通过跟踪算法(如BoT-SORT、ByteTrack)将这些检测框在时间序列上关联起来,形成连续的轨迹。1.训练

2.阻抗匹配的本质是让信号“平稳过河”——当源端与负载的阻抗“桥墩”高度一致时,信号能量可无损通过;2.信号反射问题,LVDS的跳变沿遇到阻抗突变,发射系数很大,原始信号叠加反射波后,1.不接终端电阻,驱动器的3.5mA横流源没有释放路径,相当于开路状态。1.阻抗匹配是调整天路中阻抗的关系,使得信号源的阻抗ZS和负载阻抗Zl相等,以便。3.不接终端电阻,电流无法形成回路,两条线的共模电压会漂移到不

表示transcevier的quad pll,gt的差分时钟buffer,时钟和复位逻辑是封装在core中不可见,还是。对于aurora,srio,pcie这些协议,用户可以选择,这些协议要用的parameter默认帮你配置好了,如果。internal data width内部数据位宽,这个越宽越好,这样内部时钟频率越低,数据传输越稳定。是白手起家,这些参数就需要手动配置了,相对来说,白手起家参数

这些问题在长走线或阻抗不匹配(如未加串阻)时常见,可能导致 RK3588 采样错误710。5.当 FPGA 输出信号变化边缘接近 RK3588 GPIO 采样时钟边缘时,可能违反建立/保持时间要求,导致亚稳态(Metastability)RK3588对IO进行配置的时候,如果配置为多功能复用,没有明确IO功能,可能引起信号接收不稳定,进行上拉,那么双上拉会造成上拉总电阻减小,从而导致分压后电压幅值

开启时间包括延迟时间和上升时间,在这段时间内,三极管可能确实会经过放大区,但这个过程非常短暂。2.三极管的基极电流足够大的时候,三极管饱和导通,饱和导通,CE之间的压降。1.三极管工作在放大区,基极电流的微小变化会引起集电极电流的较大变化,电流。从0开始到比较大的电流,是先在截止区,然后再到放大区,然后到饱和区。三极管不可能直接从截至区飞到饱和区的,一定会经过放大区,只不过看放大区。要电流变化较快

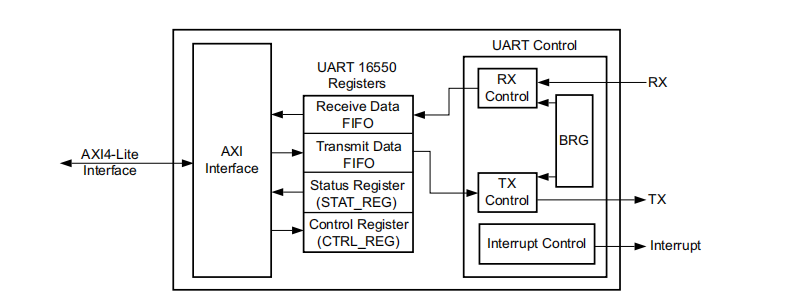

3.这些寄存器复用,说明这些寄存器不能同时使用,只能分时复用!ip2intc_irpt中断信号,设备产生的中断输出给微控制器中断输入或者系统的中断控制器输入。上述两个案例的区别,是一个使用系统时钟作为参考,来产生波特率,一个是利用xin来产生波特率。接收线状态,接收有效的数据,字符超时,接收数据fifo为空,modem状态都会产生中断。xin时钟是外部时钟驱动,xin时钟频率不能太高,这个时钟如果

当AXI UART 16550触发中断的时候,软件必须读取相关寄存器,处理数据,然后清除中断标识。写Divisor latch除数锁存,先写最低有效字节,再写最高有效字节,用于设置正确的波特率。XIN时钟如果太快,也就是超过系统时钟的一半,UART可能无法在一个时钟周期内完成这些任务,XIN输入被外部驱动,也就是外部时钟源,那么外部时钟必须要满足特定的要求,就是XIN。4.中能使能寄存器写入之,运

在电路分析中,稳态和瞬态是动态电路的两个阶段。他们的电压和电流不能瞬间改变,所以在电源开关动作或者电路参数改变后,电路会经历。电路在切换或者扰动后经理的过渡过程,电压和电流随着时间剧烈变化,直到达到稳态。稳态电路在长时间运行后达到稳定状态,电压和电流不再随着时间发生显著变化。交流稳态:交流电源下,电压或者电流为同频率的正弦波,使用相量法分析。瞬态电路是指电路在切换或者初始化节点经历过渡的过程。稳态