简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

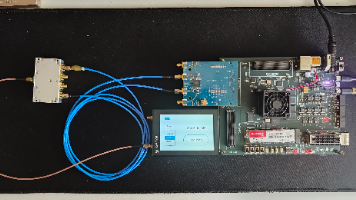

本次测试评估长款B210、短款B210、205mini以及自主研发的SDRPro这四款USRP设备的最高传输速率。测试环境为Ubuntu20.04系统,安装了UHD4.0和gnuradio等软件。测试方法是通过运行benchmark_rate命令,分别设置发射(tx_rate)和接收(rx_rate)速率为56Mbps(设备设计的最高传输速度),以检查设备的传输性能。,所有测试的USRP设备均达到

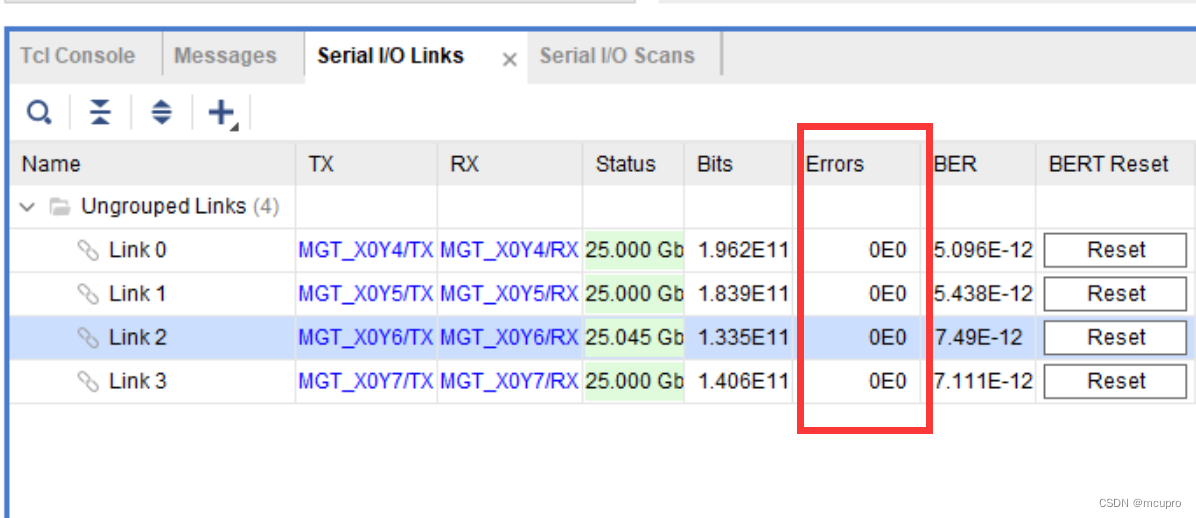

把设备插好JTAG下载器和高速口自环插口,接上电源,点击Open tar...->点击Auto Connect。根据原理图,没有串联电容时选择DC,否则选择AC,Termi...选择ACTT。点击IP Catalog->搜索 ibert->选择第一个,双击打开配置。进入时钟配置,时钟源选择QUAD128 0,配置完成点击OK即可。右键某一个通道,点击Crea...,可以打开眼图进行观察。等待bit

首次运行sudo srsran会提示缺少文件,缺少的文件在srsran_cfg文件夹中,根据提示,全部复制过去即可。修改安装脚本,修改核心数量少于或等于你的cpu核心数量,核心数越多,安装越快。使用ifconfig命令查看网络信息,找到有网络的接口,例如本设备enp111s0有网络配置,复制名称。运行成功后,使用烧写好的MIS卡,即可连接基站。安装完成后重启电脑,插入基站版,开机后运行uhd,这是

若板卡的网线与路由器等设备设备连接,而不是与电脑直接连接时,需要修改板子的IP地址。我的本地IP网段为5,所以我这里IP地址需要需要修改为192.168.5.*,IP的最后一位不要与其他设备冲突,网关需要修改为192.168.5.1。使用开发板的网口与电脑或路由器等设备连接,使开发板与电脑在同一局域网内,使用telnet工具连接开发板,进行LWIP自环测试。修改完成后编译并生成BOOT.BIN文件

首先需要使用与petalinux相同版本的vivado创建工程,与之前不同的是在创建硬件设计时需要勾选上添加bit文件,所以要在生成bit文件之后再创建硬件设计文件。打开装有对应版本的linux系统,设置petalinux的环境变量,在petalinux的安装目录中找到settings.sh,使用下面这条命令设置环境变量。8把工程文件->images->linux 下的BOOT.bin和image

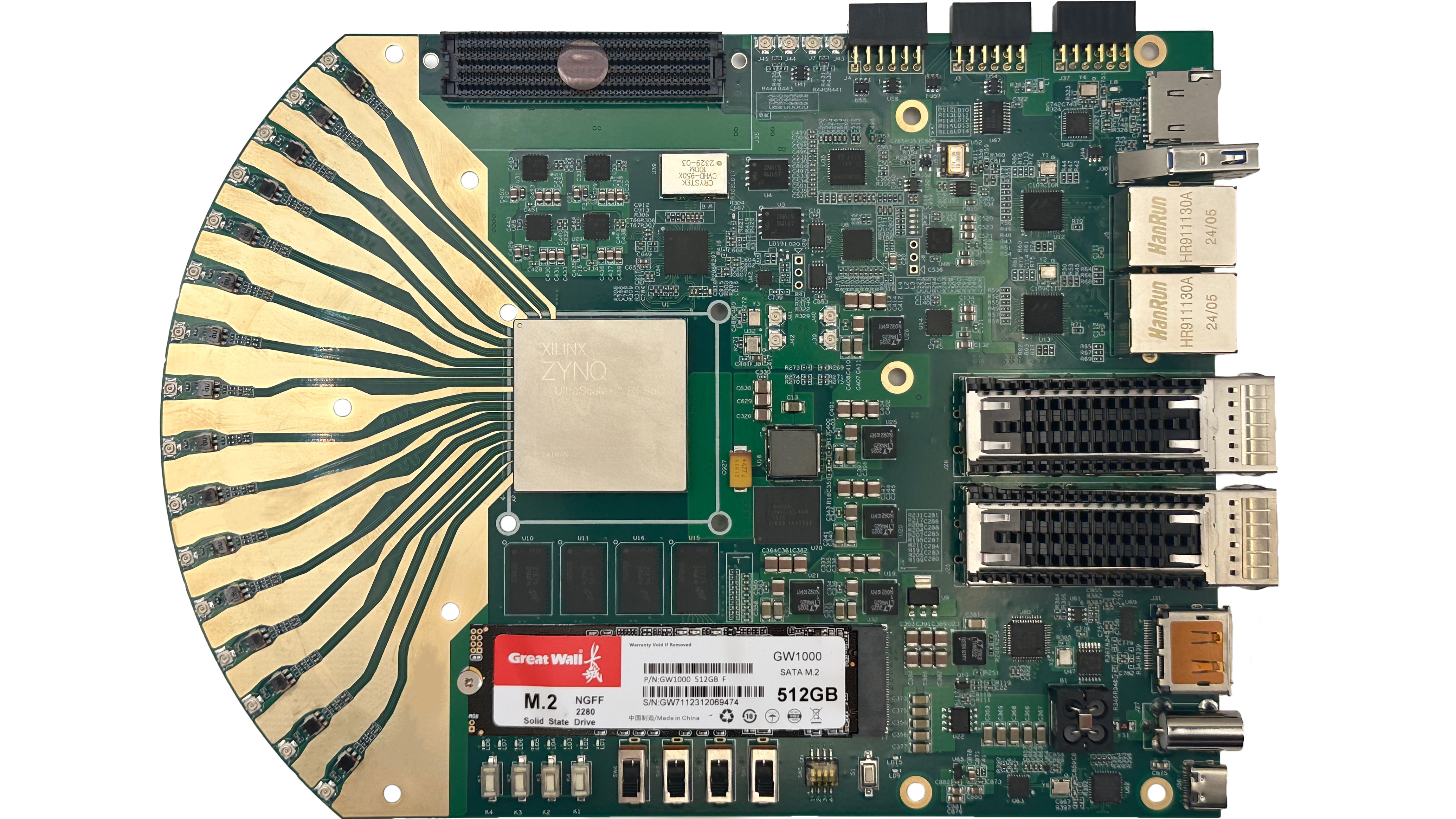

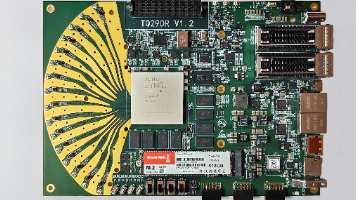

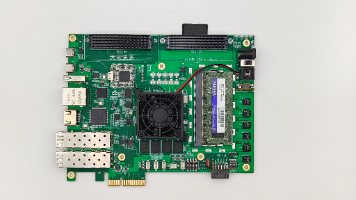

本文介绍了29DR开发板上100G光口的配置与测试方法。开发板包含两个100G光口,每个光口通过四对25G差分线实现传输,使用156.25MHz参考时钟。在Vivado中添加IBERT模块,分别配置QUAD_128和QUAD_129对应的时钟源(MGTREFCLK0和MGTREFCLK0129),生成bit文件后通过JTAG模式烧录测试。测试内容包括通道速率测量、链路自检测以及眼图分析,验证了光口

本文档是学习本开发板的基础,通过设置计数器使led0到led7依次闪烁,让用户初步认识vivado基本的开发流程以及熟悉项目的创建。本开发板的所有教程所使用的软件都是vivado2024.1版本的。可以根据网上的教程下载与安装。硬件资源此次教程使用了8个LED灯,如图1-1所示图1-1LED实物图由原理图可知,此开发板的LED灯为高电平点亮,如图1-2所示图1-2LED原理图创建项目工程首先打开软

同样在mian.c文件中可以看到一些AD9361的配置,如下图所示,可以看到收发频率在2.4G,所以后面测试时需要准备一个信号发生器,产生2.4G的频率。本例程的一些操作都是建立在前一个例程的基础上进行的,请尽量阅读完第前一个例程。打开vivado项目中的设计文件,添加观测使用的ila,开启4路输出,每一路都是32位,连接adc_fifo模块的输出,具体连接如下图所示。通过本例程的学习,我们可以实

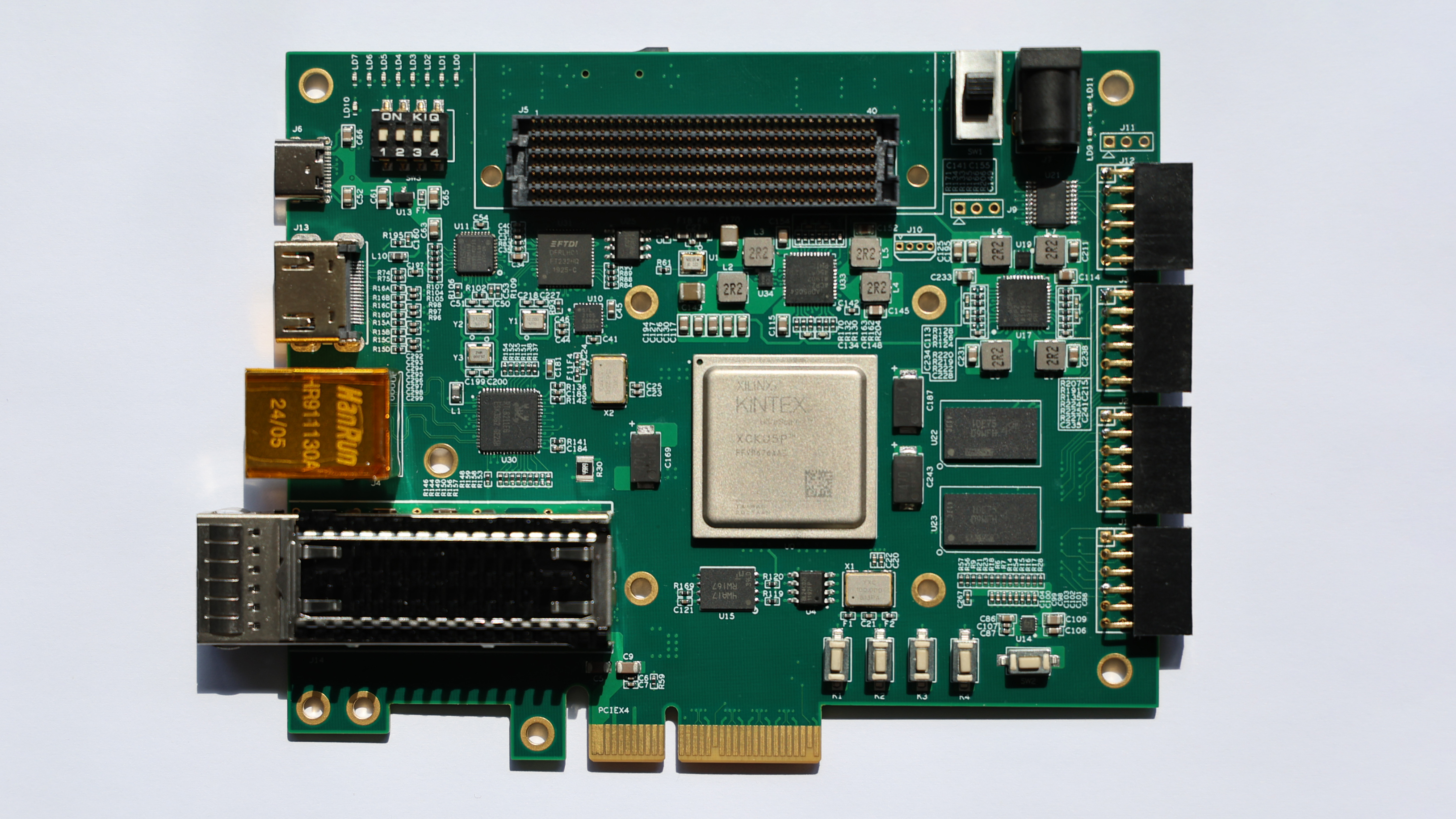

本文介绍了在Vivado中使用zc706开发板创建PCIe项目的完整流程。通过添加XDMA IP核,完成Basic、PCIe ID、PCIe BARs等关键配置,生成bit文件后配合boot_gen工具制作启动镜像。重点强调了硬件连接注意事项:主机需完全关机后插入板卡,706板卡电源开关需关闭。最终通过lspci命令成功识别到Xilinx设备,验证了PCIe通信功能。文章提供了完整的配置参数截图和

解压提供文件压缩包“adrv9026.zip”,解压后有三个文件夹,首先是“hdl-2023_R2”为vivado端的项目,里面有各种射频子板加不同底板的项目,本例程使用的是ZCU102的项目修改出来的。此项目是我们已经修改完成并编译完成,打开bd文件,本项目的设计如下图所示。压缩包中的“boot_gen”文件夹为生成BOOT.BIN文件的工具,将前两步生成的“system_top.bit”文件与