简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

凌晨三点的显示器还亮着,我盯着仿真界面里反复撞马路牙子的车辆模型,咖啡杯在桌上敲出焦虑的节奏。平行泊车的路径跟踪就像在跳探戈——既要紧跟舞伴的节奏,又不能踩到对方的脚。传统的PID控制器在这里笨拙得像头熊,是时候请出两位新搭档了:MPC(模型预测控制)和纯跟踪算法。控制算法的精妙之处在于,既要有数学家般的严谨,又要具备街头智慧——有时候,解决路径震荡的最佳方案,可能就是在代码里偷偷加个0.95的衰

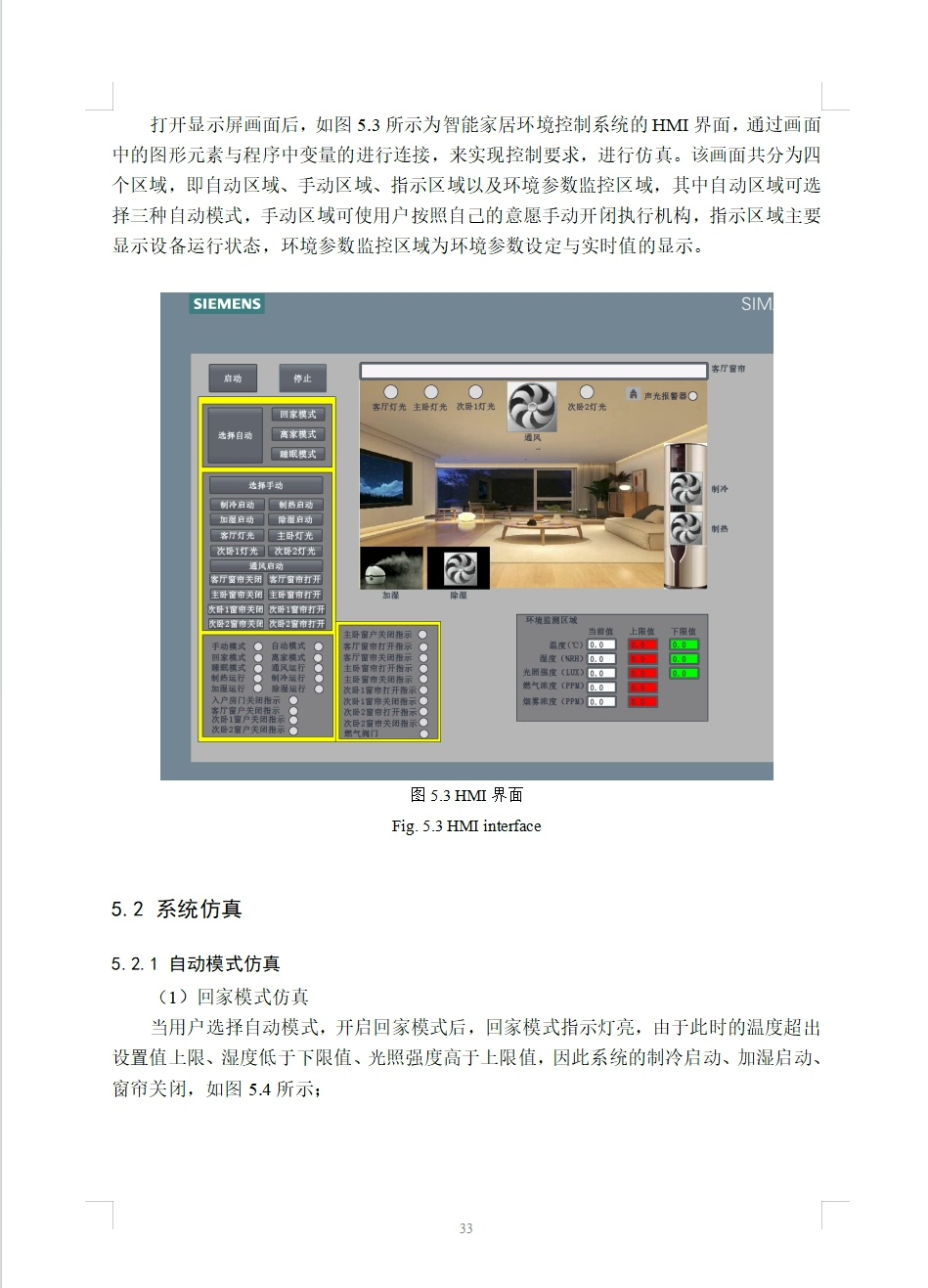

基于PLC的智能家居环境控制系统设计清晨6:30,窗帘自动拉开15度,加湿器开始吐出第一缕白雾。此时厨房的咖啡机突然抽风似的疯狂震动——别误会,这不是什么灵异事件,只是某位程序员用PLC(可编程逻辑控制器)搞的智能家居系统在耍宝。

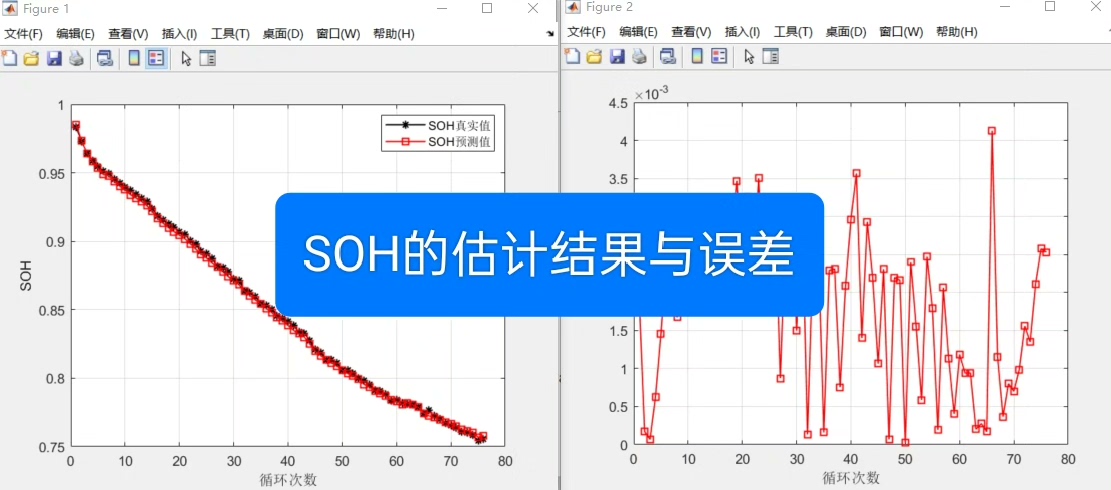

牛津数据集包含8 枚 740 mAh 的 LiCoO2/Graphite 18650 电池,在 40 °C 恒温箱内循环执行“1 C 恒流恒压充电 + 1 C 恒流放电”老化实验,每 100 循环插入一次性能测试(HPPC + 容量标定)。本案例以“牛津锂离子电池老化数据集(Oxford Battery Degradation Dataset)”为蓝本,给出一条从原始二进制结构→可训练特征→LST

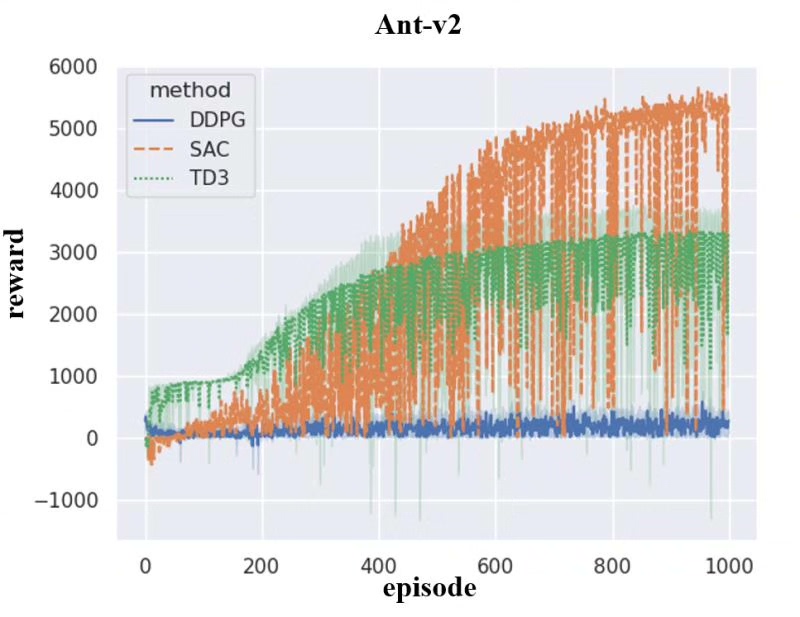

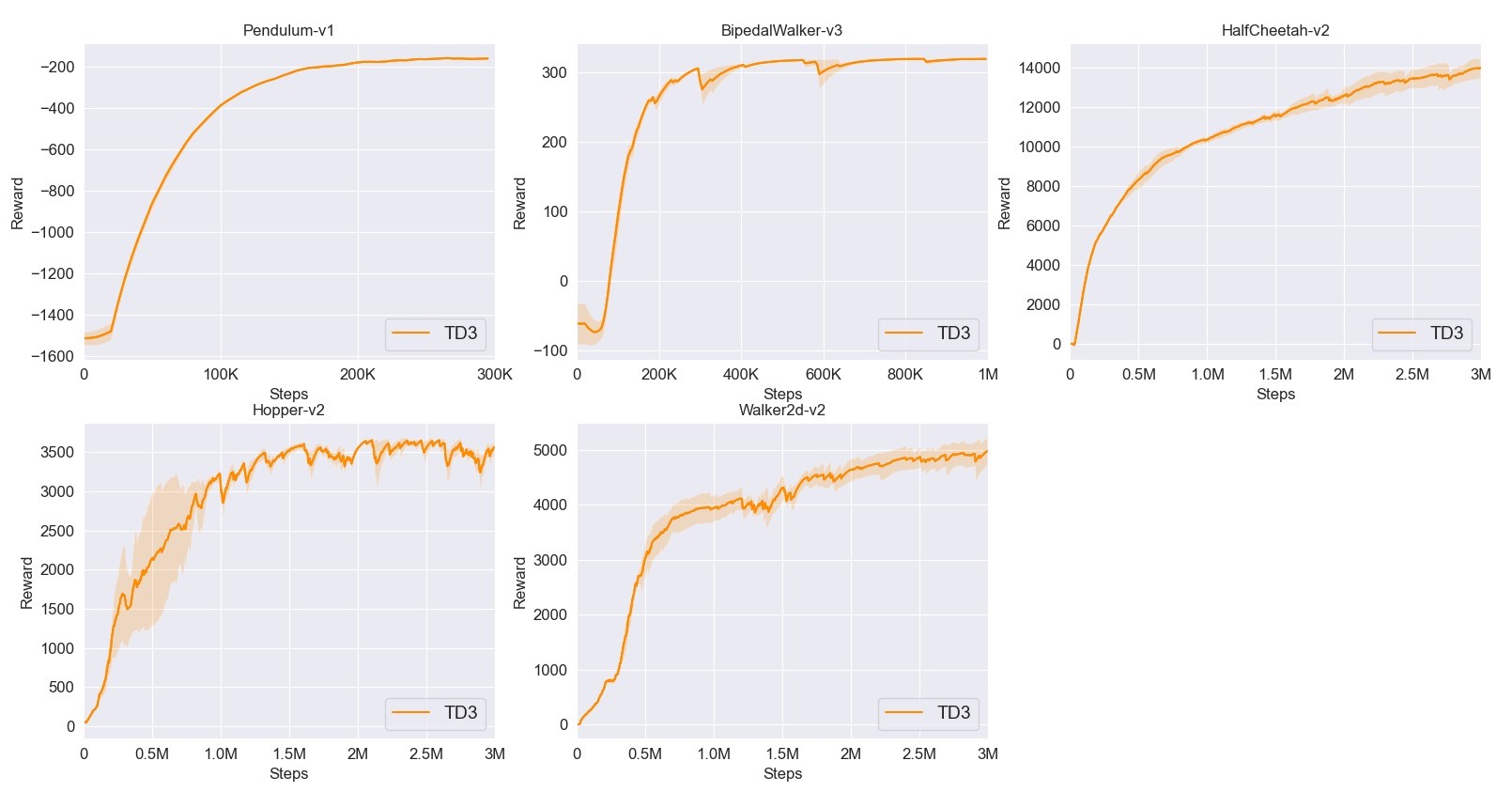

深度强化学习算法:DDPG TD3 SAC实验环境:机器人MuJoCo本文针对在 MuJoCo 的 HalfCheetah-v2 环境中实现的四种深度强化学习算法进行全面分析,包括 A3C、DDPG、SAC 和 TD3。这些算法代表了现代深度强化学习在连续控制任务中的主要技术路线。

层定义,输入为 1 维振动信号,输出 32 通道特征。conv2_1(5×1)、conv2_2(7×1)、conv2_3(9×1),并行提取不同尺度特征。,分别作用于多尺度特征和融合后特征。,输出 10 类故障概率。前向传播逻辑# 宽卷积层特征提取# 多尺度特征提取(三条并行支路)# 特征融合 + ECA注意力加权# 分类三条并行支路分别处理不同尺度卷积,通过torch.cat拼接特征,经 ECA

这9种DRL算法涵盖了基于策略梯度、基于价值以及二者结合的多种方法,对于强化学习初学者来说,是非常好的学习资源。通过实践这些算法,你能深入理解强化学习的核心概念,掌握使用Pytorch进行强化学习算法开发的技能。赶紧动手试试吧!

本系统通过模块化设计,实现了微网P2P能源交易的仿真与智能决策。微网环境模块精准模拟了能源生产、负荷消耗和交易规则,为强化学习提供了高保真的交互场景;三种强化学习算法覆盖了不同复杂度和应用场景,支持性能对比与选择;工具支撑模块则简化了训练流程、实验管理和结果分析。系统可用于研究强化学习在能源交易中的应用效果,为微网运营商提供决策支持,也可作为学术研究的基础框架,支持进一步的算法优化和场景扩展。通过

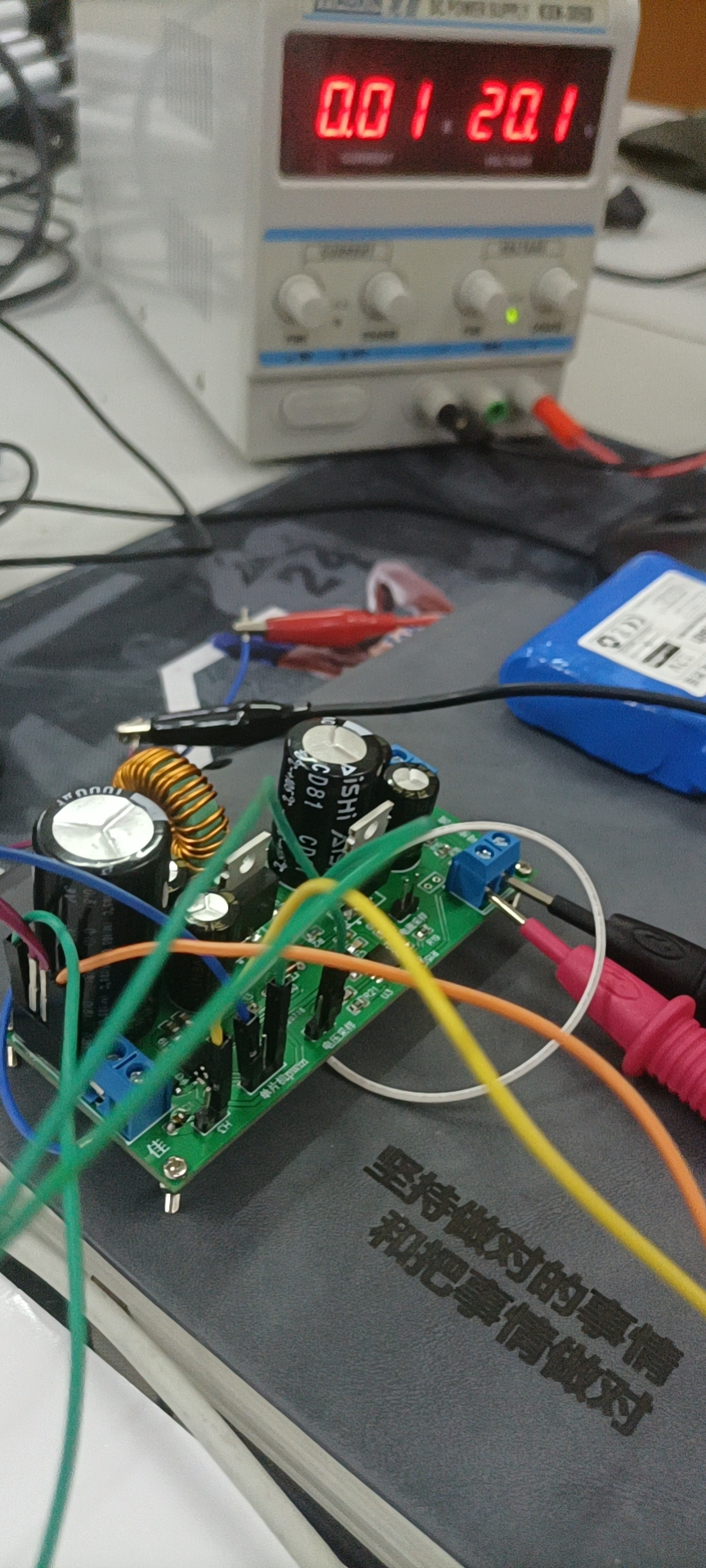

主电路用NRF540N这对MOS管做同步整流,这货的Rds(on)只有44mΩ,实测开关损耗比普通二极管方案低30%不止。驱动部分用IR2104搭的半桥驱动,注意这里有个骚操作——自举电容用了0.1μF陶瓷电容并联10Ω电阻,实测驱动波形上升沿控制在20ns以内。重点在死区时间设置,IR2104的典型传播延迟是520ns,这里设置63个时钟周期(按72MHz算约0.875us),实测上下管没有直通

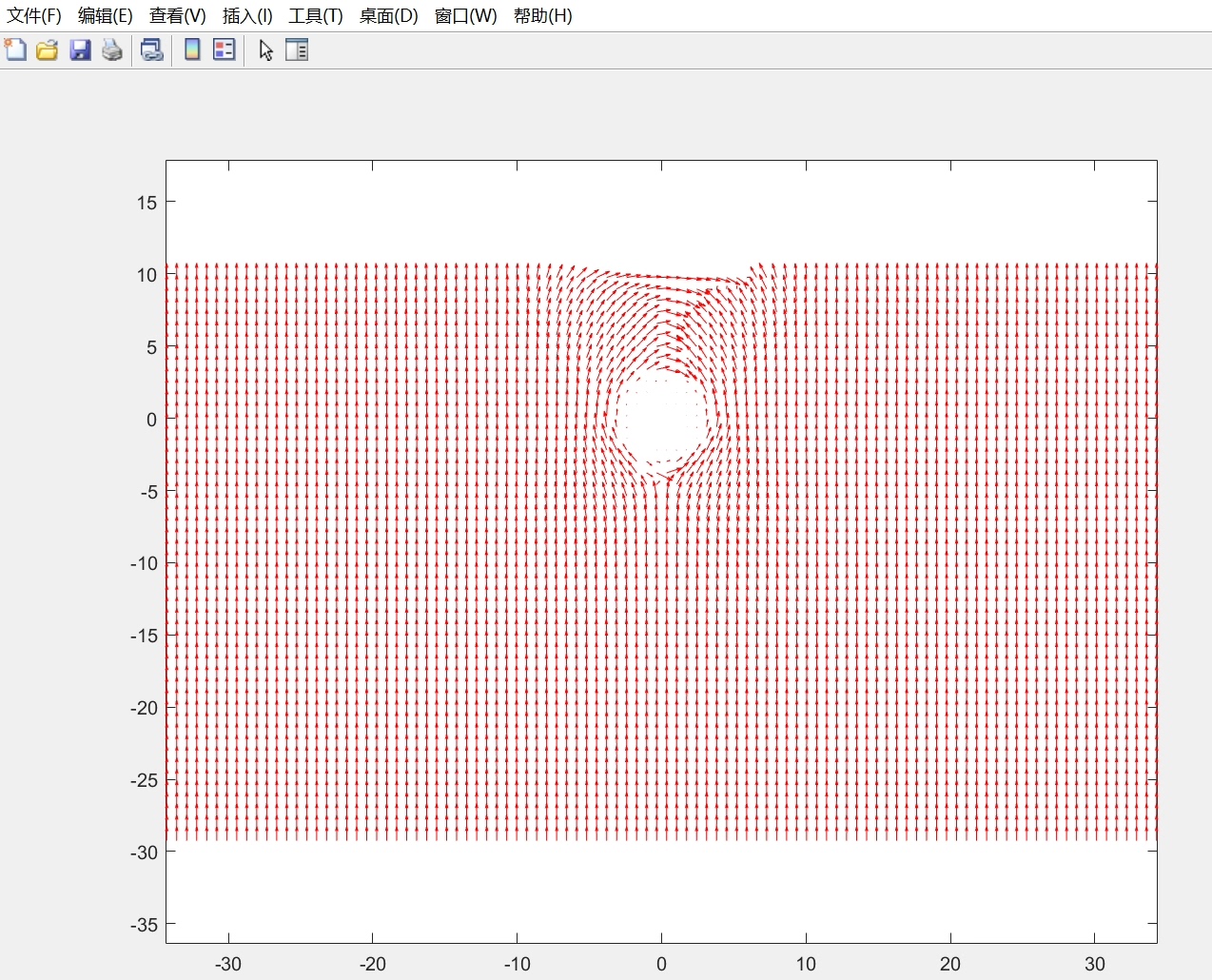

在岩土工程数值模拟后处理中,三维主应力方向可视化是个挺有意思的活。今天咱们直接上手实操,用FLAC3D7.0的Fish语言配合Matlab整一套主应力方向可视化方案。遇到过实际案例:某边坡模型导出的方向向量在坡脚处呈现放射状分布,通过颜色映射发现最大主应力方向与滑裂面走向高度吻合。注意FLAC3D里的应力方向是全局坐标系下的,记得坐标系转换这事咱们后面再说。使用fish将单元体的三个主应力方向数据

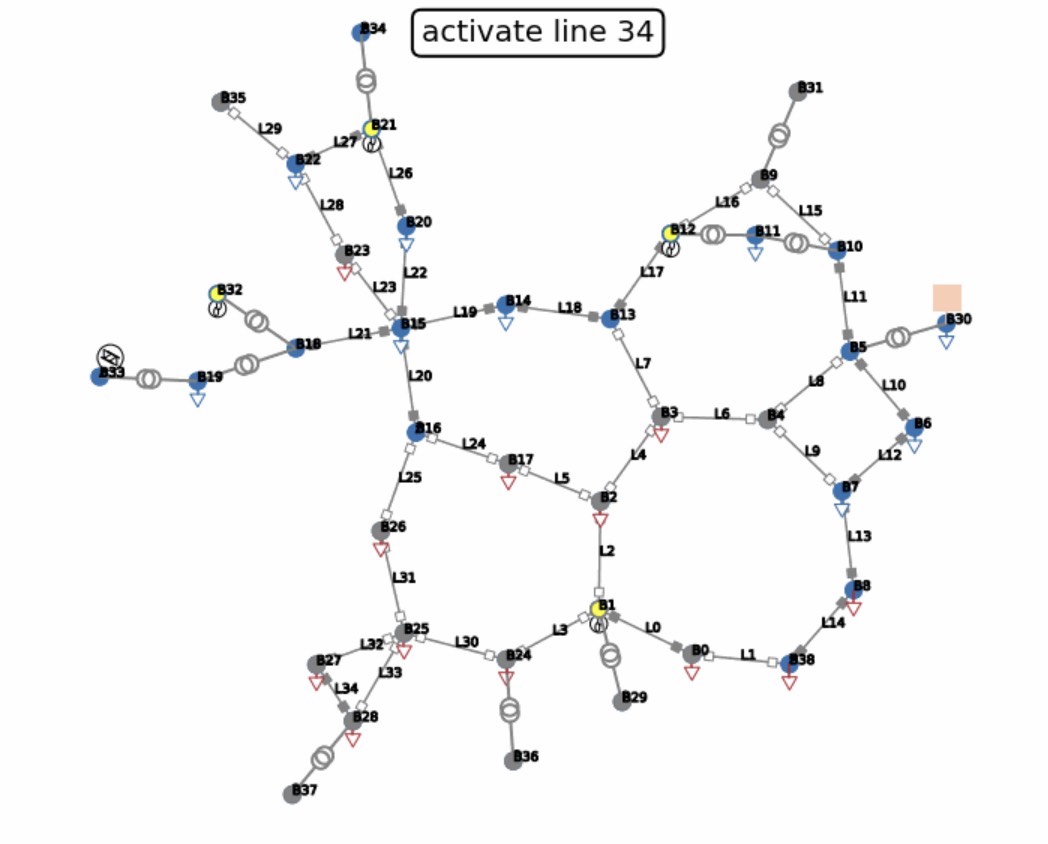

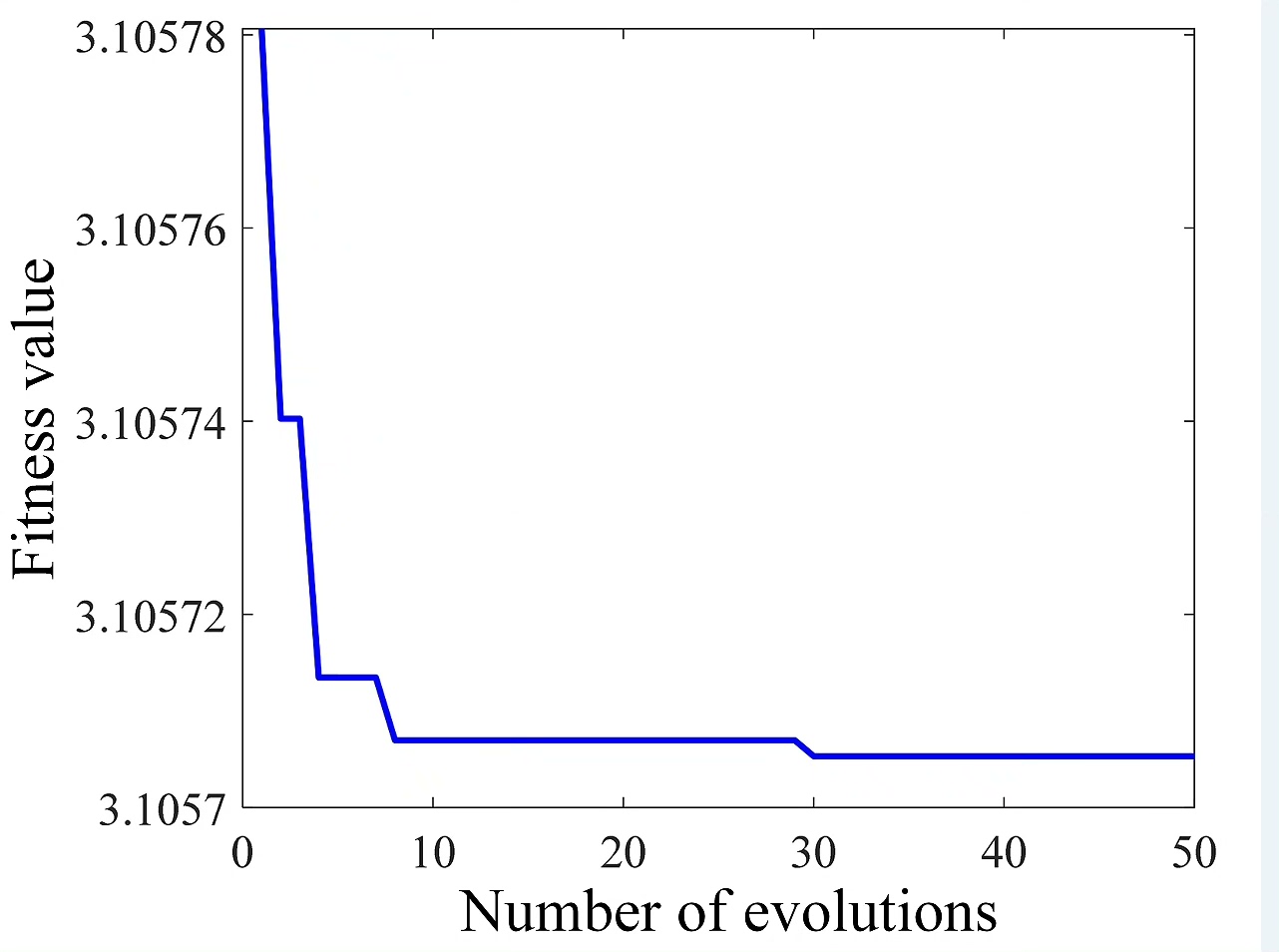

利用可再生能源进行电力系统恢复-DRL做法目标是开发 DRL 技术,该技术可以计算可再生能源比例较高的电力系统的恢复序列环境的初始状态模拟了大规模停电后电力系统的耗尽状态代理的任务是恢复所有负载的服务如果天气条件适宜,可再生能源发电机可用作黑启动资源,前提是启动电力由储能装置或电网提供可再生能源发电机的电力输出由获得的实际天气数据中随机选择的时间点决定,这些数据适用于附近的风能/太阳能发电厂mat