简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

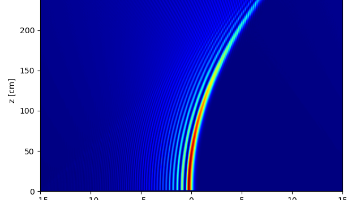

摘要:LightPipes实现了基于Airy函数的一维和二维Airy光束模型。一维Airy光束光场分布为F(x)=Ai(x/x0)e^(ax),传播时呈现弯曲特性;二维Airy光束在x和y方向均服从Airy函数分布F(x,y)=Ai(x/x0)Ai(y/y0)e^(a1x+a2y)。文章通过Python代码示例展示了两种光束的生成和传播特性,并给出了相应的光强分布图。AiryBeam1D和Airy

本文介绍了使用Git进行团队协作开发时的冲突处理流程。首先演示了如何初始化Git仓库、创建裸库并开启Git服务供局域网共享。随后重点讲解了两种常见冲突场景:空文件冲突和内容冲突。在空文件冲突中,Git会自动合并不同版本;而在内容冲突时,需要手动修改冲突标记并提交合并结果。文章详细展示了冲突解决的具体操作步骤,包括拉取更新、识别冲突标记、手动修改文件以及最终提交合并结果的过程。最后验证了冲突解决后代

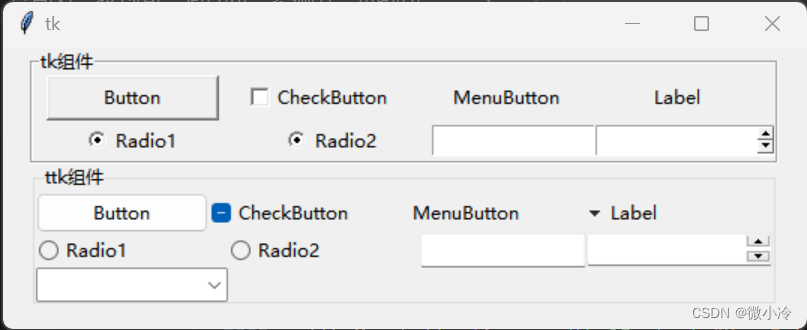

python的开发效率极高,也体现在窗口程序设计上

本文推荐8个无需注册、无套路的主流网盘搜索工具(截至2025年6月)。包含学霸盘、小白盘等百度网盘专用搜索,以及兄弟盘、混合盘等支持多平台的聚合搜索。各网站对比显示,学霸盘、口袋云等支持时间排序/资源大小筛选,多数提供直达链接。其中兄弟盘覆盖阿里/夸克/迅雷等7种网盘,1号线报支持6种网盘资源。这些工具普遍无强制关注要求,部分网站含广告。

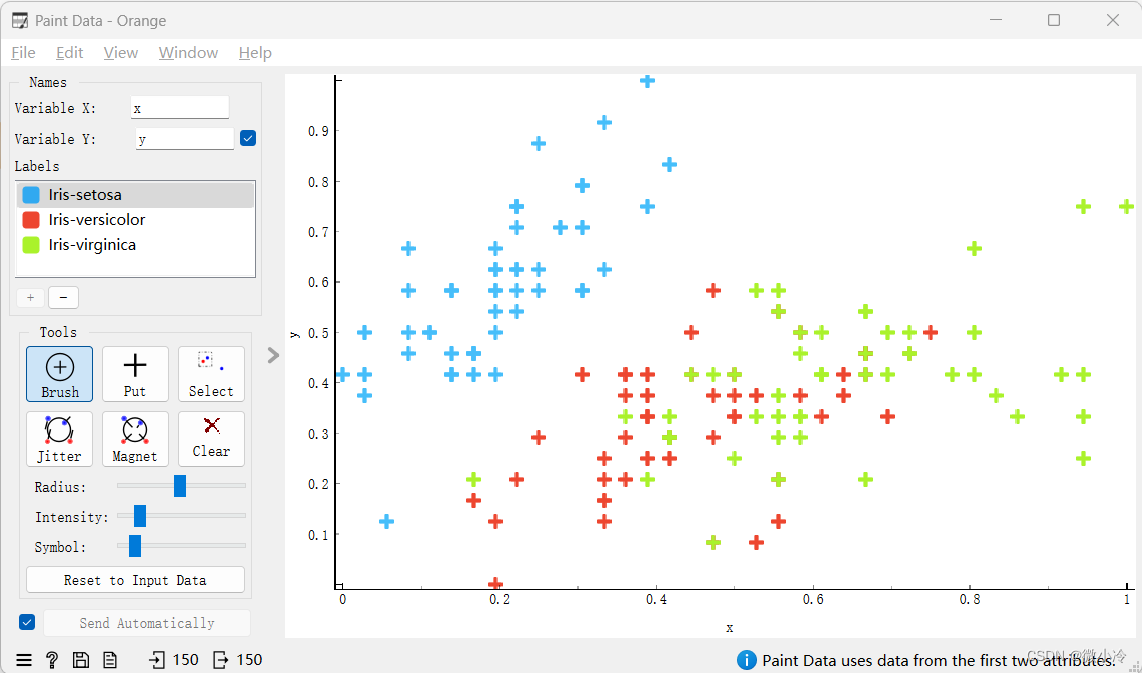

介绍数据挖掘工具Orange从安装到初步使用的基本流程

光的颜色与其说颜色是光的一种属性,不如说是人眼对可见光频率范围内的一种感应,是人眼的一种属性。而人眼对光频的感应包括三个方面,即明度、色调和饱和度。其中,明度与光强有关色调反应的是光的频率信息饱和度表示图像上的颜色与光谱色的接近程度当不考虑色调、饱和度为0的时候,只考虑明度,则色彩感消失,就是所谓的黑白图像,或者更严格地说是灰度图像。色调与饱和度虽然反应色光的频率信息,但表现的是...

tkinter中共有16个核心部件,ttk中也有16种,二者都有的组件有有四大按钮:Button, Checkbutton, Menubutton, Radiobutton;三个框架:Frame, LabelFrame, PanedWindow;以及输入框Entry,标签Label,刻度条Scale,滚动条Scrollbar 和数字框Spinbox。tkinter独有的控件有多行文本Text;消息

IOPaint是一款开源的图像修复工具,只需简单涂抹,便可以编辑图片,从而实现图像抹除、对象替换等功能,可以实现下面的涂抹效果。

Power Mode除了华丽之外,其实还有一个意想不到的功能,即用一种十分夸张的方式提醒你代码已经更改了,对于手贱的人来说可以省掉许多麻烦。

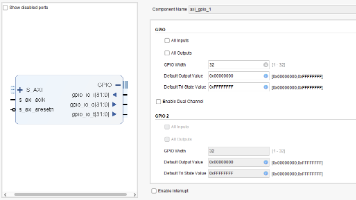

本文介绍了AXI GPIO接口的硬件配置与软件编程方法。硬件部分说明了GPIO核的信号接口功能,包括输入/输出信号、三态控制及各项参数设置(如位宽、默认值、中断使能等)。软件部分重点讲解了xgpio.h提供的GPIO操作函数,包括初始化(XGpio_Initialize)、方向设置(XGpio_SetDataDirection)、数据读写(XGpio_DiscreteWrite/Read)等,并详