简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

这里说的 “三级引导” 并不是一个固定的、标准的术语,而是想强调,在某些系统里,bootloader 可以再拆得更细,例如。BootROM 不是严格意义上“只能从 ROM 启动操作系统” 的意思,而是指芯片上电复位后,第一段固定的启动程序,通常固化在 ROM(只读存储器)或 mask ROM、OTP ROM,甚至是 eFuse 或者内嵌 Flash 中。可以是单级的,也可以是多级分层的。对 Arm

现在这个云时代,云计算渗入我们生活的方方面面。也许你正在使用云服务。但只是你不知道而已。

在数据传输的同时,主设备可以在下一时钟周期内发起新的地址阶段请求,从而实现地址与数据的重叠传输。为了提高总线的整体传输效率,AMBA AHB 总线协议引入了 突发传输(Burst Transfer) 机制,使得多个连续地址的数据可以在一次地址阶段后连续传输,从而显著减少地址译码的开销并提升带宽利用率。在基本的单次传输模式中,每次传输都需要先进行地址阶段和从设备选择阶段,因此在每笔数据传输前都会产生

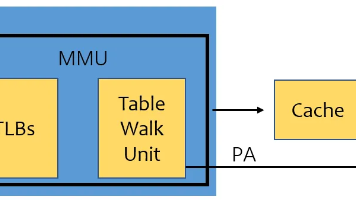

上面提到的数据拆分,其实只是设备驱动层面的操作——驱动会根据硬件的 DMA 传输能力、物理地址的连续性以及应用层传入的缓冲区特征,将一次用户请求拆分成若干个物理上连续的片段(segment)。看到这里,我们就会发现,在有 IOMMU 的前提下,DMA 传输数据需要的源地址、目的地址发生了本质变化,不再是需要连续的物理地址了。从这里就可以发现,有了 IOMMU 之后,实际上,DMA 的源地址、目的地

两个进程的总 CPU 利用率为 (25/50)+(35/80)=0.94,因此似乎合乎逻辑的结论是:这两个进程可以被调度,并且仍让 CPU 有 6% 的可用时间。如果我们按执行与周期的比率 ti/ρi 测量一个进程的 CPU 利用率,那么 P1 的 CPU 利用率 20/50 = 0.40,P2 的是 35/100 = 0.35,总的 CPU 利用率为 75%。尽管是最优的,然而单调速率调度有一个

多数底层优化机制(如乱序执行、推测执行、多发射等)对软件开发者而言是透明的,无需显式关注;然而,部分优化会对程序行为产生可观察影响。为保障正确性,体系结构也提供了如内存屏障等机制,使开发者可以显式控制这些影响。当然这里也包括ARM 学习笔记(三)中所讲的内存类型。阅读到这里,建议再看一下ARM 架构下 cache 一致性问题整理一文,可能会有不一样的体会。

参考文献:《ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition》

参考文献:《ARM ArchitectureReference Manual ARMv7-A and ARMv7-R edition》

总结一句话,intptr_tuintptr_r变量类型用于跨平台的情况下,不同机器字长(16位、32位、64位)整数与指针相互转移的的通用性。通常情况下,编译器内部都会提供intptr_t等定义。如果编译器没有提供,则标准库会根据架构用 typedef 自己定义。

regulator 框架是 Linux 内核中用于管理电压和电流调节器(如 LDO、DCDC 转换器等)的一个子系统。它提供了一个抽象层,使得驱动程序和内核的其他部分可以以一致的方式与调节器进行交互,而无需了解底层硬件的细节。控制电压的启停调整输出电压查询当前电压状态保护系统不受过流或过压的影响以上两种方式,regulator driver 可以根据实际情况,选择一种实现方式。