简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

DFT相关的mem repair概念通过DFT检测出某些mem单元读写错误(芯片制造出来之后有随机问题,电路错误或者性能达不到),此时可以通过一些规则和算法用mem中原本富余的逻辑来替换这部分单元...

1.DVFS 即动态电压频率调整。动态技术则是根据芯片所运行的应用程序对计算能力的不同需要,动态调节芯片的运行频率和电压(对于同一芯片,频率越高,需要的电压也越高),从而达到节能的目的。参考https://blog.csdn.net/weixin_42749767/article/details/829867372.power domains means, power on-off,...

c++的virtual function实现原理和systemVerilog的virtual function/task实现很相似除了下面的一篇文章还可以参考【C++拾遗】 从内存布局看C++虚继承的实现原理https://blog.csdn.net/xiejingfa/article/details/48028491咱们知道,与C语言相比,C++在布局和存取时间上的额外开销主要是由虚函数(vir

作者戴金艳,公众号:计算机视觉life, 编辑部成员. 更好的阅读体验请看首发原文链接图像拼接是将同一场景的多个重叠图像拼接成较大的图像的一种方法,在医学成像、计算机视觉、卫星数据、军事目标自动识别等领域具有重要意义。图像拼接的输出是两个输入图像的并集。:在所有输入图像中检测特征点:建立了图像之间的几何对应关系,使它们可以在一个共同的参照系中进行变换、比较和分析。大致可以分为以下几个类直接使用图像

嵌入式系统的各种常见外设

要支持大规模的网络,就必须有性能最好,端口密度最大的汇聚层核心层设备,这样的设备成本高,不是所有企业都买得起,且必须在建设网络时就预先规划好网络规模,在网络规模小时,会造成资源的浪费,在网络规模继续扩大时,扩容也比较困难,因而让企事业单位陷入了成本和可扩展性的两难选择之中。而又因为每台叶交换机都需要连接到脊交换机,因此脊交换机的端口密度取决于拓扑结构中叶交换机的最大数量,同时,网络中的脊交换机的数

转自http://www.elecfans.com/d/652288.html在Coarse Placement和Legalization之间,其实还有很重要的一个步骤, 就是对ScanChain(扫描链)的处理。英文名Scan Reorder,直译为扫描链重组。那讲Scan Reorder之前,有必要对Scan Chain的基本知识做一定普及。Scan chain其实是可测试性设计(D...

Scribe line(划片道,又称 dicing street、切割道)是晶圆上相邻两颗芯片(die)之间的窄条区域,专门留给砂轮或激光切割使用,把整片晶圆分割成单颗芯片。宽度:通常,由封装厂和刀片尺寸决定。位置:die 四周一圈,与芯片边缘平行,内部不画任何功能电路。功能:提供机械切割路径,避免切到芯片;容纳测试结构(PCM、WAT test key),用于监控工艺均匀性;可放置对准标记、du

2.随着ADAS和娱乐信息系统的飞速发展,车载ECU需要处理越来越多的数据(交通标志,高精地图,个性化,多媒体等数据),同时对ECU的运算能力也有了更高的要求,传统的ECU已经不能满足日益增长的数据处理和运算能力的需求。简单来说就是把功能相近的多个传统ECU,集中到一个算力和资源都很强大的控制器里,这个控制器被称为域控制器,所以这里的域指的是功能域。常见的域控制器有:动力总成域控制器,车身域控制器

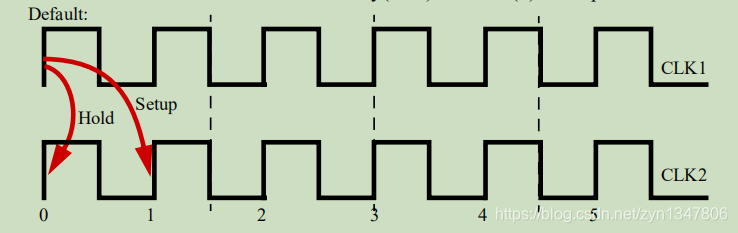

seup or hold和start or end时钟的对应关系如下版权声明:本文为CSDN博主「进击的芯片」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/zyn1347806/article/details/97659093。