简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

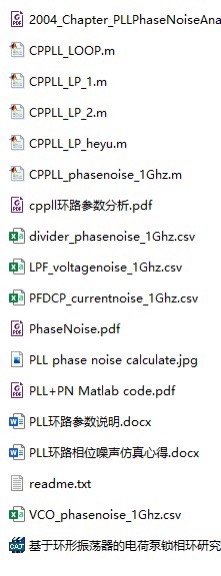

这套 MATLAB 代码集主要用于电荷泵锁相环的设计与仿真,包含五个核心文件,分别处理环路参数计算、相位裕度优化、滤波器设计以及相位噪声分析等关键任务。代码采用系统化的方法,从基础理论出发,逐步构建完整的锁相环模型。

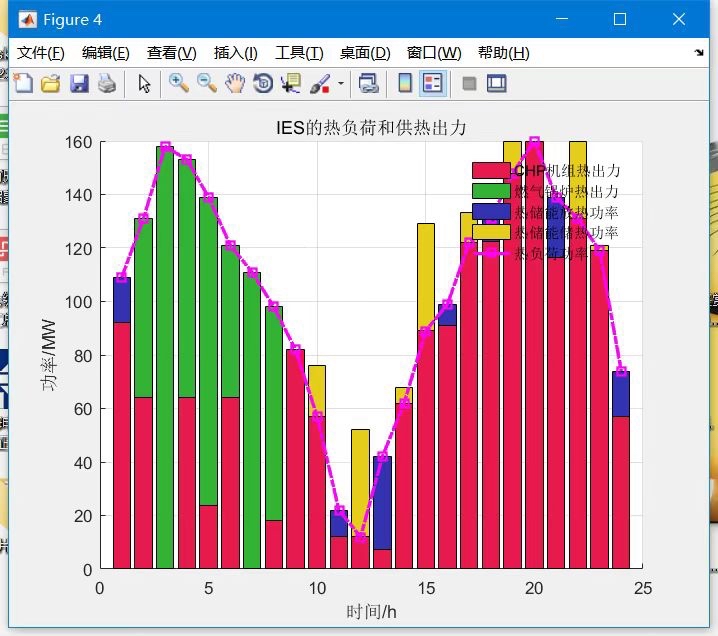

本文分析的是一个基于阶梯碳交易成本的综合能源系统优化调度模型,该系统创新性地集成了电转气(P2G)与碳捕集(CCS)技术,通过Matlab平台结合Yalmip建模工具和Cplex求解器实现。该模型旨在实现能源系统的低碳经济调度,平衡能源供应与环境保护的双重目标。

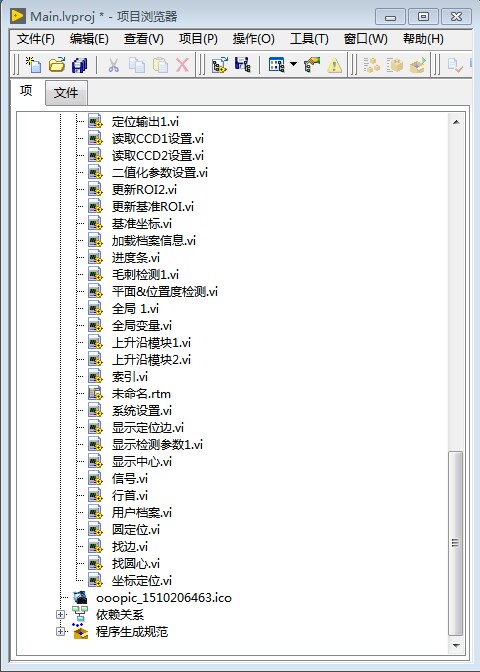

通过LabVIEW与HALCON的结合,我们可以轻松实现一个功能强大的视觉检测系统。这个系统不仅能够支持单相机和双相机两种模式,还能够实现边缘检测、圆检测和模板匹配等核心功能。整个系统的实现过程相对简单,但由于HALCON的强大功能,系统的稳定性和准确性都非常不错。未来,我可能会继续探索如何利用HALCON的更多高级功能,比如多模板匹配、基于AI的改进算法等,进一步提升系统的性能和适应性。

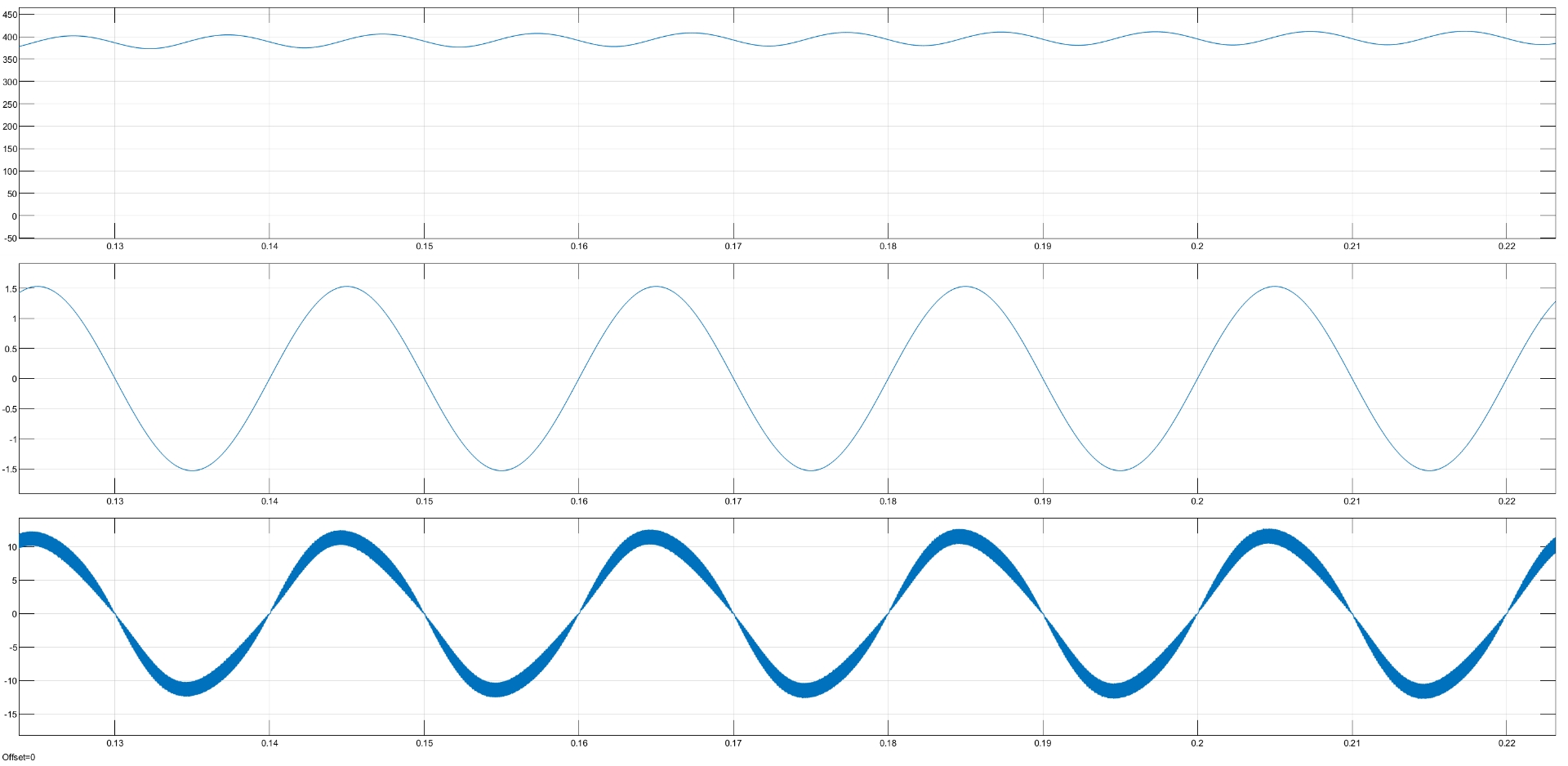

图腾柱无桥PFC,平均电流控制。环路建模然后设计出电压环和电流环补偿网络,零极点放置。PLECS、psim和simulink均验证过,均有对应模型。同时Dual-boostPFC及两相、三相交错并联图腾柱PFC均有。最近在电源领域研究,遇到了图腾柱无桥PFC这个有趣的技术,跟大家分享下我的心得。

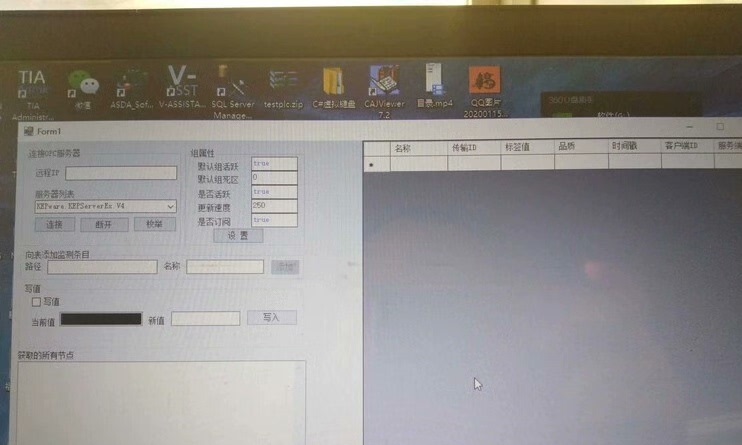

本系统基于C#语言开发,采用OPC(OLE for Process Control)技术实现与PLC(可编程逻辑控制器)的通信,构建了一套完整的工业数据采集与监控上位机解决方案。系统分为两大核心模块:基础OPC测试工具(OPCTest)与实际工业数据采集系统(Dayun),支持OPC服务器连接、数据读写、实时监控、历史数据存储与查询等功能,适用于电机驱动设备的性能测试与数据管理场景。

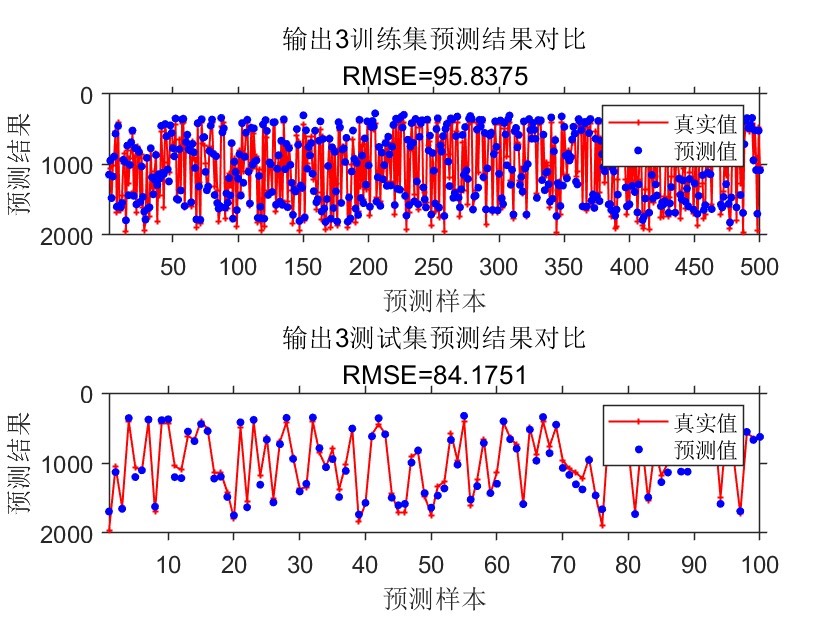

该实现提供了一个结构清晰、评估全面的 LSTM 多输入多输出预测框架。其设计兼顾工程实用性与学术严谨性,不仅适用于快速原型验证,也为后续深度优化奠定了坚实基础。开发者可根据具体任务需求,在数据预处理、网络结构或训练策略层面进行针对性改进,以获得更优的预测性能。LSTM长短期记忆神经网络多输入多输出预测(Matlab)所有程序经过验证,保证有效运行。1.data为数据集,10个输入特征,3个输出变量

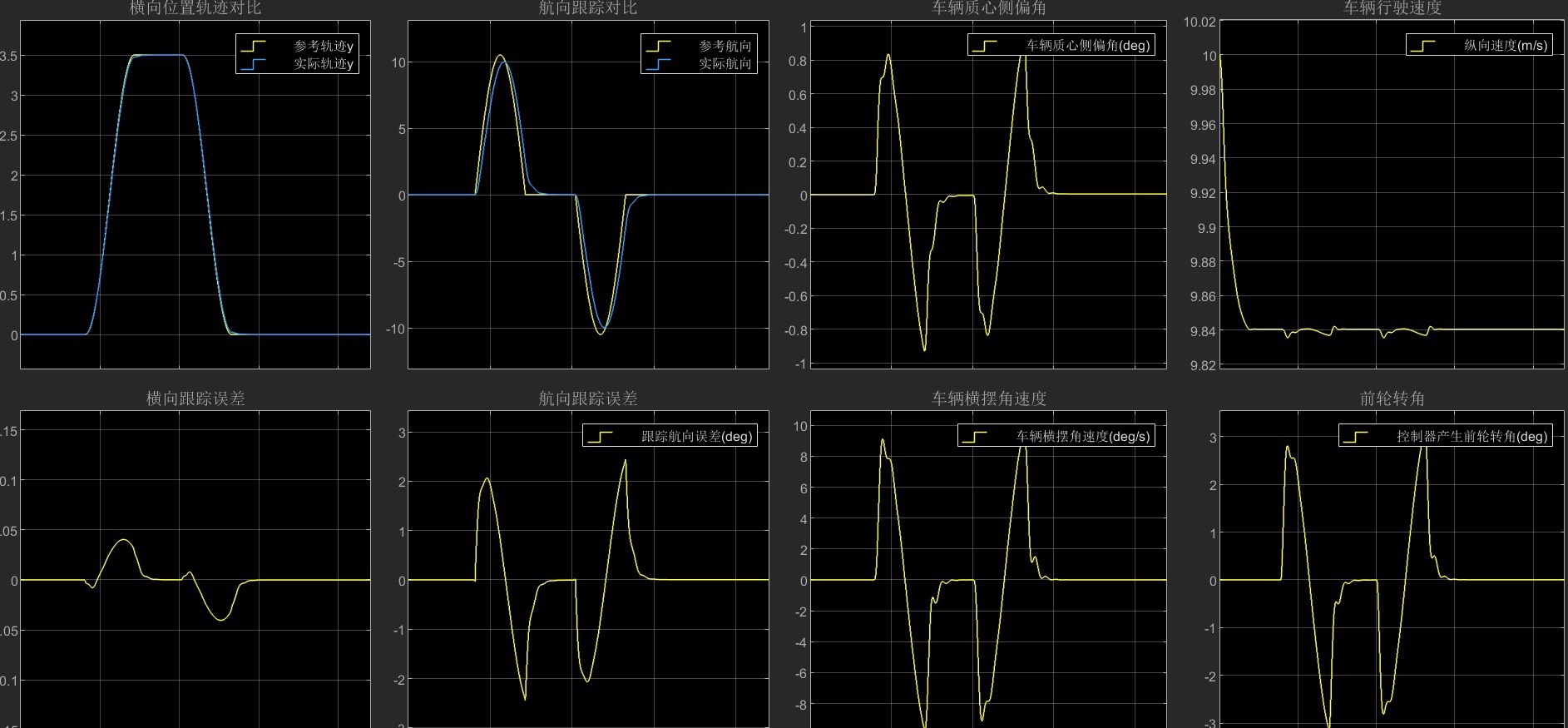

基于变时域(Np)的MPC(模型预测控制)的超车路径规划控制Carsim是8.1版本。有安装教程内附有相关论文可进行参考在自动驾驶领域,超车路径规划控制是一个关键且极具挑战的任务。今天咱就唠唠基于变时域(Np)的MPC(模型预测控制)在这方面的应用,顺便还会提及8.1版本的Carsim,以及给大家分享下安装教程,文末附上参考论文,方便大家深入研究。

该项目是一个典型的高压输电线静电场仿真,通过参数化扫描模拟三相交流电的电场变化,输出地面电场分布云图、沿线场强曲线和最大场强数据,适用于工程设计和电磁环境评估。Maxwell电场仿真高压输电线地面电场仿真,下图分别为模型电场强度分布云图、各时刻沿地面电场强度分布,地面各点最大场强。

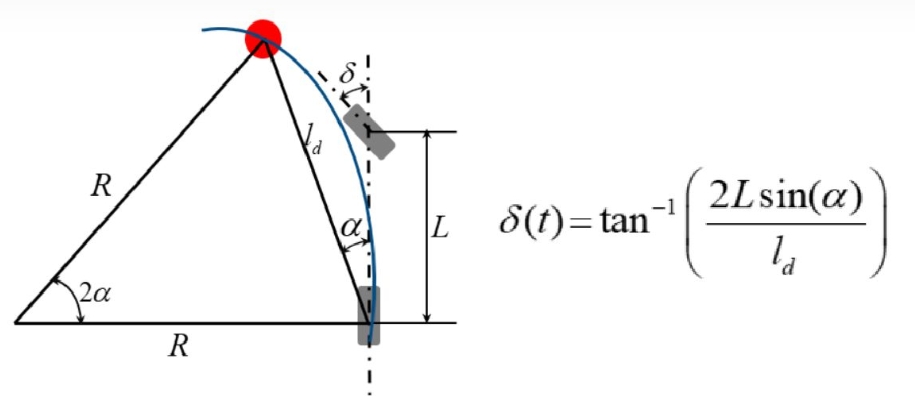

(工程项目线上支持)预瞄跟踪控制算法,单点或多点驾驶员模型,横制,纯跟踪算法。carsim和MATLAB Simulink联合仿真。附建模说明书在工程项目的线上支持领域,汽车控制算法的优化与验证至关重要。今天咱就唠唠预瞄跟踪控制算法、单点或多点驾驶员模型、横制以及纯跟踪算法,顺便讲讲基于 Carsim 和 MATLAB Simulink 的联合仿真,再附上建模说明书,让大家有个全面的了解。

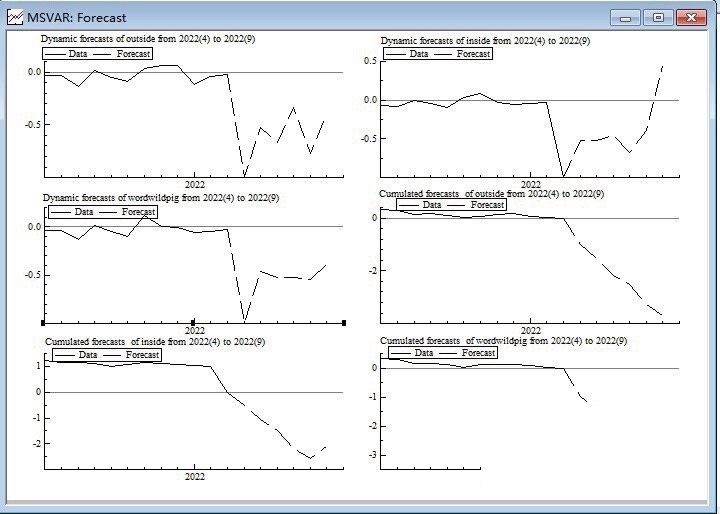

马尔科夫区制转移向量自回归模型,MSVAR模型,MS-VAR模型的GiveWin软件安装和操作过程+MS-VAR各种图形制作(区制转换图、脉冲图、模型预测图和模型预测结果等等)+最优区制数和模型形式判断(MSI-VAR、MSM-VAR模型形式的最优选择问题,这是该模型的核心问题)。文档一共分为五部分,一是软件的安装(已打包软件,按照操作步骤进行没啥问题);二是数据的导入;三是软件操作过程;四是图形