简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

SDC命令详解当使用set_ideal_network命令将当前设计中的一组端口或引脚标记为理想网络源后,理想属性会沿着组合逻辑进行传播,理想网络中的线网和单元的延迟默认为0,可以通过set_ideal_latency命令指定理想网络的延迟(设置了理想网络对象的ideal_latency_max_rise、ideal_latency_max_fall、ideal_latency_max_rise、

Design Compiler的综合策略大致可以分为三种:一种是自上而下(Top-Down),即一次性读入整个顶层设计及所有子模块,应用顶层约束,然后统一综合,这适合设计规模较小或计算资源充足时;一种是自下而上(Bottom-Up),即各个子模块单独约束、单独综合,最后再综合顶层设计,这适合超大设计或受到内存限制时;两种策略的结合是一种更常见的综合方法。

本文将对Power Compiler功耗分析时考虑的三种功耗(漏电功耗、内部功耗、切换功耗),及它们的计算方式(NLPM)进行详细介绍。

传播时钟是在进行了时钟树综合后,使用set_propagated_clock命令可以将一个理想时钟转换为传播时钟(注意,虚拟时钟即无时钟源对象的时钟无法被转换为传播时钟)(设置对象的propagated_clock属性为true),此时的时钟延迟由源延迟和真实网络延迟组成,这里的网络延迟是根据时钟路径上的线延迟和单元延迟真实计算出来的,而不再使用set_clock_latency命令设置网络延时。

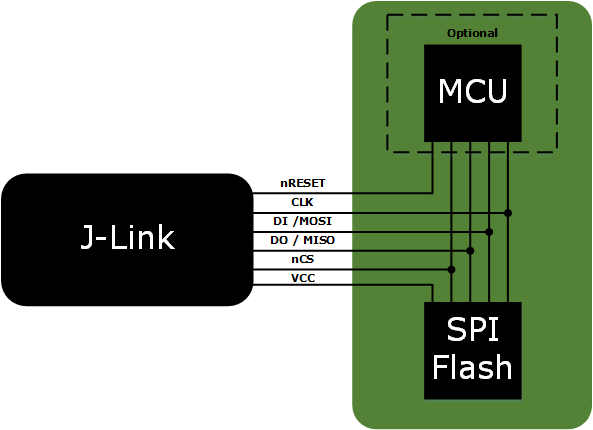

各型号的J-link、J-Trace和Flasher简介

Jlink/J-Flash是常见的烧录/调试工具,本文将说明其烧录Flash的工作原理。按照烧录方式来分,Jlink/J-flash可以分为直接烧录和间接烧录。

启动文件(Startup File)是嵌入式系统开发中的核心组件之一,它用于初始化系统并为主程序的运行做好准备。在大多数情况下,启动文件是用汇编语言编写的,并且与具体的处理器架构和工具链紧密相关。本文将以startup_stm32f103xe.s文件为例,说明启动文件中做了什么。

嵌入式:Keil的Code、RW、RO、ZI段的解析

torch.cuda.set_device函数用于设置当前使用的cuda设备,在当拥有多个可用的GPU且能被pytorch识别的cuda设备情况下(环境变量CUDA_VISIBLE_DEVICES可以影响GPU设备到cuda设备的映射)。

write_sdc命令用于将设计中的约束以Synopsys Design Constraints(SDC)格式输出为脚本文件(其实它并不是一个SDC命令,归为此类只是为了方便管理),在某些情况下,需要以文本形式导出一个设计的SDC约束(比如当Design Compiler配合非Synopsys的后端工具时)。