简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

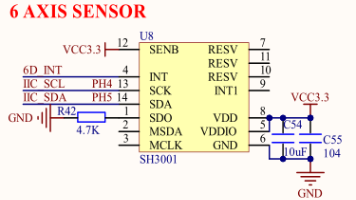

SH3001是Senodia公司生产的一款六轴姿态传感器,可测量芯片自身X、Y、Z轴的加速度以及角速度参数,通过姿态融合,进而得到姿态角。

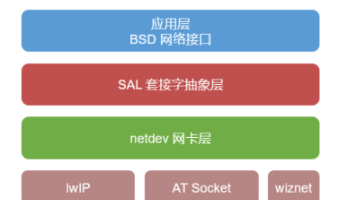

建立rtthread工程后,打开rtthread的源码文件夹,会发现,除了rtthread系统源码外,还有一个components源码目录。这个目录是RT-Thread操作系统的。

Cache是“高速临时仓库”,目的是让480MHz的内核不用等低速存储;Cache必须配合MPU使用,不同内存/外设要配不同的缓存策略;只要涉及DMA/外设,必须处理“Cache数据一致性”(Clean/Invalidate)。不用一开始追求“最优配置”,先按“开启I-Cache+D-Cache仅给AXI SRAM用+外设关Cache”的基础规则来,遇到具体问题(比如DMA读错数据)再针对性解决。

STM32H743的MPU(Memory Protection Unit,内存保护单元)是内核级的硬件安全机制,核心作用是划分内存区域限制访问权限(比如只读/只写/可执行)、校验访问主体(CPU特权/非特权模式),防止程序错误(如数组越界、野指针)或恶意代码破坏关键内存(如内核数据、外设寄存器),是提升系统稳定性和安全性的核心组件。代码量较大/多任务,担心内存错误导致崩溃;有安全/稳定要求(商用、

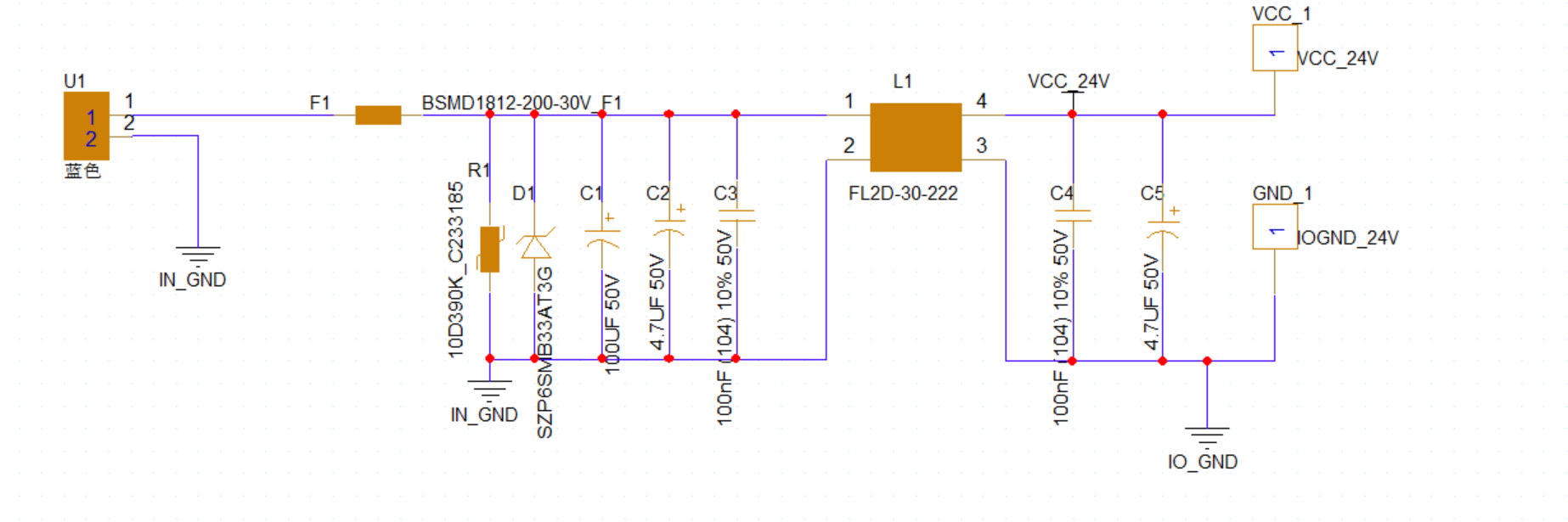

从输入到后级,按‘过流保护→大能量过压保护→精细过压保护’排序,且保护元件需靠近干扰源,被保护电路需靠近精细保护元件”。同时优化接地和布线,才能让三者协同发挥最大保护作用,避免“保护失效”或“干扰残留”。

一位资深嵌入式工程师分享职业发展心得,提出成为单片机高手的路径:需掌握C语言、数据结构、计算机组成等理论知识,以及数电模电等硬件基础。学习过程分为三个阶段:从外设驱动开发到模块组合,最终实现项目级代码编写。强调用面向对象思维解决C语言模块解耦问题,推荐RTThread操作系统。指出高级工程师需在底层优化、工程思维、行业认知等方面突破,从功能实现升级为打造稳定可量产的产品。文章旨在为行业新人提供成长

系统状态类ps(线程)、meminfo(内存)、list_sem(IPC),用于快速定位系统层面问题;硬件调试类pin(GPIO)、i2cuart(外设),验证硬件和驱动通信;高级定位类bt(调用栈)、heap(内存调试),解决崩溃、内存泄漏等复杂问题。这些命令覆盖了80%以上的调试场景,掌握后能大幅提升RT-Thread开发和问题定位效率。

新手/简单逻辑优先选,快速落地且易调试;中等复杂度、需维护的嵌入式项目选函数指针表,平衡简洁与扩展性;复杂逻辑/高端开发选面向对象,极致解耦但需OOP基础;固定逻辑/高效执行选状态表,适合协议解析等场景。按状态数量、资源限制、维护成本选择实现方式。