简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

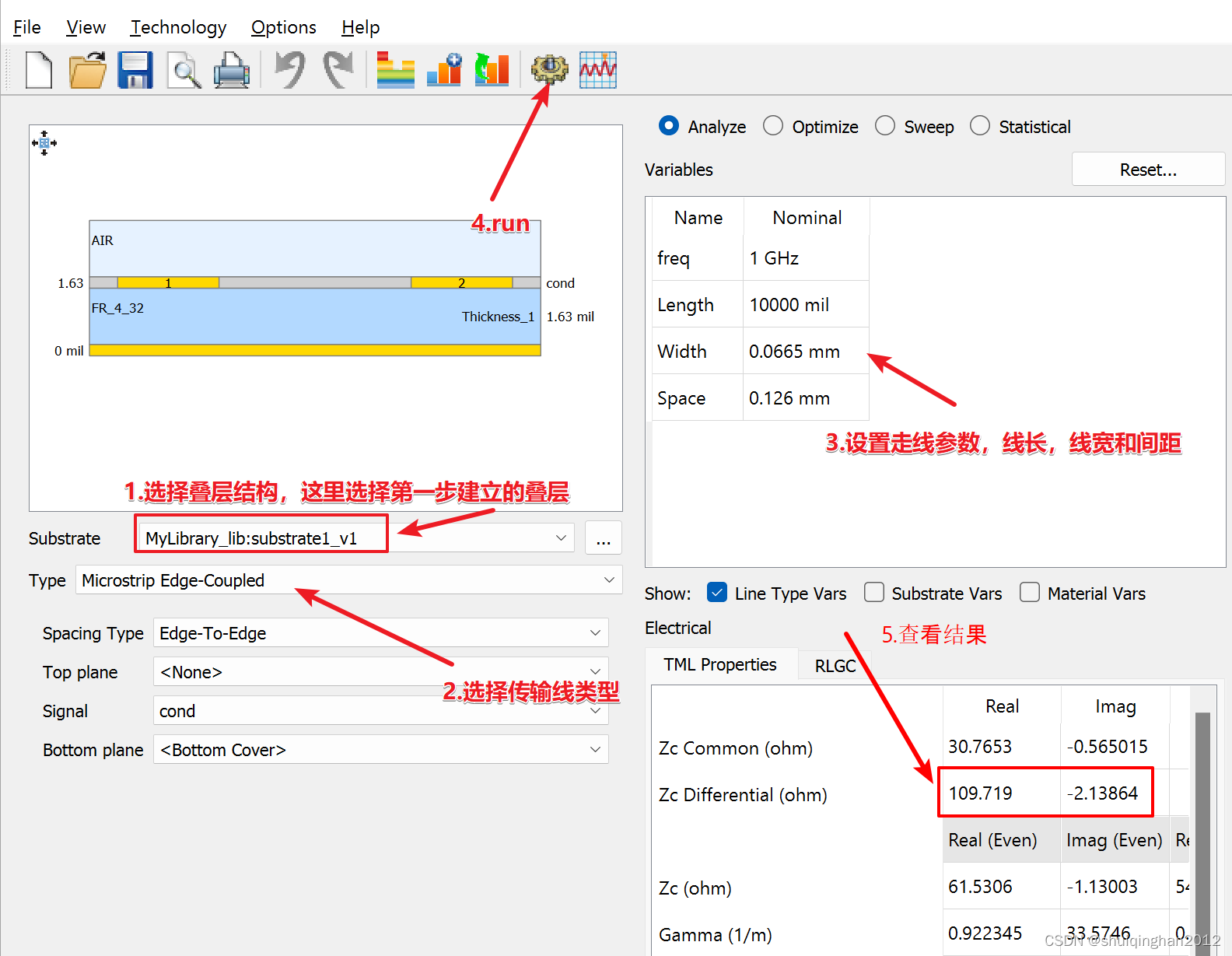

PCB阻抗计算

阻抗线计算的两种方式验证

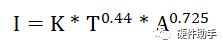

【转】PCB设计之“载流能力”

本文主要介绍PCB设计中走线和过孔的载流能力。走线的载流能力决定电流承载能力的因素主要有:铜箔厚度、走线宽度、温升、镀通孔孔径。但由于电流分布不是均匀的,因此很难精确计算。常用的公式:K为修正系数,一般覆铜线在内层时取0.024,在外层时取0.048;T为最大温升,单位为摄氏度(铜的熔点为1060);A为覆铜截面积,单位为平方mil(注意是squaremil);I为容许的最大电流,单位为安培。1o

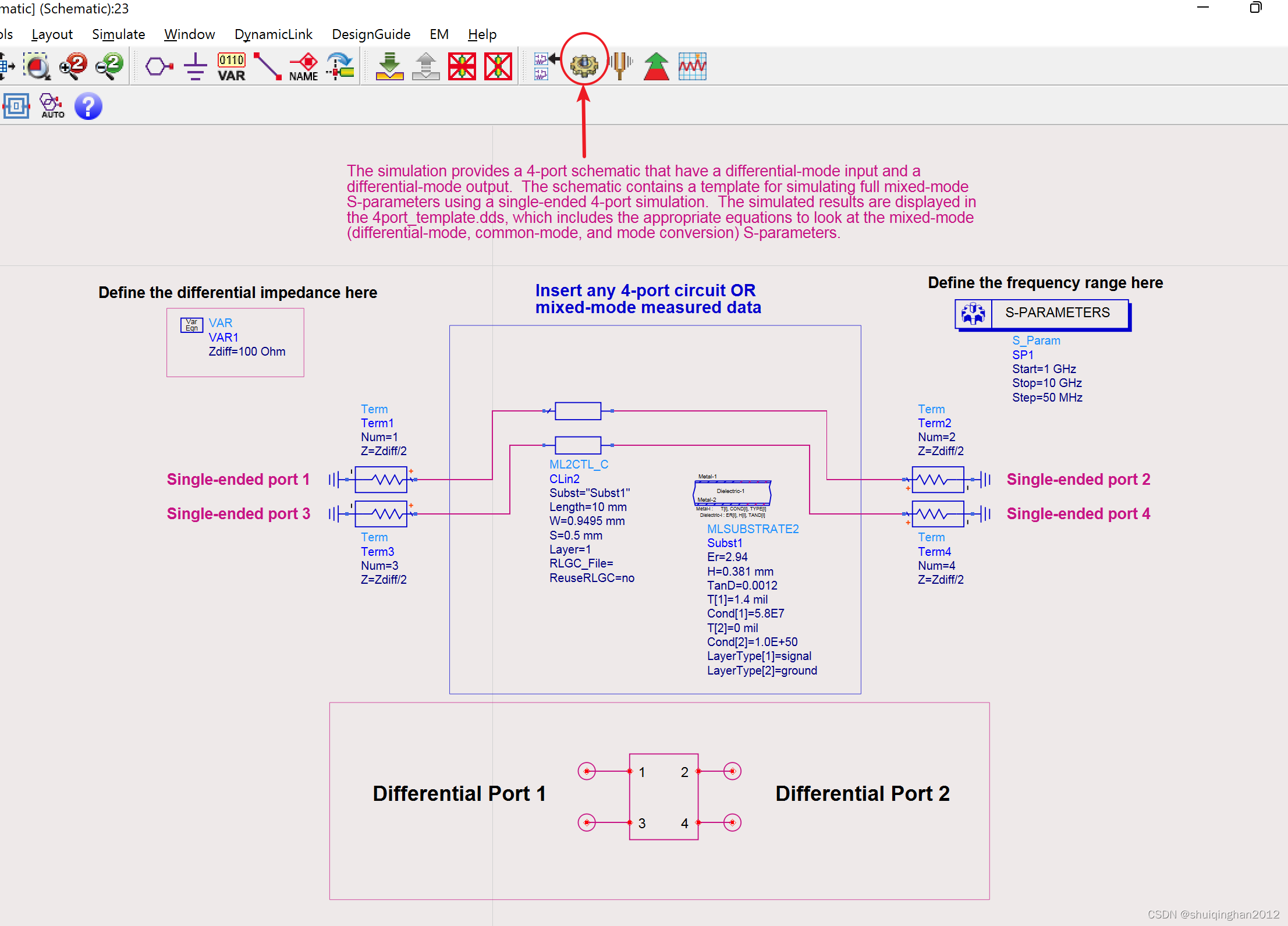

ADS差分传输线前仿真

主要以ADS自带4port S参数模板说明如何快速预估实际项目中差分信号的插损和阻抗,重点在渔,而非鱼。

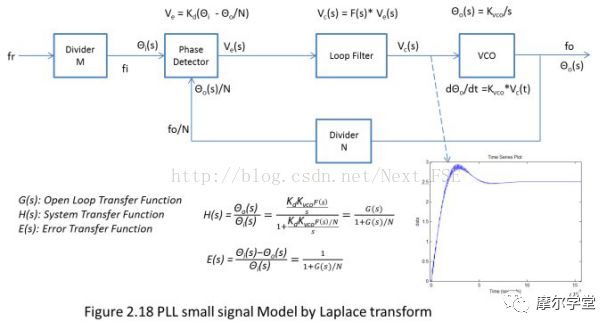

[转载]超详细:SerDes知识详解

Serdes 介绍

由I2C data信号低电平不到0,再思考I2C及GPIO

最近做项目测试时发现I2C data信号低电平不能完全到0电平,如下图量测到低电平最大值150mV左右,检查SOC及DL端SPEC,低电平最大值都是VIL max =0.35VDD 对于1.8V的IO 电平,这个电压是0.35x1.8=0.63V 显然150mV<<630mV,不影响逻辑判断,因此从项目的角度考虑,此问题并不影响项目,可以忽略。只是做项目的角度考虑,此问题就可以结束了。

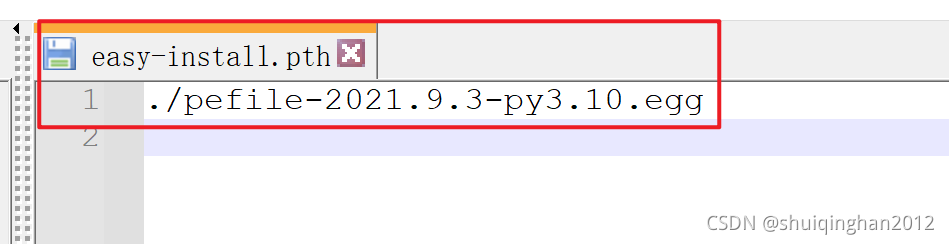

python Building wheel for future (setup.py) ... error

pip install pyinstaller 时报如下错误:Collecting futureUsing cached future-0.18.2.tar.gz (829 kB)Preparing metadata (setup.py) ... doneBuilding wheels for collected packages: future Building wheel for future

到底了