简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

遇到这种不报具体错误的错误,可以通过查询LOG文件,可能是因为license的原因导致编译失败

测试方式为,将信号源设置为任意频率,通过软件设置跳频频率到对应的频率点,触发方式通过9009 gpio模式,及时起点为GPIO的上升沿,同时将GPIO的上升沿作为触发条件。通过IAL观测信号稳定时间,经测试大概时间在60us,和ADI公布时间差不多。需要说明的是,这里的60us只是单纯的切换时间,未算api加载跳频频率的时间。

测试USB接口,通常采用操作系统进行测试,但是xilinx同样提供了裸机测试程序。该工程是将DDR虚拟成U盘,BIT运行起来需要对其进行格式化处理。首先是根据硬件设计BD文件,主要是根据IO口已经GTR接口配置。综合编译产生BIT,创建VITIS工程。

客户端命令行:iperf -u -c 2xx.1xx.1xx.1xx -p 20001 -l 1380 -B 172.16.28.173 -t 10 -i 1 -b 1800Ke.g. iperf -u -c 10.12.23.47 -p 8080 -l 1380 -B 10.12.32.45 -t 10 -i 1 -b 200M参数解释:1) 测试对端是10.12.23.4

通过 EXPORT_SYMBOL 导出的符号可以被包含GPL许可权的模块和不包含GPL许可权的模块调用;通过 EXPORT_SYMBOL_GPL 导出的符号只能被包含GPL许可权的模块调用具体使用如下面两个例子// A module#include <linux/init.h>#include <linux/module.h>int add_integar(int a, i

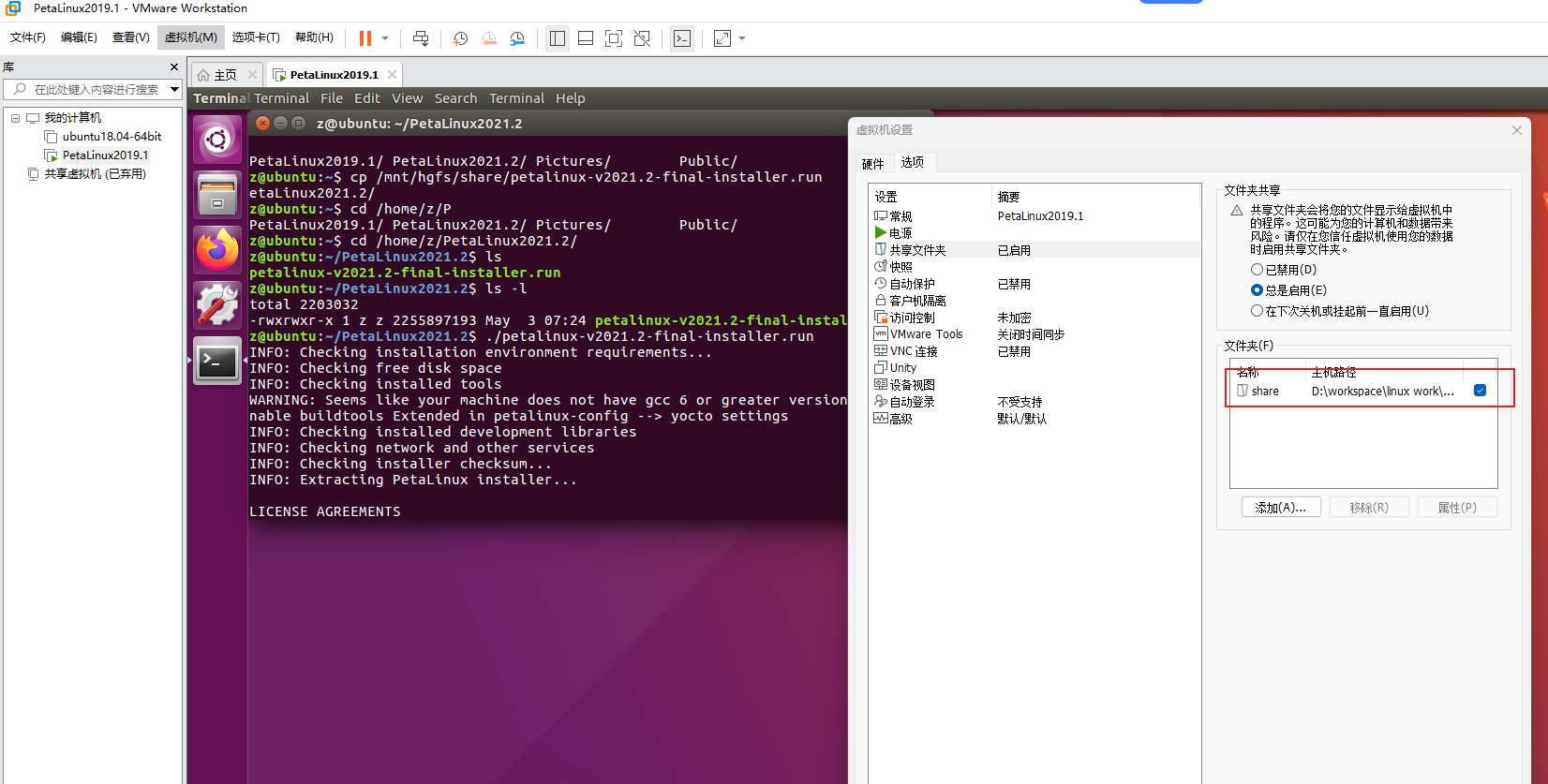

vmware 12 下安装 ubuntu 16.04 后,按往常的惯例安装 vmware-tools,安装时提示建议使用 open-vm-tools,于是放弃 vmware-tools 的安装,尝试使用 open-vm-tools。填入下面的内容,为了方便,就不单独配置各个共享文件夹了,直接将所有共享文件夹 mount 到一个目录下。安装时,apt 提示建议安装 open-vm-tools-des

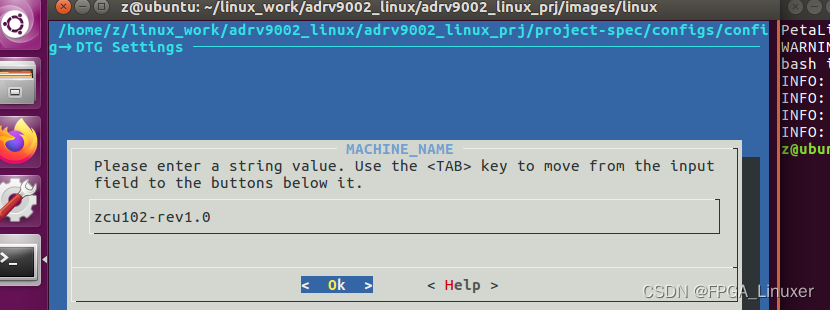

2.直接修改设备树,第二种方法对没有linux基础的朋友不是那么友好。但是系统启动以后ifconfig发现没有ETH0。1,在DTS settings下设置对应的板卡。BD文件使能了GEM。

2.生成的BOOT.bin,通过VITIS烧写到QSPI里,将boot设置为QSPI启动。挂载EMMC分区(注意不挂载是无法通过df -h查看对应的磁盘空间)对RFSOC适配petalinux做个记录。配置petalinux启动配置。重启就可以从EMMC中启动了。3.对分区分别完成格式化。4.查看分区挂载情况。

把 Verilog/VHDL 文件复制到你工程中重新建一个模块(脱离 IP 封装)。自动复制一份到新目录(例如 ./ip_repo/my_ip_v1_0_edit/)1️⃣ 右键 IP → “Open IP Example Design”(若可用)✅ 方案二:把 IP 解包(unpack)到普通源文件形式。👉 这样你得到的是完全可编辑的 IP 副本,不影响原版。2️⃣ 在生成的 example