简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

迄今为止,全球集成电路封装技术一共经历了五个发展阶段。通常认为,前三个阶段属于传统封装,第四、五阶段属于先进封装。当前的主流技术处于以CSP、BGA为主的第三阶段,且正在从传统封装(SOT、QFN、BGA等)向先进封装(FC、FIWLP、FOWLP、TSV、SIP等)转型。与传统封装相比,先进封装采用非焊接形式封装,应用场景主要适用于存储器、CPU和GPU等,在先进封装工艺中,除了需要用到传统的封

视觉语言模型被广泛定义为可以从图像和文本中学习的多模态模型。它们是一种生成式模型,可以接受图像和文本输入并生成文本输出。大型视觉语言模型具有良好的零样本能力,具有良好的泛化能力,并且可以处理多种类型的图像,包括文档、网页等。用例包括谈论图像、通过指令进行图像识别、视觉问答、文档理解、图像字幕等。一些视觉语言模型还可以捕获图像中的空间属性。当系统提示检测或分割特定主题时,这些模型可以输出边界框或分割

pad一般指die上面的金属开窗,可以通过金线与pin相连。ball一般指bga封装基板下面的锡球。bump一般指pad上面长出来的锡球。pin一般指封装上的引脚。

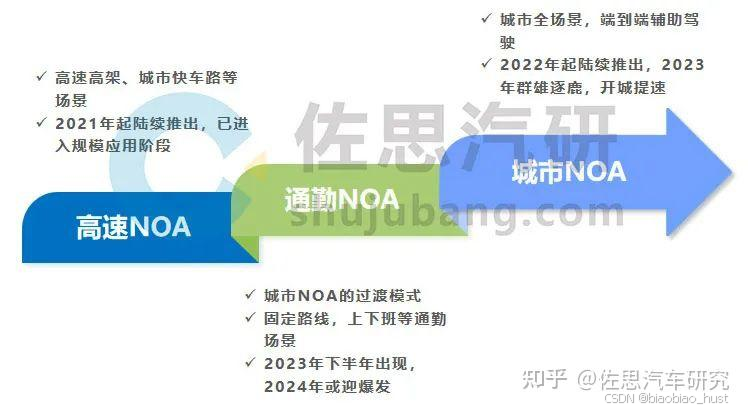

NOA全称为Navigate on Autopilot,通常被业界称为“领航辅助驾驶”或“高阶智能驾驶”。也有人叫或领航辅助功能,本质意思是把导航和辅助驾驶相结合,是一种基于车辆传感器和高精度地图数据的自动驾驶辅助系统,旨在帮助驾驶员在高速公路及城市道路中上更加安全、高效地行驶。NOA允许车辆在导航系统的指引下,自动驶入或驶出高速公路匝道,甚至在某些情况下实现自动变道超车。与传统的功能相比,NOA

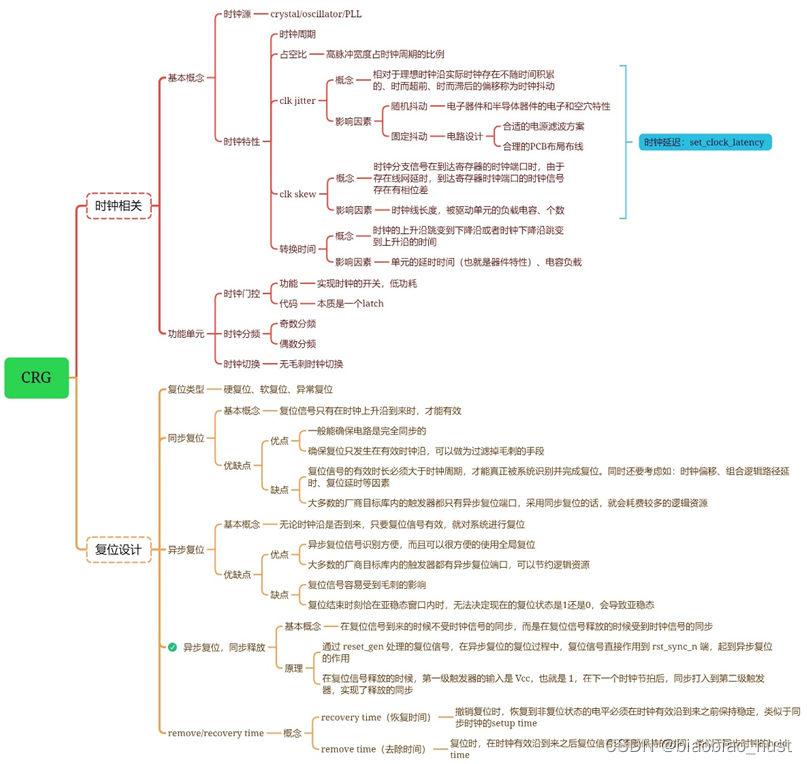

CRG(Clock and Reset Generation,时钟复位生成模块) 模块扮演着关键角色。这个模块负责为整个系统提供稳定可靠的,同时在系统上电或出现故障时生成,确保各个模块按预期运行。简而言之,CRG模块就像是SoC系统的心脏,提供着整个系统需要的时钟和复位信号。出于时钟复位结构规范设计和DFT可控的目的,一般会把相关电路放在一个集中的模块中管理,由专门的设计人员按需求进行设计与维护。

片上时钟控制器(On-chip Clock Controllers ,OCC),也称为扫描时钟控制器(Scan Clock Controllers,SCC)。OCC 是插在SoC上的逻辑电路。用来做DFT测试,基本原理是在 scan shift 模式下, 选通慢速的ATE 时钟,load 或 unload 扫描链;在 capture 模式下,对 free-running PLL clock 过滤筛

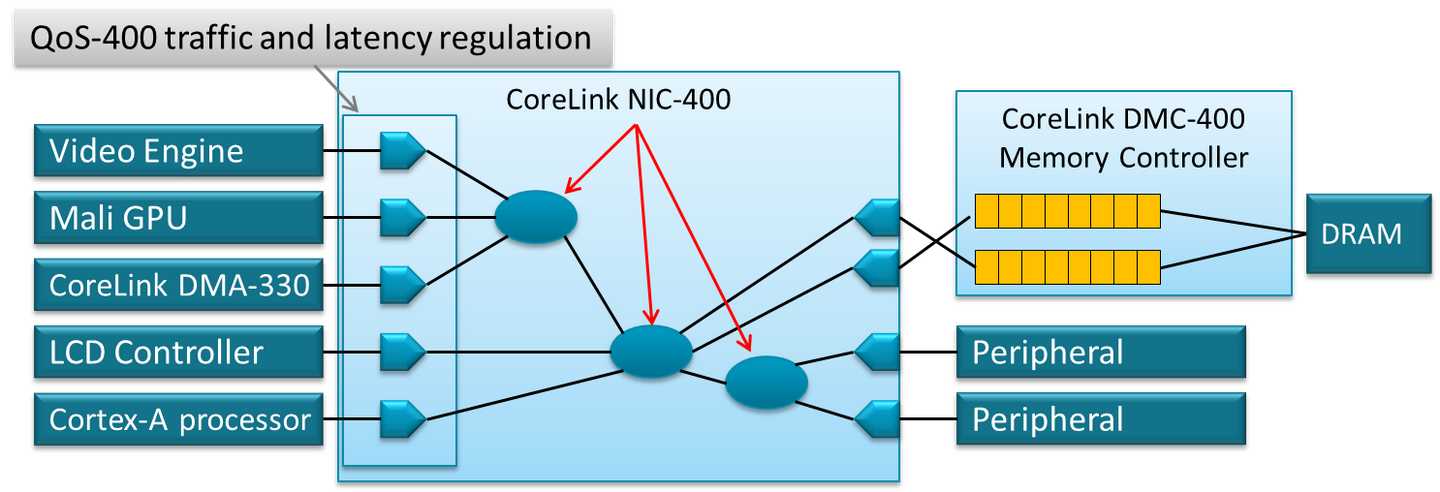

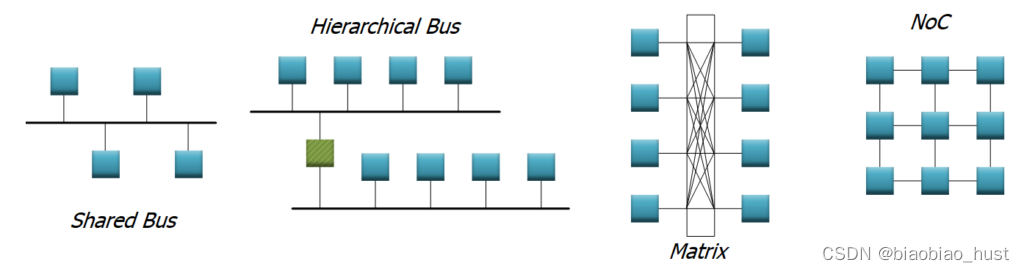

SoC (system on chip,片上系统)通常指在单一芯片上实现的数字,总线结构是该系统的主要特征,由于其可以提供高性能的互连而被广泛运用。随着单芯片上集成的处理器核数越来越多,片上互连架构经历了从到。借鉴了分布式计算系统的通讯方式,采用和技术替代传统的总线结构,从体系结构上解决了SoC 总线结构由于地址空间有限导致的可扩展性差,分时通讯引起的通讯效率低下,以及全局时钟同步引起的功耗和面积

他们各有特点,适合不同场景。一般手机芯片上使用交叉矩阵,网络处理器和服务器上使用环状网络,而网状拓扑也被大量应用于手机芯片。交叉矩阵连接的主从设备数量受到限制,但是效率最高,读写请求可以在1到2个周期内就直达从设备。如下图所示,这就是一个5x4的交叉矩阵:在28纳米制程上,5x4的配置下,这个总线的频率可以跑到300Mhz。如果进一步。要想进一步提高到频率,要么使用更好的工艺,要么插入寄存器,这样