简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

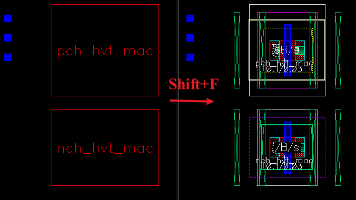

Layout视图下pcellEvalFailed问题

对《自己动手设计CPU》第四章的部分内容进行简化,因为某些资源下载不到了,因此就自己跑通了一套编译流程

本工程实现调用ZYNQ-7000的内部ARM处理器,通过UART给电脑发送字符串。硬件:正点原子领航者-7020开发平台:Vivado 2018、 SDK。

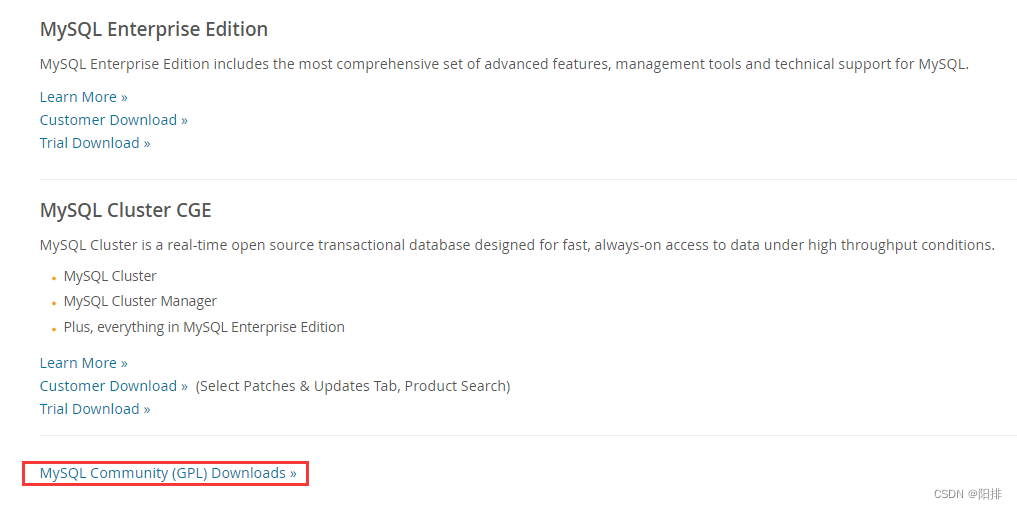

参考链接:进入官网:https://www.mysql.com/downloads/点击MySQL Community(GPL) Downloads下载社区版点击X86,64bit下载。点击No, thanks…直接下载。解压到英文目录,并在目录下新建一个 my.ini 文件,中间的内容包括:1.1.1 添加系统变量为了方便登录操作mysql,在这里我们设置一个全局变量点击"我的电脑"–>“属性”

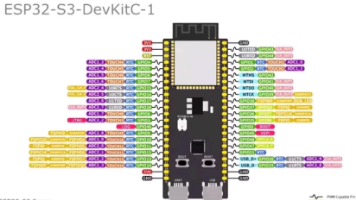

Arduino上通过Board Manager下载ESP32/8266的支持包。ESP32通过USB接口连接电脑,然后选定对应的ESP32S3 Dev Module板子。

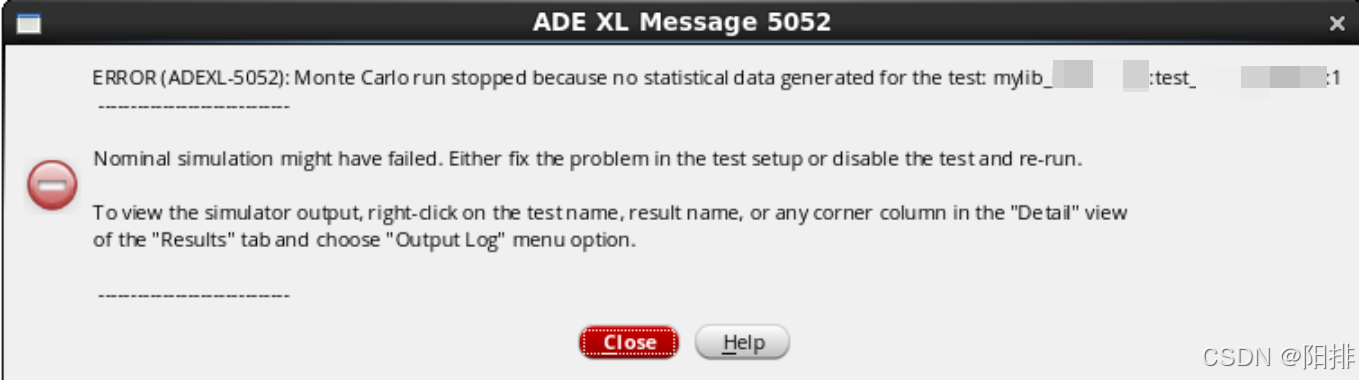

6、在自动弹出的ADE XL Test Editor中添加分析(Analyses)和输出(Outputs),操作与基本的ADE L仿真一样。但需要注意的是,此时需要对仿真的模型库进行修改。部分仿真库原来可能存在问题,因此尝试跳过此步骤,如果无法仿真,则再回来修改,取消勾选原来的Nominal,添加自己的Corners。取消勾选Nominal,点击上方的新建工艺角,选择模型库文件,选择section

在得到tsmcN28的iPDK包后,需要对其进行安装,来选择不同的金属层数、库类型等。安装完后才能在Cadence Virtuoso中使用。1、打开tsmcN28的库文件,找到3、配置选择:根据以下论坛中的问题,可以得知PyCell安装后可能存在layout无法正确显示的问题,但安装Skill Pcell则不会出现。因此在下方第一个选择中,选择2 Skill Pcell,其他的任选。

前端到后端的跨域问题需要通过axios来解决,而后端的跨域问题需要通过cros来解决。

一开始学习的时候为了节省硬盘空间,少安装了mpsoc等多种板级软件包,这是官方设计的fpga开发版,但没想到后期工作的时候还是碰到了。为了不删原来的软件,直接增量安装,可以进行以下操作。1 如果是早期的vivado 2018不用联网安装,采用iso镜像安装的版本。2 打开vivado,菜单栏help,add design tools or devices。4 重启vivado软件,就可以在新建工程

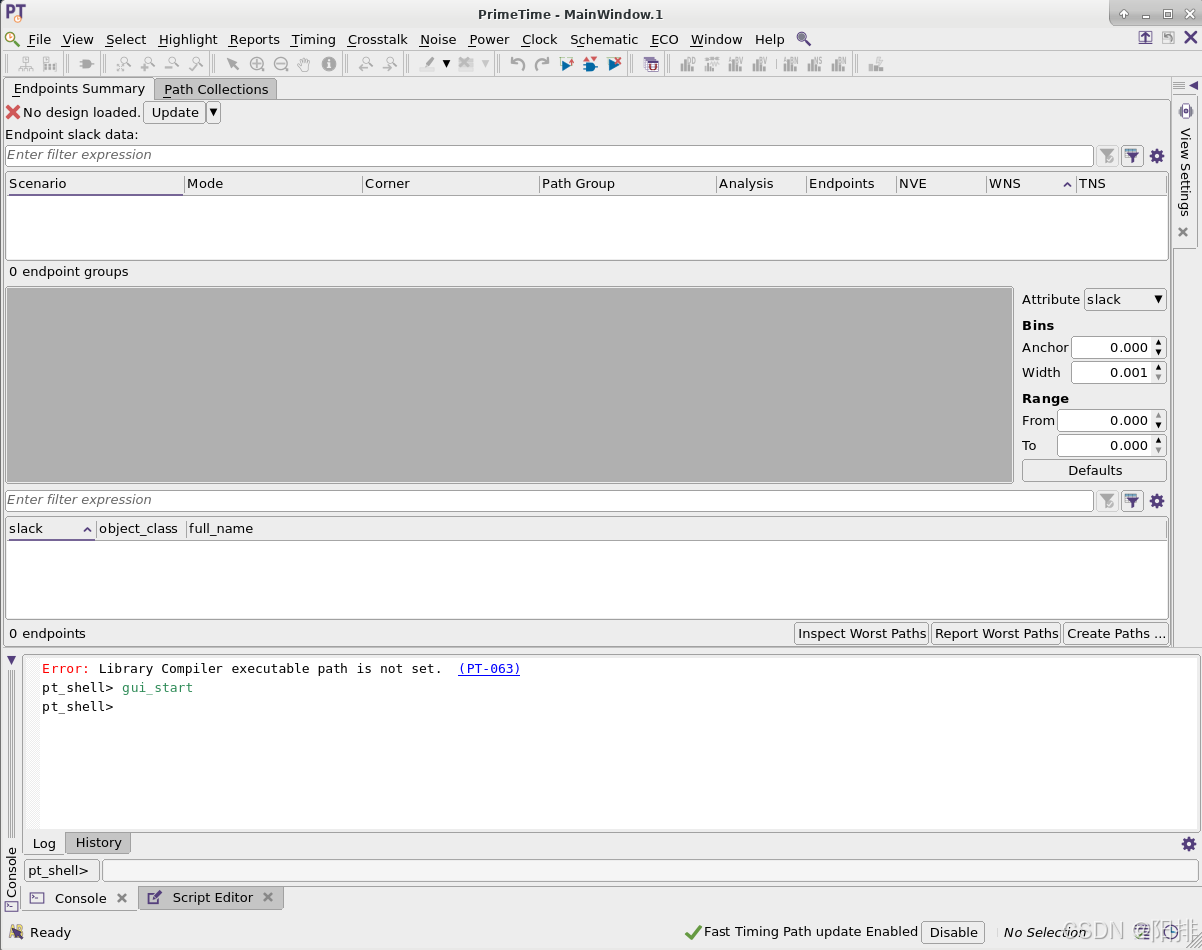

图形化界面:命令行启动:1.3 读入设计1.4 设计约束、负载和时序约束与DC综合时进行的时钟约束相同。set_disable_timingreport_disable_timingset_input_transitionreport_case_analysisreport_timingreport_constraintreport_bottleneck通常,对设计进行如下4种类型的分析:(1)从