简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

RCNN、Fast-RCNN、Faster-RCNN网络详解

RCNNRCNN算法流程:1.一张图片生成1k~2k个候选区域(使用Selective Search方法);2.对每个候选区域,使用深度网络(即图片分类网络)提取特征;3.特征送入每一类的SVM分类器,判别是否属于该类;4.使用回归器精细修正候选框位置。1.候选区域的生成利用Selective Search算法通过图像分割的方法得到一些原始区域,然后使用一些合并策略将这些区域合并,得到一个层次化的

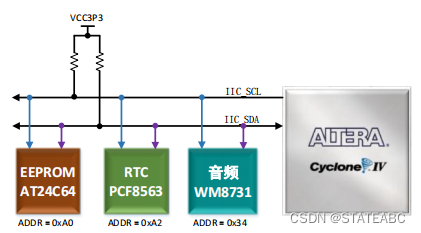

IIC通信协议

IIC即Inter-Integrated Circuit(集成电路总线),是一种双向、半双工、二线制串行通信总线。多用于主机和从机在数据量不大且传输距离短的场合下的主从通信。主机启动总线,并产生时钟用于传送数据,此时任何接收数据的器件均被认为是从机。

Linux系统编程入门(一)

1.环境搭建2.GCC3.静态库4.动态库5.Makefile

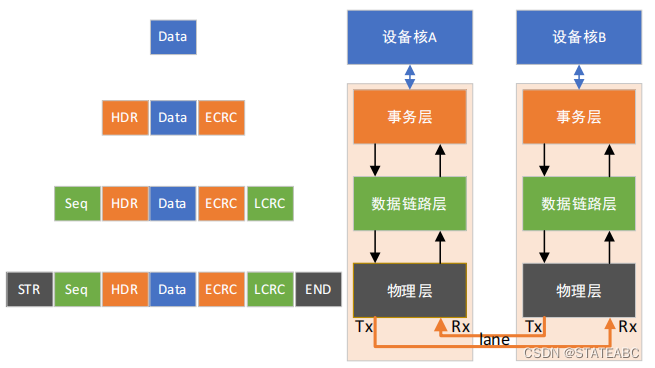

PCIe总线详解

PCI Express (peripheral component interconnect express) 简称PCIe,是一种高速、串行、全双工、计算机扩展总线标准,采用高速差分总线,并采用端到端的连接方式。

到底了