简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

《计算机体系结构量化研究方法(第六版)》个人总结——1.2 计算机的分类

《计算机体系结构量化研究方法(第六版)》整理笔记——1.2 计算机的分类

AES加密算法原理及python实现

AES加密算法原理及python实现AES对称加密算法1.Rijndael的设计思想2.AES的基本结构3.加密解密的详细结构4.四种轮操作1.字节代换(SubBytes)2.行移位操作(线性变换)3.列混合(MixColumn)4.轮密钥加1.密钥编排5.AES解密6.AES的python实现AES对称加密算法 AES加密算法即密码学中的高级加密标准(Advanced Encryption S

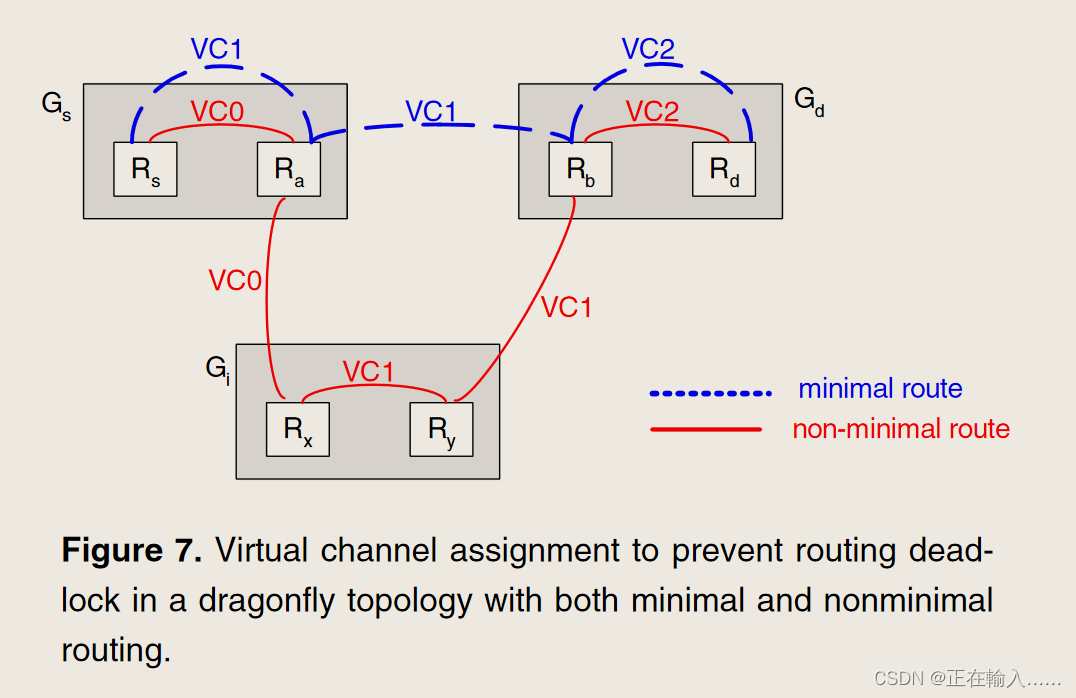

Dragonfly 拓扑的路由算法

John Kim, William J. Dally 等人在 2008 年的 ISCA 中提出技术驱动、高度可扩展的 Dragonfly 拓扑。而文章中也提到了 针对 Dragonfly 拓扑的路由算法。本文对其中提到的路由算法进行汇总归纳。主要是讨论蜻蜓拓扑的最小和非最小路由算法。

AES加密算法原理及python实现

AES加密算法原理及python实现AES对称加密算法1.Rijndael的设计思想2.AES的基本结构3.加密解密的详细结构4.四种轮操作1.字节代换(SubBytes)2.行移位操作(线性变换)3.列混合(MixColumn)4.轮密钥加1.密钥编排5.AES解密6.AES的python实现AES对称加密算法 AES加密算法即密码学中的高级加密标准(Advanced Encryption S

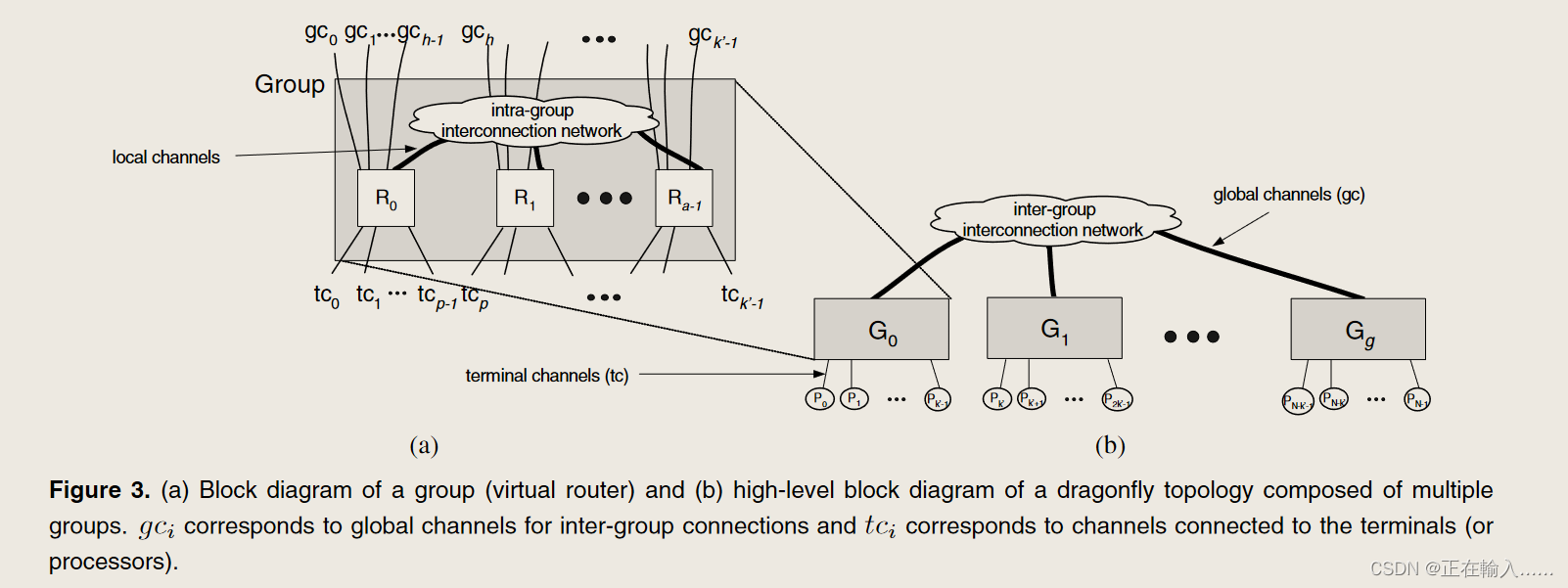

【Interconnection Networks 互连网络】Dragonfly Topology 蜻蜓网络拓扑

Dragonfly 蜻蜓拓扑具有三层的分层网络,从小到大分别是路由器(router),组(group)和网络系统。

在python中使用SVM

在python 中使用支持向量机

到底了