【入门教程二】基于DE2-115的My First Platform Designer(Qsys) 工程

在上一个教程My First FPGA工程当中,模块创建直接用Verilog code 写的,那是一个最简单的系统, 如果遇到稍微大一点规模系统,直接的code编写将会显得非常费时了,其实Intel还有另外一个非常好用的工具帮助工程师快速设计FPGA工程,那就是Platform Designer(Qsys)。图形界面,简化系统开发复杂性工程师在设计过程中可调用Intel Quartus 软件IP(

- 本教程演示了如何使用Platfrom Desinger工具轻松地创建一个FPGA设计, 设计过程中可调用Intel 提供的IP,也可以调用用户自己创建的IP模块,并支持其与Quartus 软件中的IP模块进行标准化互连,以便在系统中使用,从而加速了嵌入式系统的设计。

关于自定义IP请参考教程

Platform Designer 自定义IP(用于纯RTL设计)-CSDN博客

或者教程

Platform Designer 自定义IP(Avalon MM 接口,用于Nios II/Nios V/HPS等系统控制)-CSDN博客

一、Platfrom Desinger介绍

在上一个教程My First FPGA工程当中,模块创建直接用Verilog code 写的,那是一个最简单的系统, 如果遇到稍微大一点规模系统,直接的code编写将会显得非常费时了,其实Intel还有另外一个非常好用的工具帮助工程师快速设计FPGA工程,那就是Platform Designer(Qsys)。

- Platform Designer是图形界面,简化系统开发复杂性

- 工程师在设计过程中可通过Platform Designer调用Intel Quartus 软件IP(Intel官方已经写好的现成功能模块)

- Platform Designer允许用户创建自己的IP模块,并支持其与Quartus 软件中的IP模块进行标准化互连,以便在系统中使用,从而加速了嵌入式系统的设计

- 自动为IP模块间生成内部的可连接线路

- 设计的系统可以作为子系统给其他系统使用

- 后期通过Platform Designer界面来修改系统设计将比直接修改HDL文件要简便得多

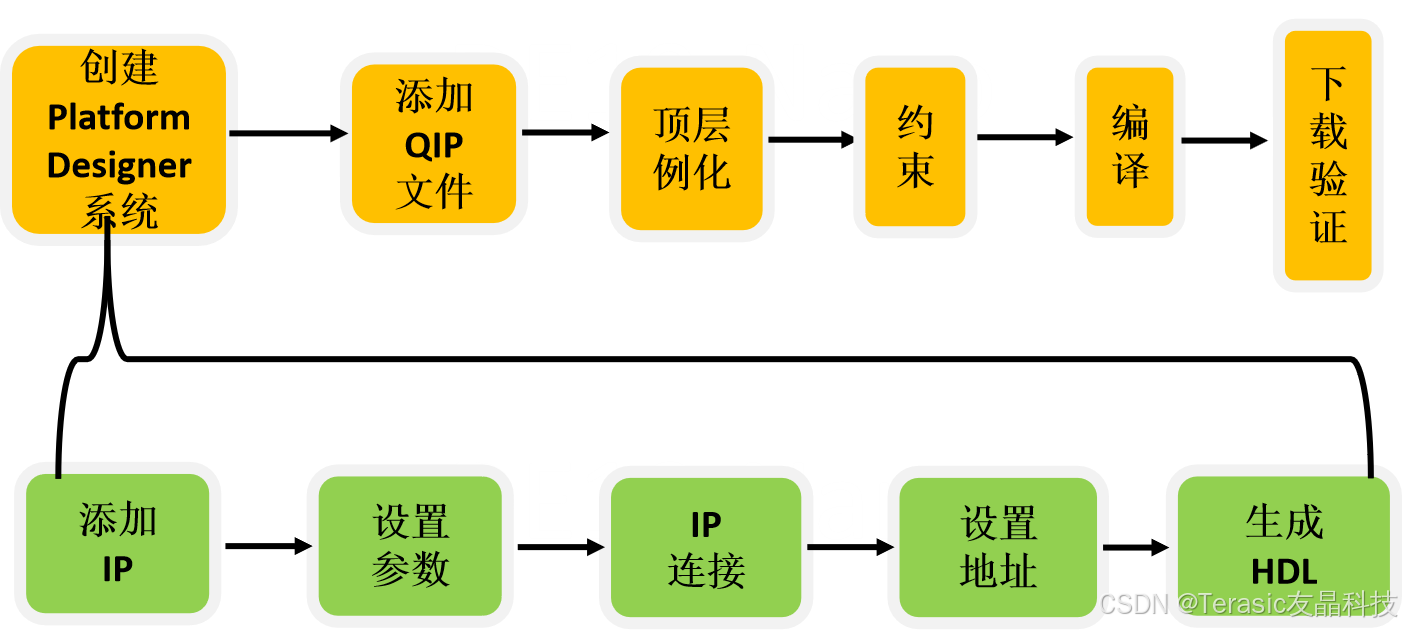

二、Platform Designer 工程设计流程

三、Platform Designer用户界面及使用介绍

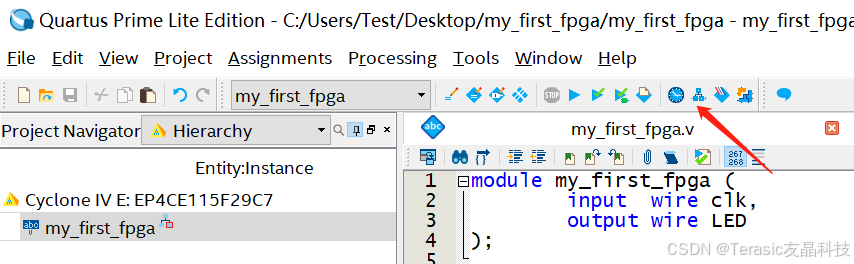

双击Quartus图标打开该软件。直接点击下图的Platform Designer图标:

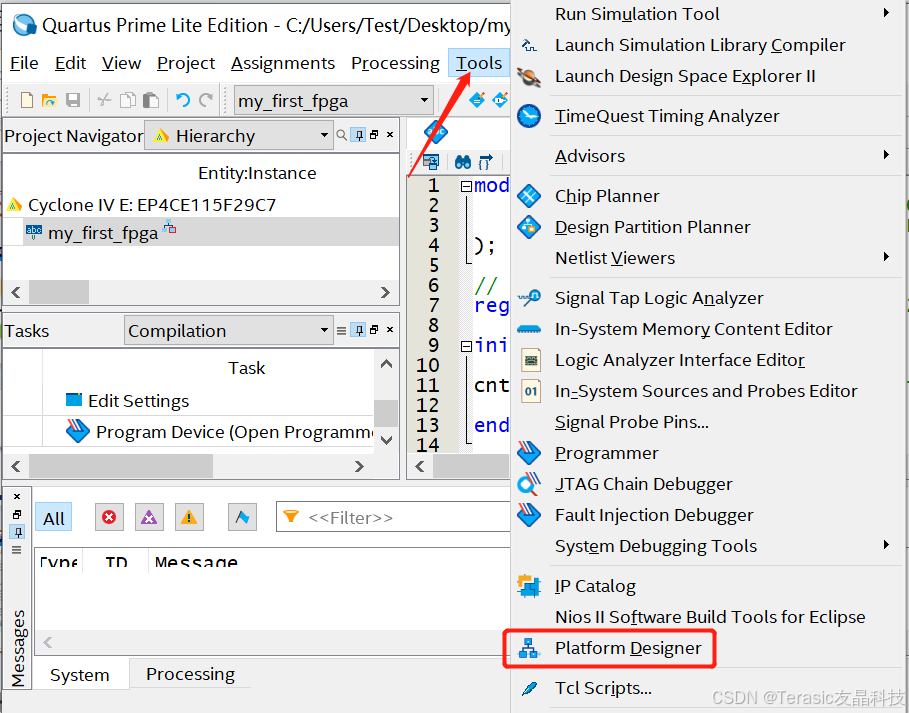

或者选择Quartus Prime的tool菜单来选择Platform Deisner 来打开该工具。

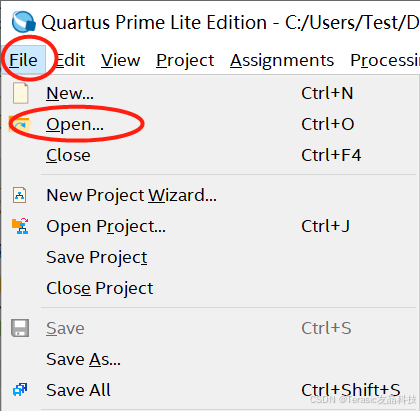

当然,如果你已经有一个Platform Deisner 设计,但是想修改它,你可以通过File菜单点击Open选择打开你的Qsys文件。

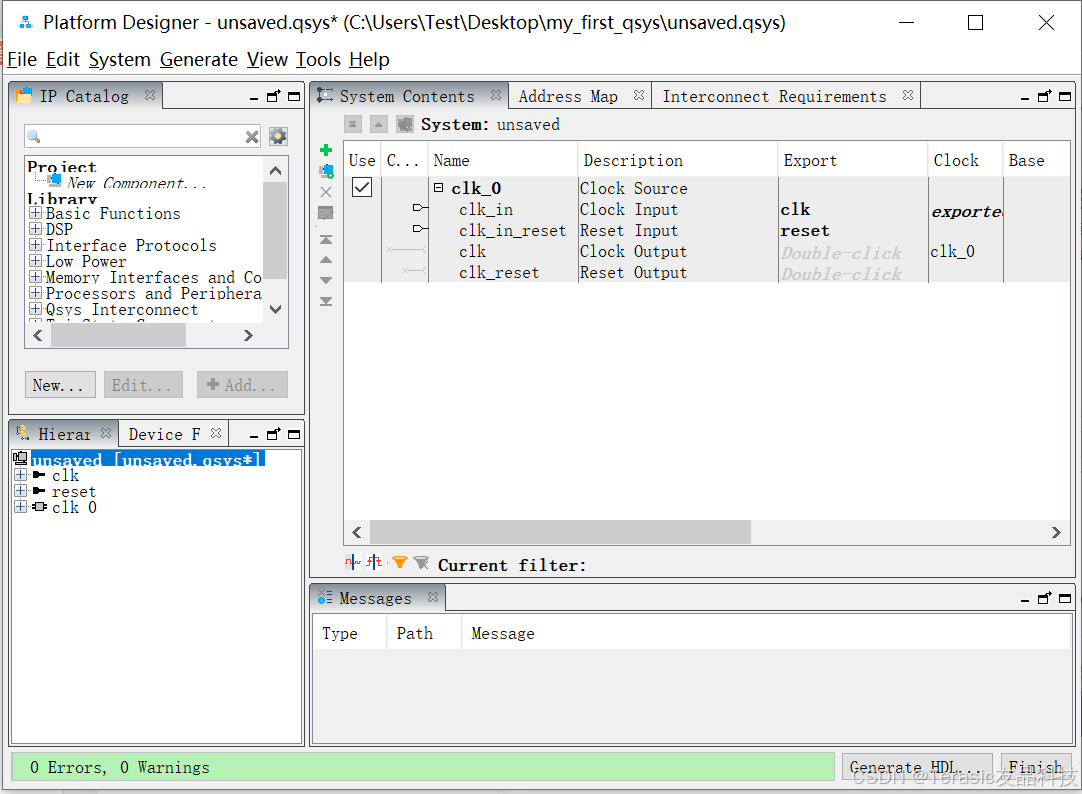

Platform Designer用户界面:

打开Platform Deisner 菜单以后,弹出一个Platform Deisner 用户界面,它是由一些用来构建系统和分析结果的选项单构成,截图上面可看到的有系统内容设置窗, IP目录选项窗,层次选项窗,信息窗口等,所有的选项单可以根据你是否需要相关的信息来使能或者关闭。

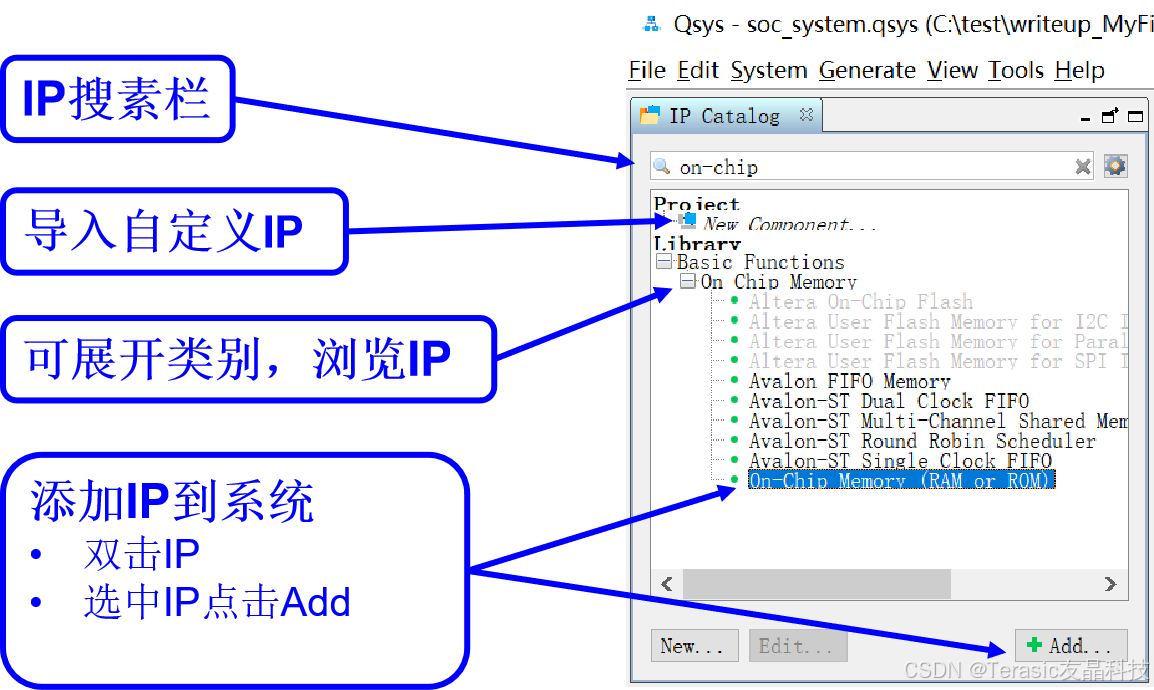

IP目录选项窗:

在IP目录选项窗中IP目录列出了所有可供加入到你当前Platform Deisner系统中的IP, 标准的IP 放于Library 库部分 你还可以通过查找功能,直接通过关键字检索你需要的IP 只需要双击元件的名字或者选中元件点击Add,就可以加入元件到你的系统。

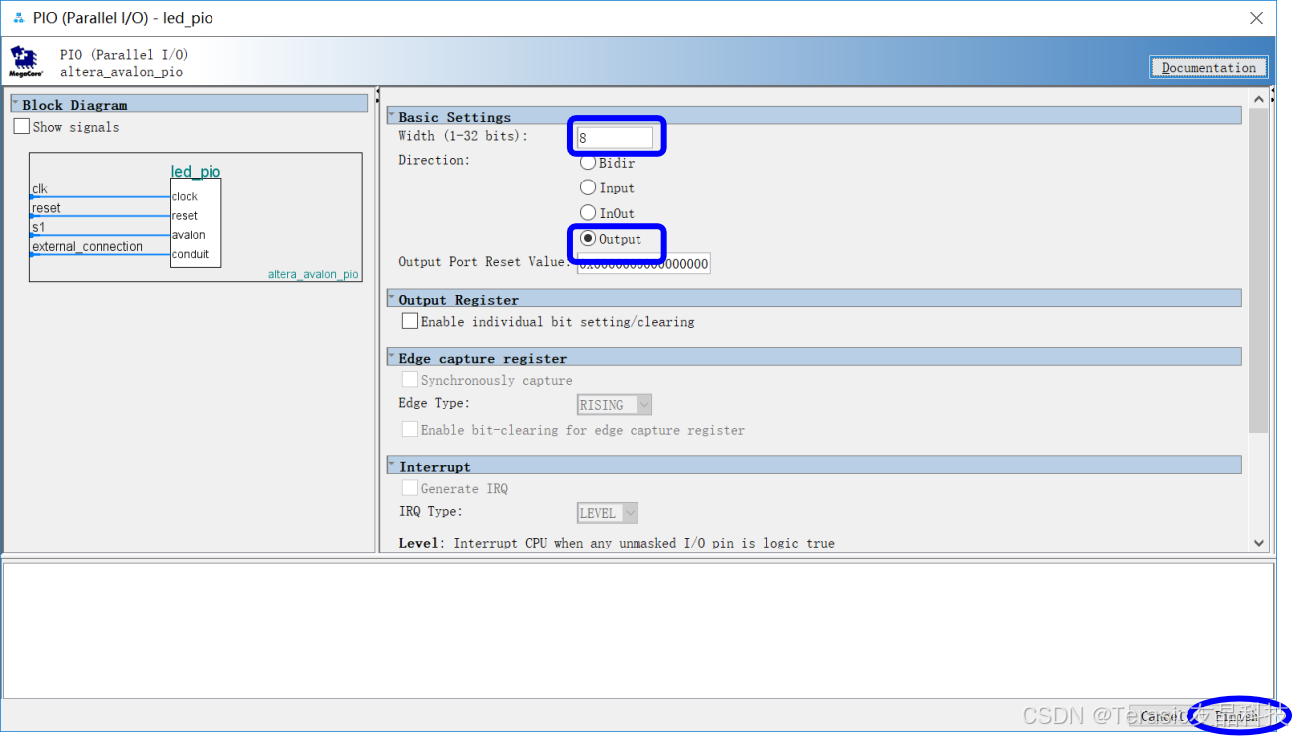

IP参数设置:

在IP目录窗口选择的组件,可以通过图形界面去设置其参数。 比如在IP目录窗口选择一个PIO组件,当点击Add之后,会出现对应的元件参数编辑窗口,你可以根据系统的要求定义元件的参数。 一个PIO (Parallel I/O) 组件,设置8bit, 设置输出。然后单击对话框右下角的Finish按钮。 您可以用相同的方法添加些其他IP,当所有IP 都添加和设置完毕,你要将系统中的元件连接在一起。

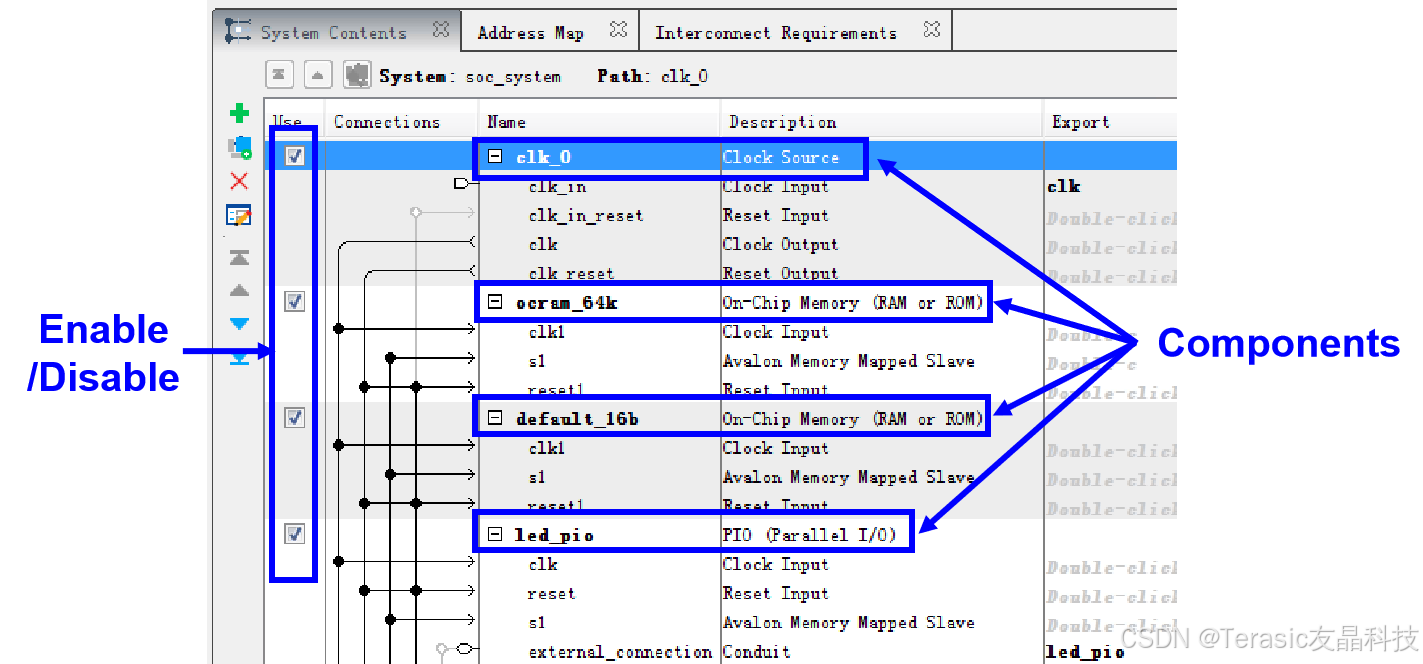

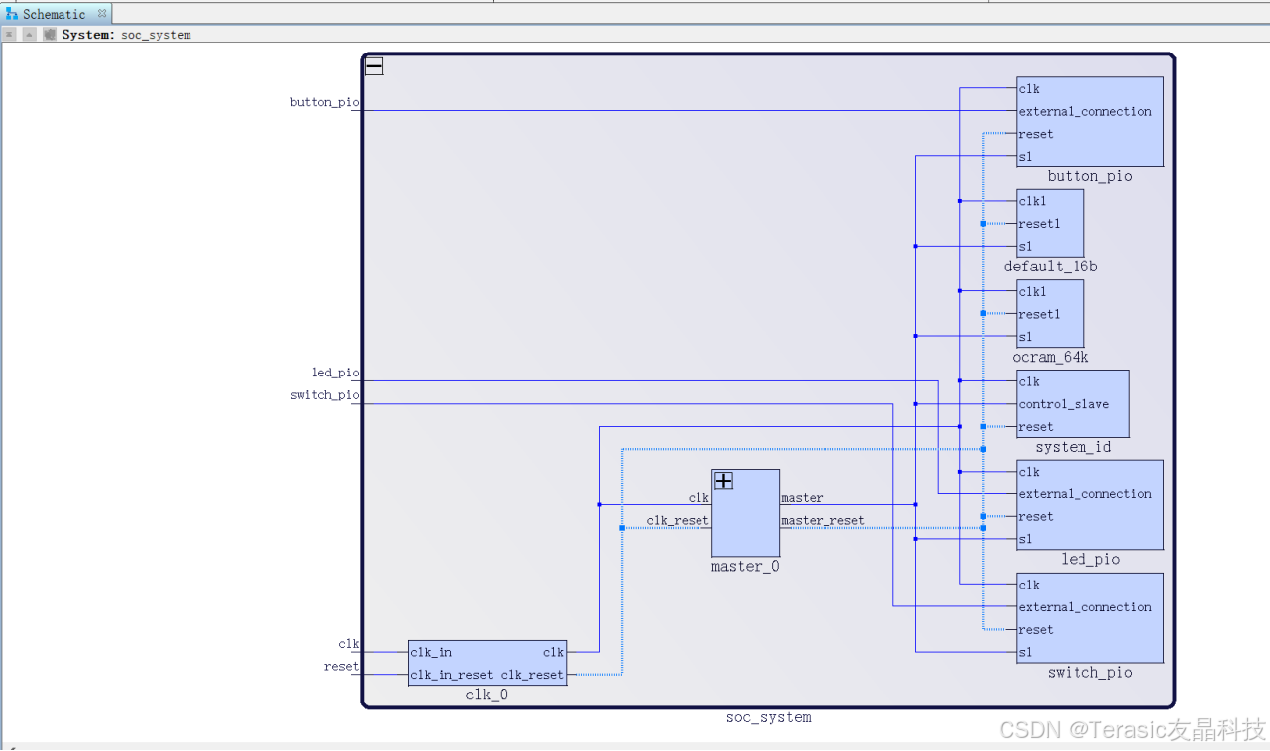

系统内容设置窗:

系统内容设置窗口显示了当前系统里面的一些元件和子系统 该窗口可以轻松管理一个元件和系统的其他部分的关系 以及连接 你可以在不删除元件的情况下,通过左边的对勾选项使能和不使用当前元件 还可以选中元件对其进行各种操作,如重命名,编辑参数等。 比如把刚才添加的PIO组件重命名为led_pio。

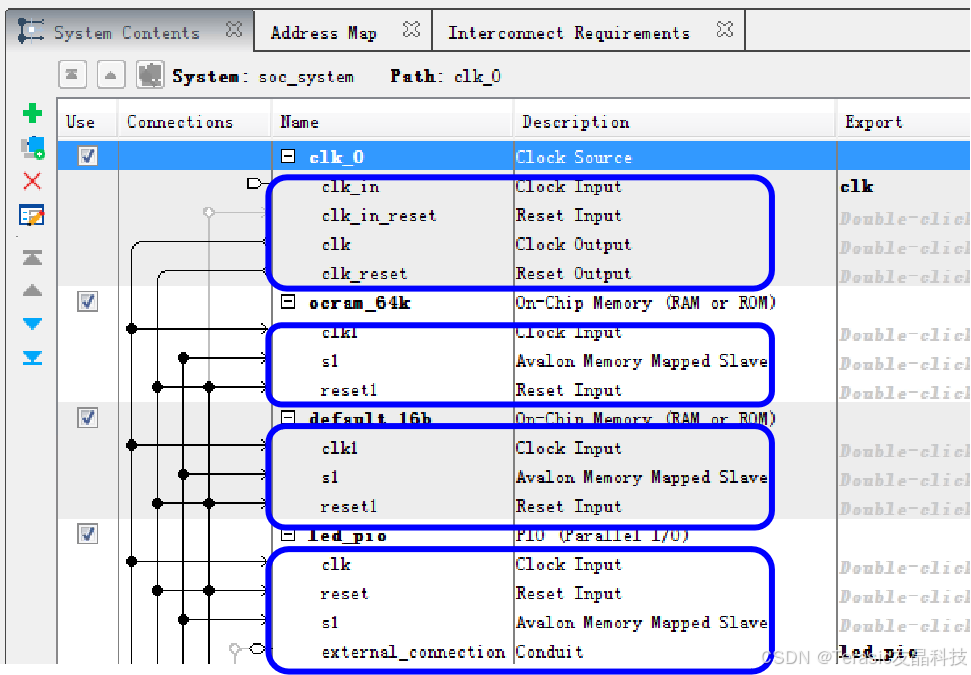

Platform Deisner的IP之间的连接:

当你向一个系统添加一个元件时,系统内容窗口会显示这个元件的所有接口,大部分甚至所有的接口都需要被连接 比如图上 led_pio的元件有4个接口需要被连接 一个时钟 和一个 复位的输入接口 一个 Avalon MM slave接口 和一个Conduit(导管)接口。

IP信号之间的连接方法一:

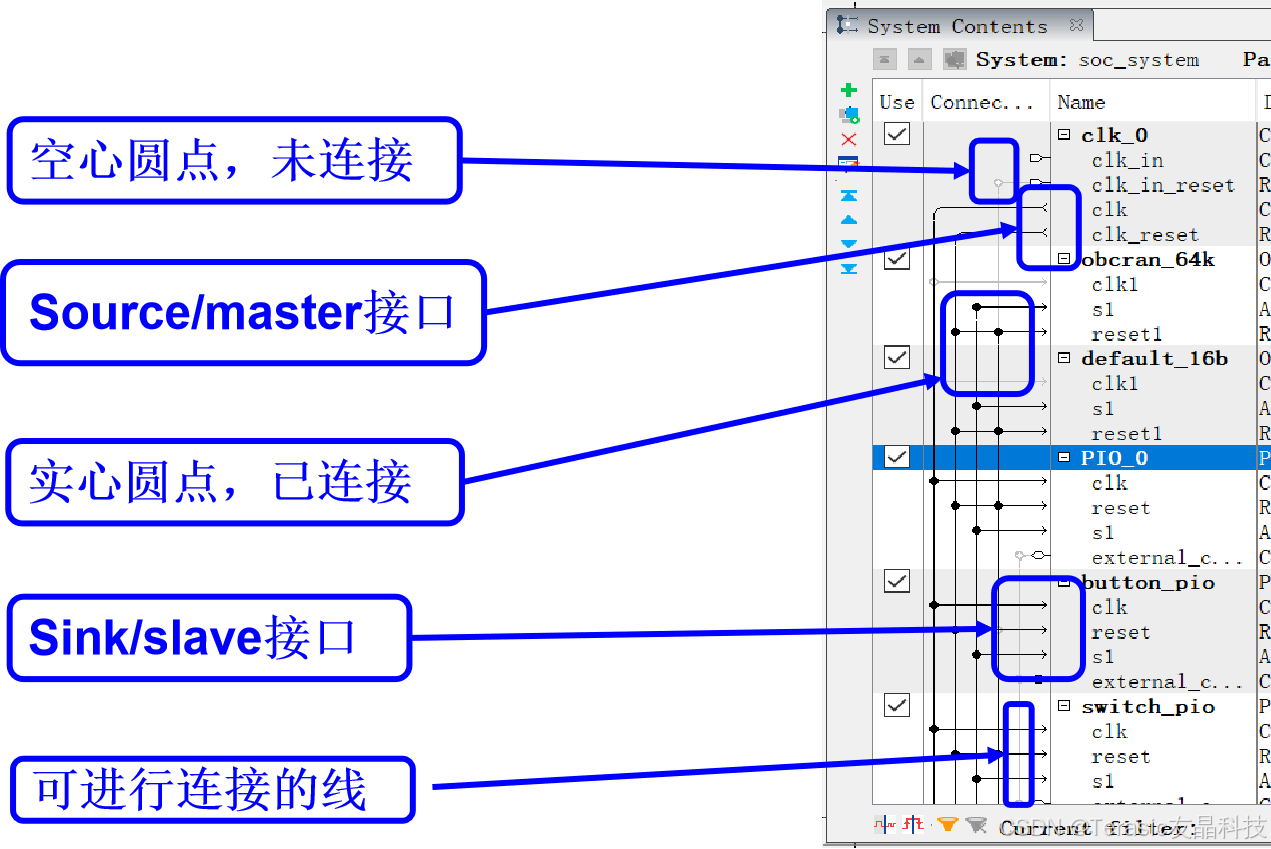

Qsys系统内容窗口中的连接面板是将元件连接在一起和检查连接的主要途径 使用面板可以快速方便的连接主从端口,时钟/复位的输入和输出端口,数据流的源和目的 中断的收发端口,用户指令的接收发送端口 实心的黑色圆点,表示两个端口已经连接,空心圆点表示尚未连接 。

再看看连接面板上,箭头向外的端口表示这是一个主端口,向内的箭头 表示这是一个从端口 虚线表示可以进行连接的线, 实线则是已经连接的线。

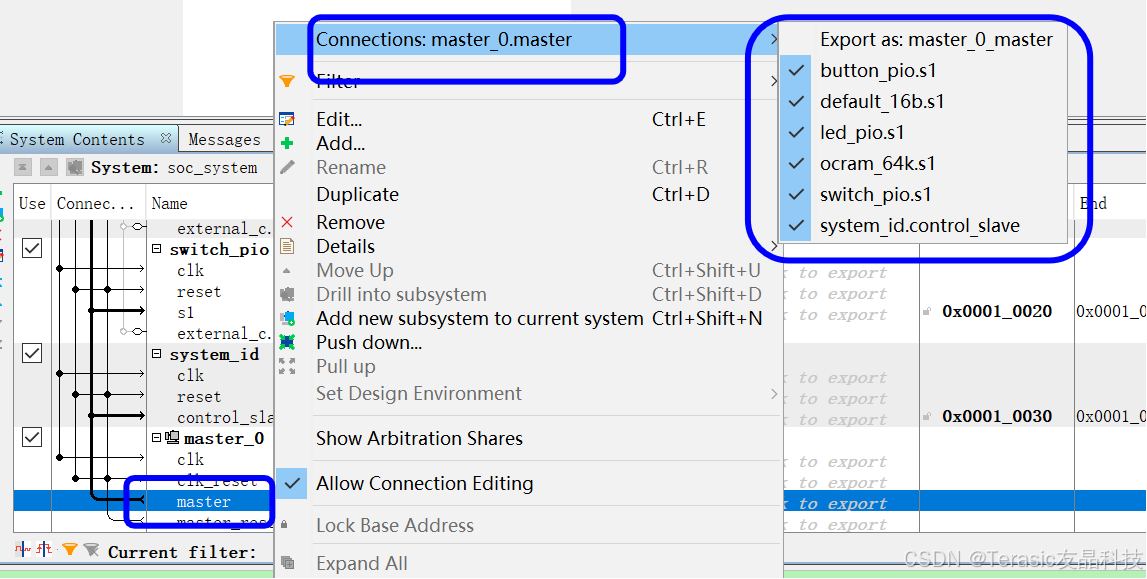

IP信号之间的连接方法二:

还可以通过右击你需要连接的端口,在连接菜单会列出你能连接的接口列表,点击进行连接。

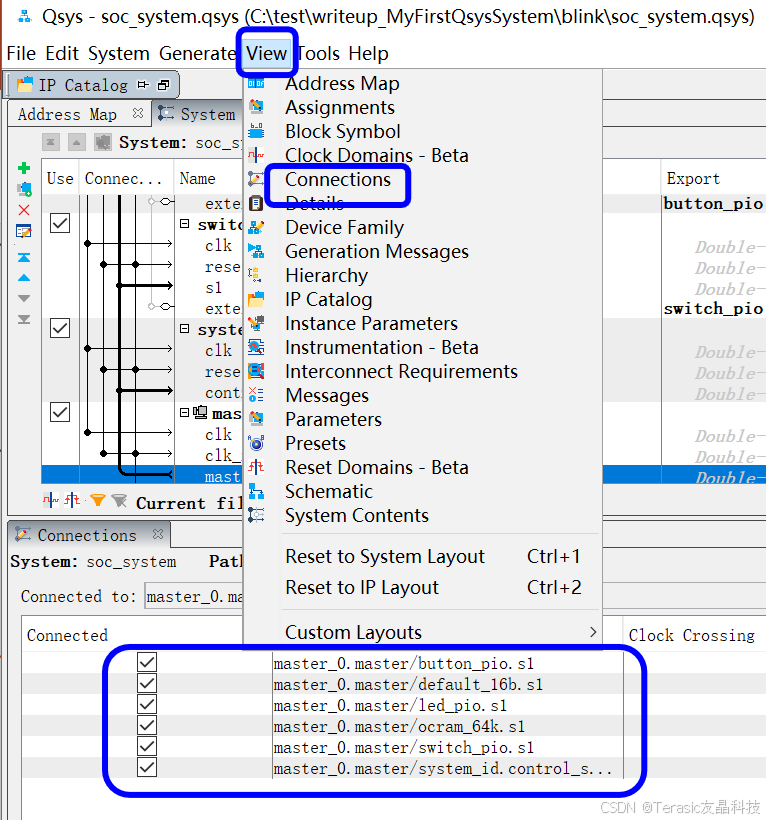

IP信号之间的连接方法三:

还可以通过在View里面打开连接标签,在这里的列表里,通过选中打勾 进行系统的连接。

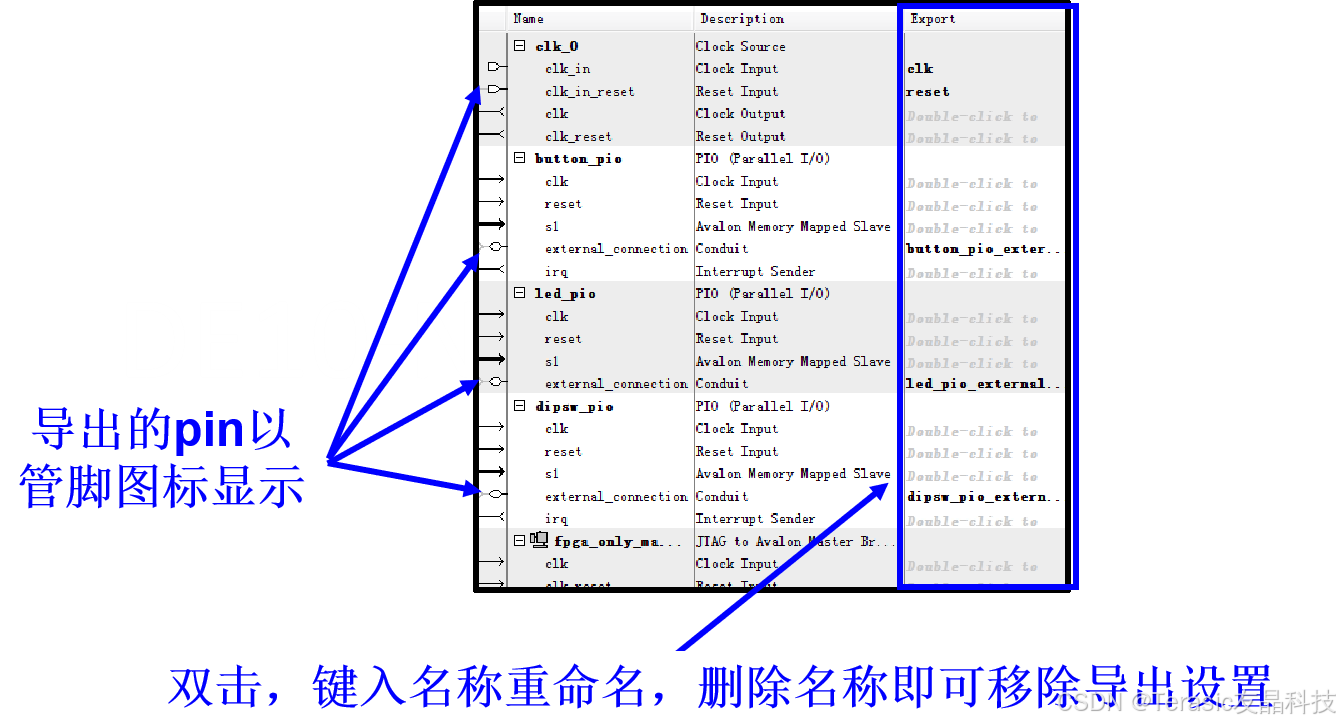

Platform Designer的IP的管脚导出:

在Platform Designer中,任何在系统内容中显示的元件的接口,都可以被导出 通过导出功能,这些信号可以被带到Platform Designer设计的顶层,并且连接到外部,比如FPGA管脚或者其他逻辑电路 要导出元件接口,只需要在该接口的Export栏,双击,即可,一旦导出,连接面板会由线变成管脚图标。

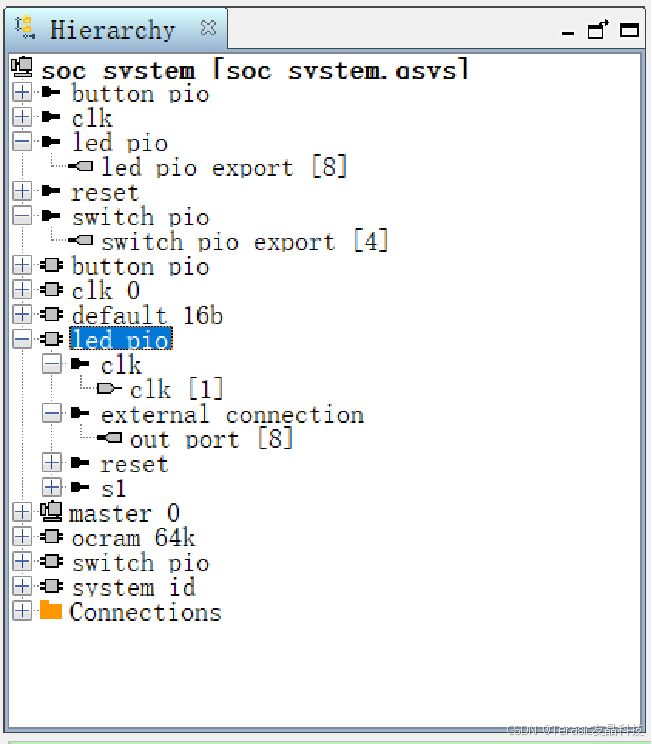

IP连接完成以后,我们可以通过一些窗口审查系统中各个元件的连接,确保准确。 这里有一些其他窗口,能帮助你检查自己的系统。

层次窗口,可以看到整个Qsys系统的组件端口和连接细节,比如可以看到各个组件的时钟,复位,输入端口,输出端口,以及数据总线的连接情况。

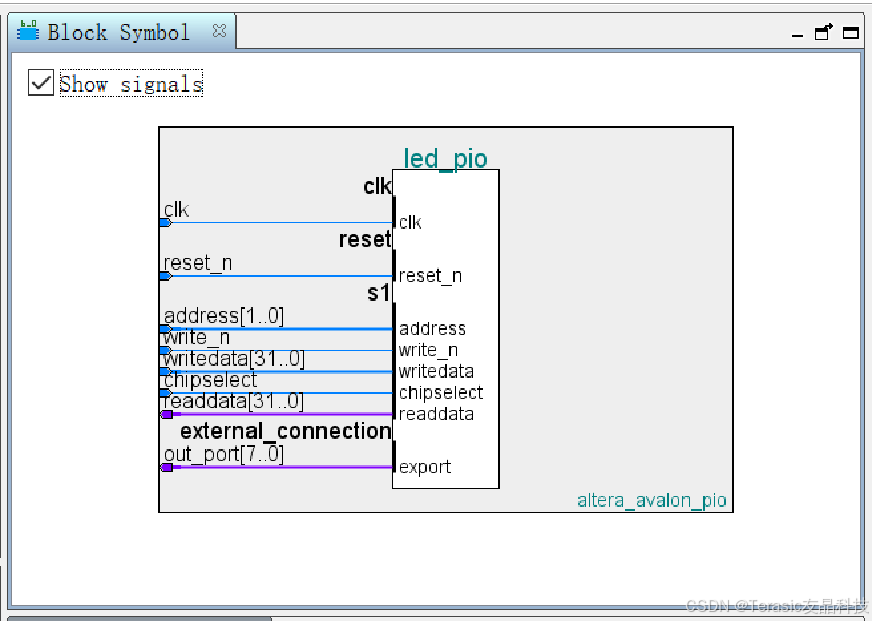

在符号模块窗口,显示了当前选中组件的顶层模块,可以看到该模块对外的所以连接端口,其中加黑的端口,是用户可以自定义连接修改的。

在符号模块窗口,显示了当前选中组件的顶层模块,可以看到该模块对外的所以连接端口,其中加黑的端口,是用户可以自定义连接修改的。

四、地址映射(本实验用不到)

如果是想通过HPS或者Nios II/Nios V 去访问这些组件,就要通过组件地址去进行访问。如果只是设计RTL电路,不涉及master(CPU)则可以不管Platform Designer里面的地址设置。也就是本节内容可略过。

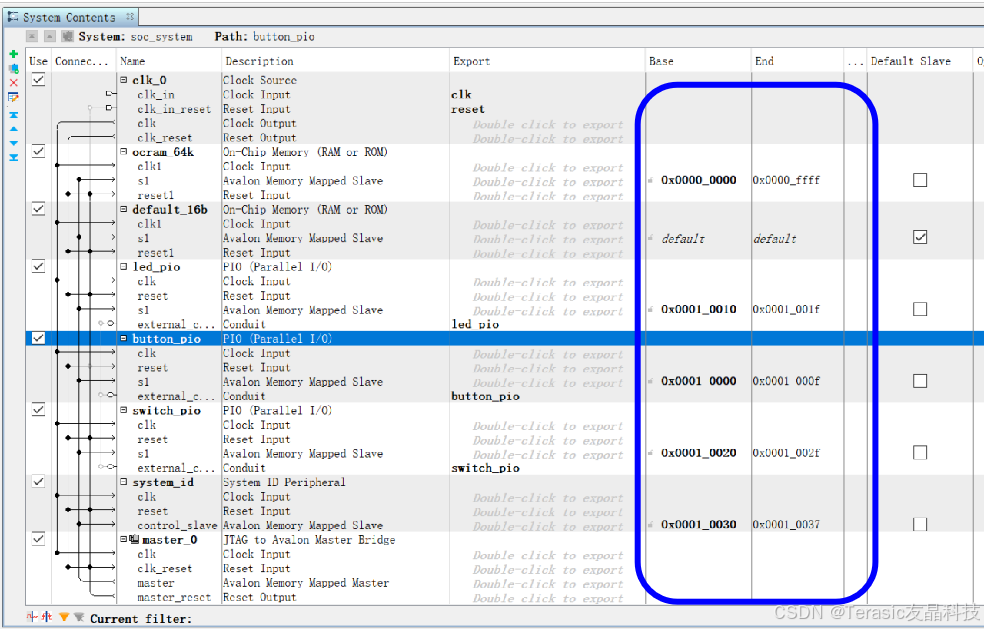

在系统内容窗口中,你可以定义系统的内存映射地址和范围。 每个内存映射的接口都有自己的映射地址,以供其访问其连接的从设备接口。 主接口的地址范围是其所有从设备接口地址的集合。 每个主接口最大地址空间是64位。 Platform Designer会自动分配从设备和主设备的基地址,你也可以选中更改。

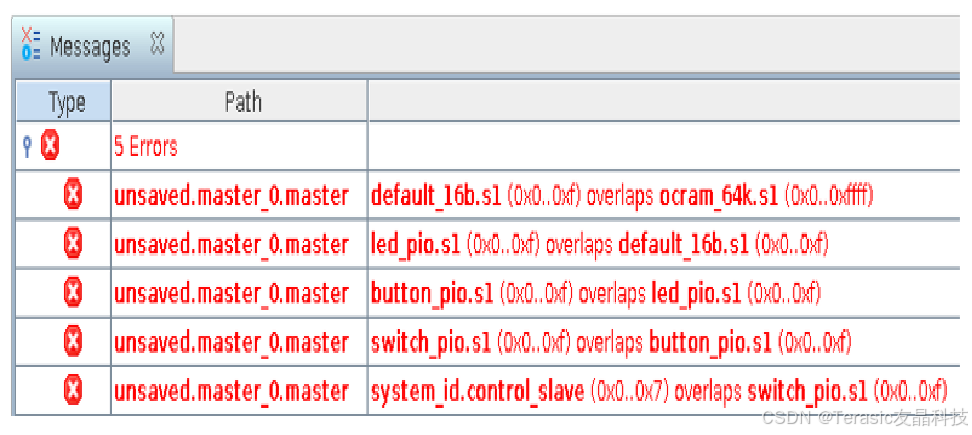

Platform Designer为每个从设备定义了一个初始地址范围,但最初它们是重叠的,在Messages窗口中提示了错误:

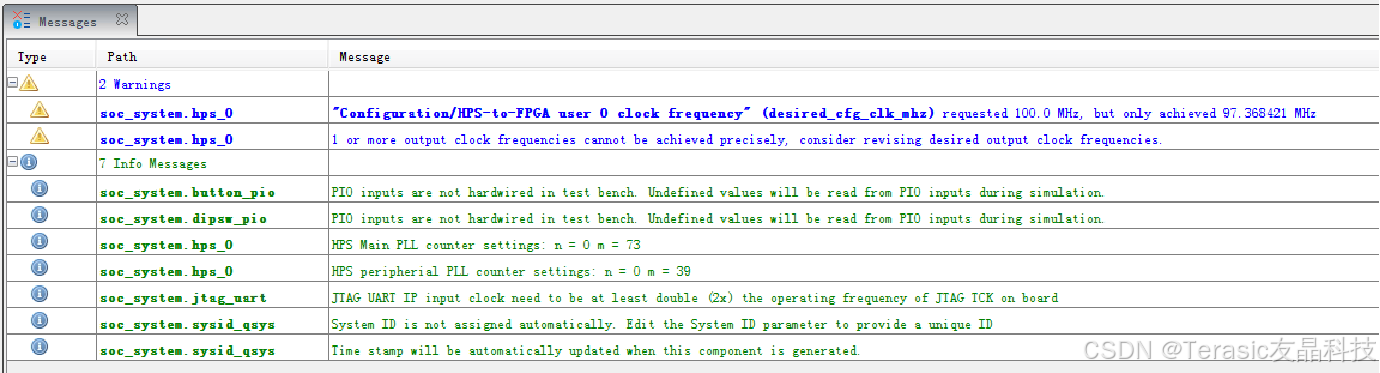

在Platform Designer用户界面的下方,是消息标签 这里列出了所有系统信息,警告和错误信息,要建设一个系统,所有的错误信息必须要消除。

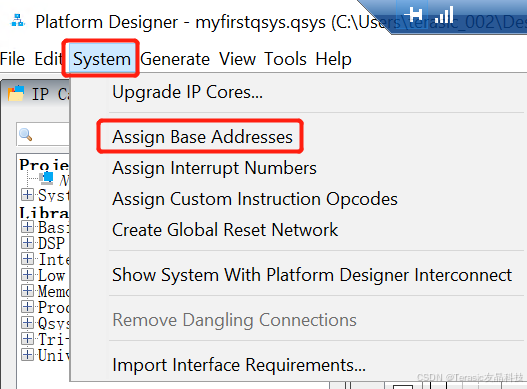

关于地址分配可以点击Platform Designer的菜单System——Assign Base Addresses进行自动分配,然后再手动修改。

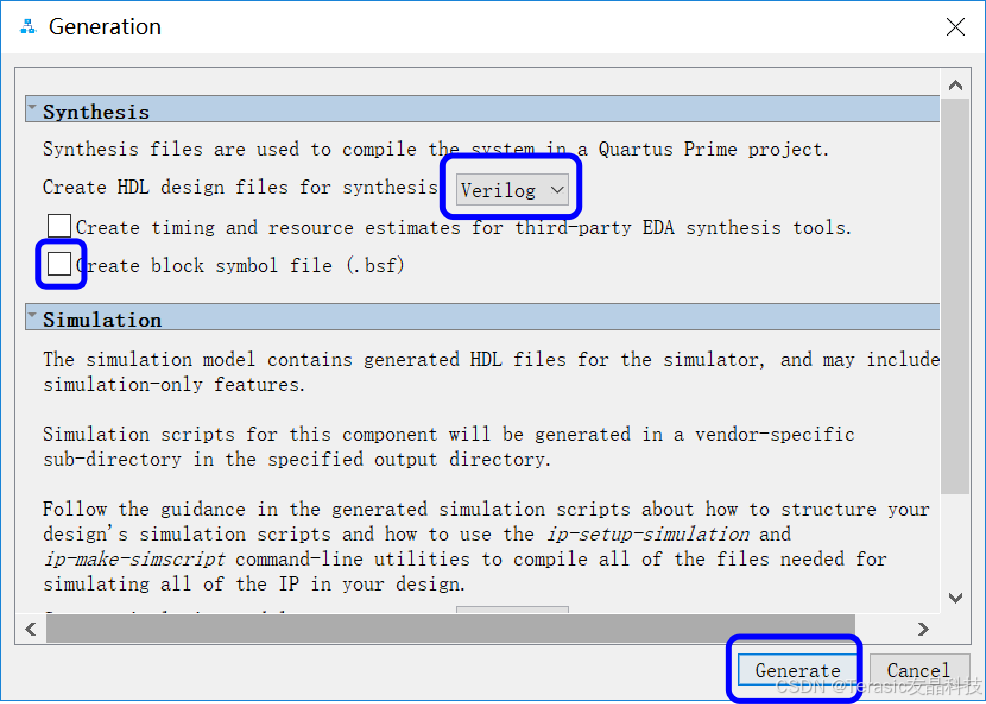

在Qsys界面的底部 单机产生HDL按钮可以打开产生窗口,可以选择硬件语言为VHDL或者Verilog 单击生成按钮,就可以产生Qsys系统硬件描述。

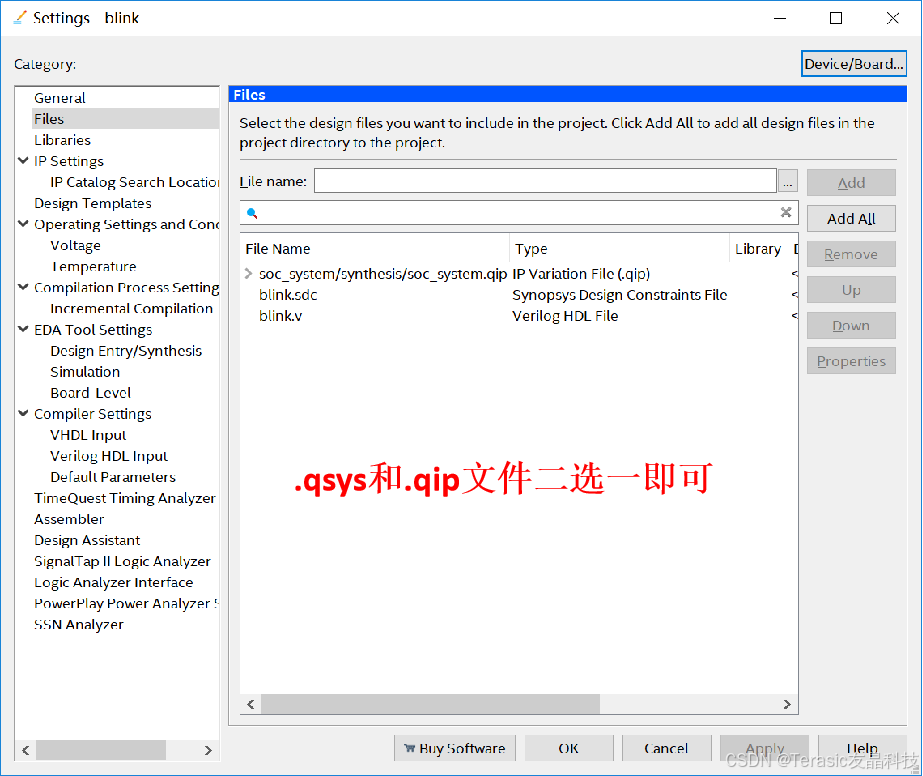

将Platform Designer系统整合到Intel Quartus软件工程 Assignments--Settings:

接下来就是在top level(顶层)文件里面例化这个Qsys系统,添加其他信号和该Qsys系统之间的连接,接下来就可以像my_first_fpga工程那一篇一样,进行 分析综合,引脚分配,编译,下载于

关于地址映射的完整教程参考:

https://www.cnblogs.com/DoreenLiu/articles/17930222.html

关于my_first_qsys工程(纯RTL)详细步骤请参考下文。

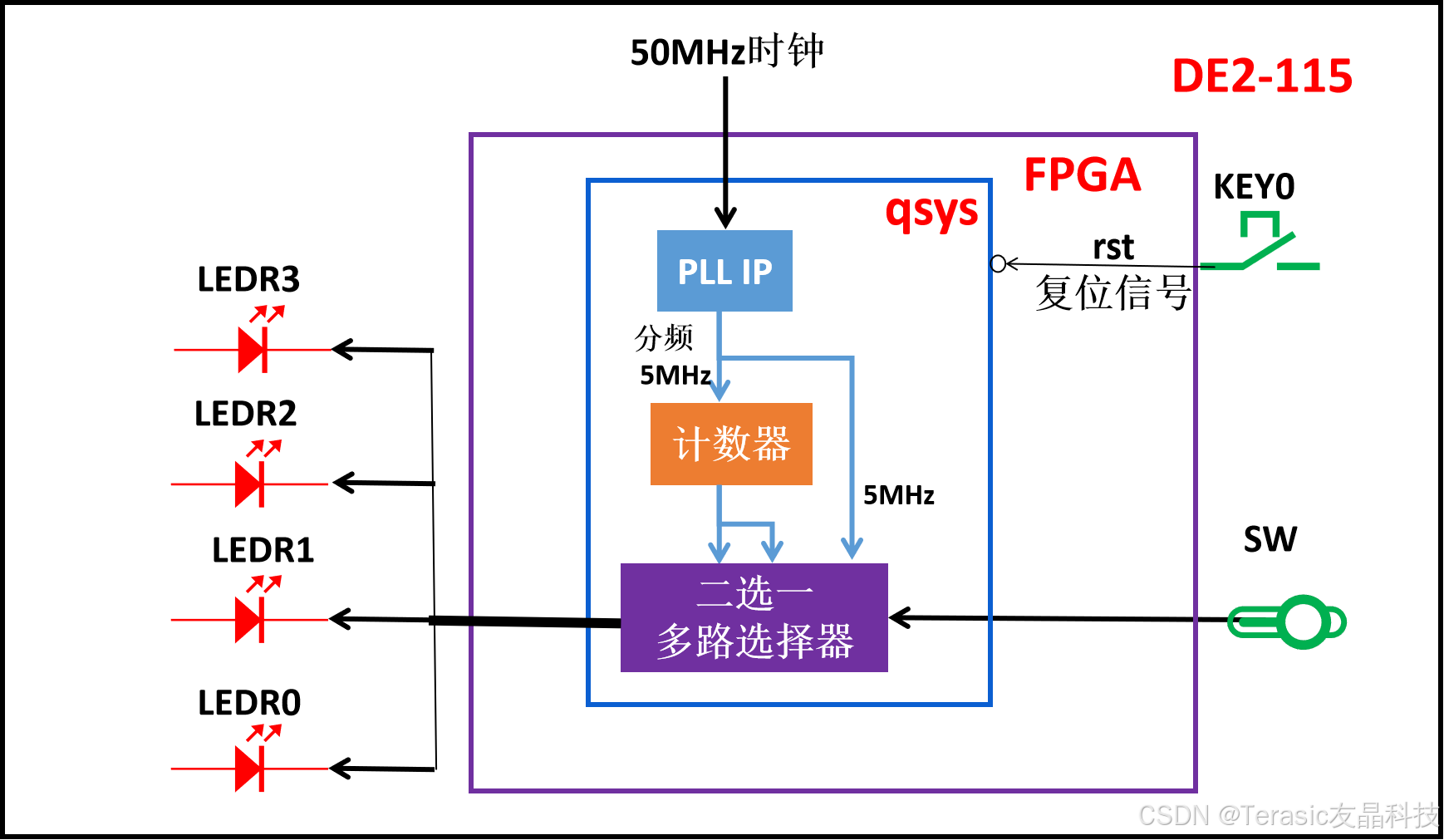

五、实验任务框图

六、my_first_qsys工程具体步骤参考

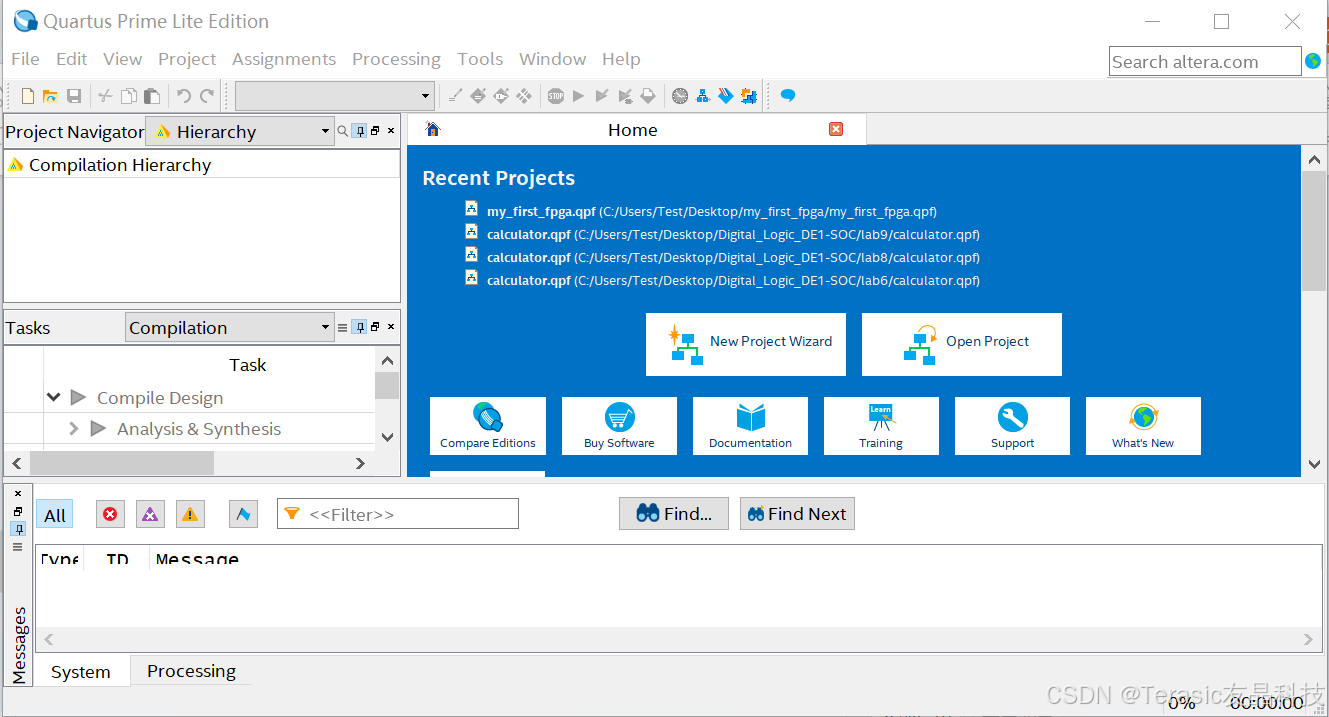

1. 创建Qsys系统

双击Quartus图标打开该软件:

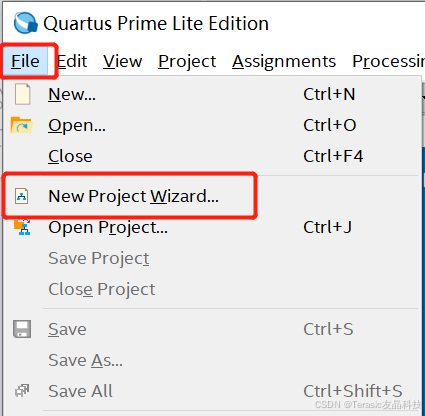

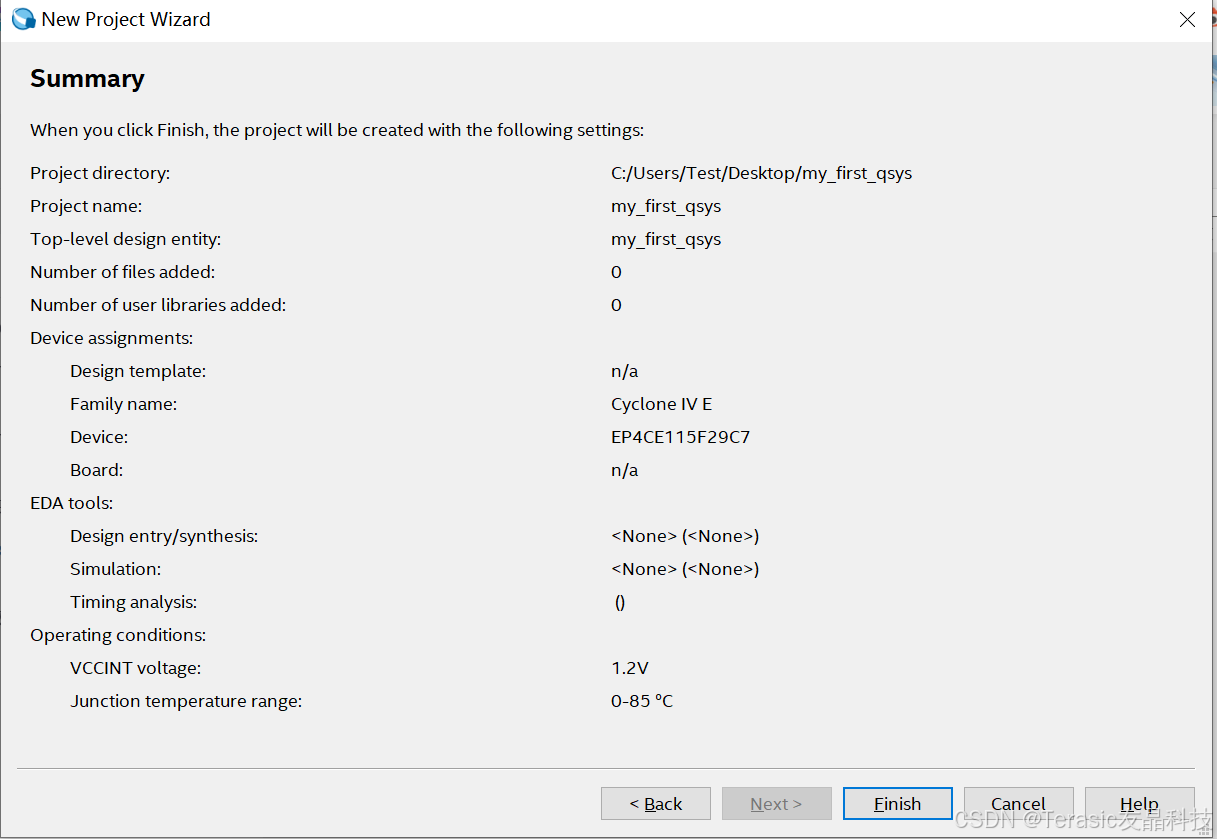

点击File——New Project Wizard来新建工程:

点击Next:

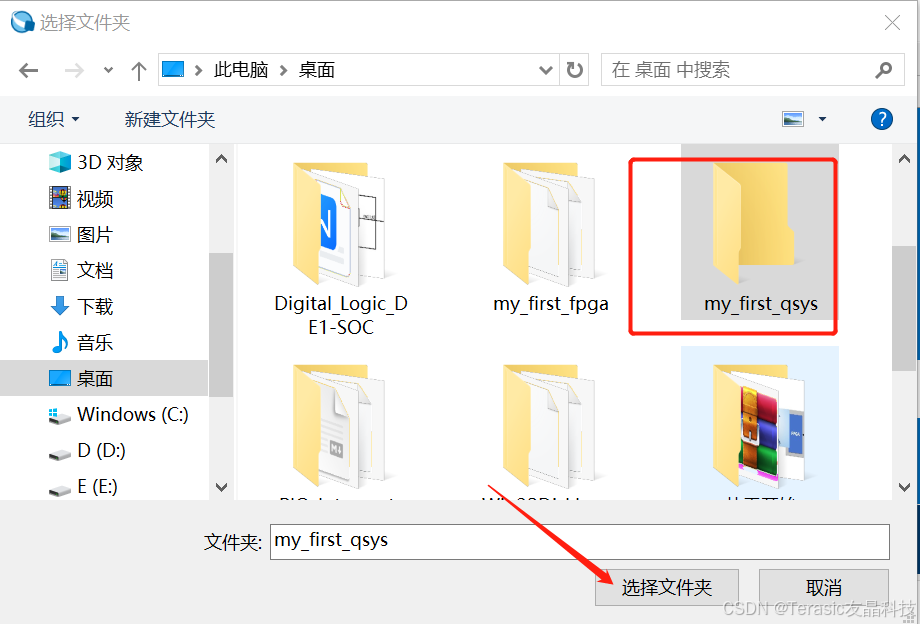

在桌面新建一个my_first_qsys文件夹,然后将工程路径指定到这个文件夹:

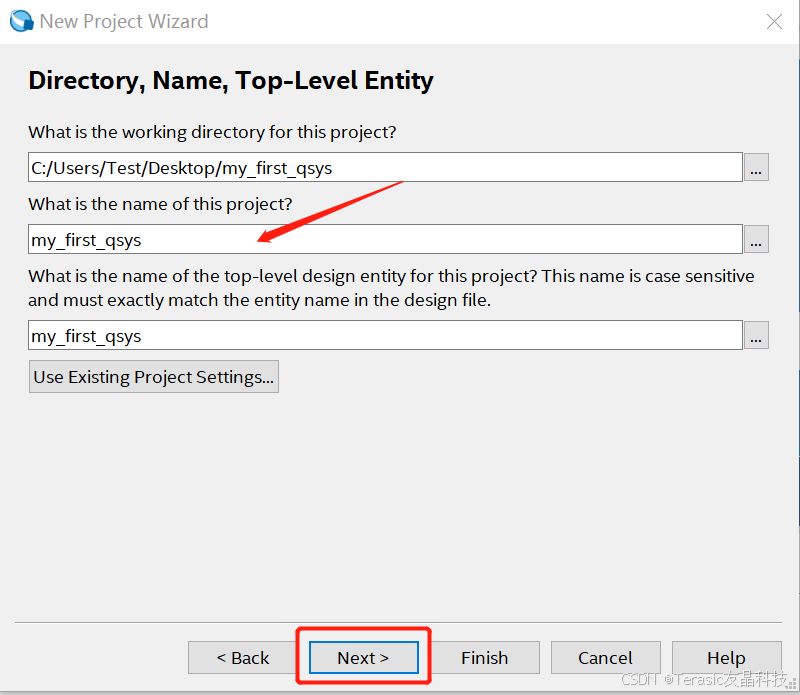

工程名称也设定为my_first_qsys:

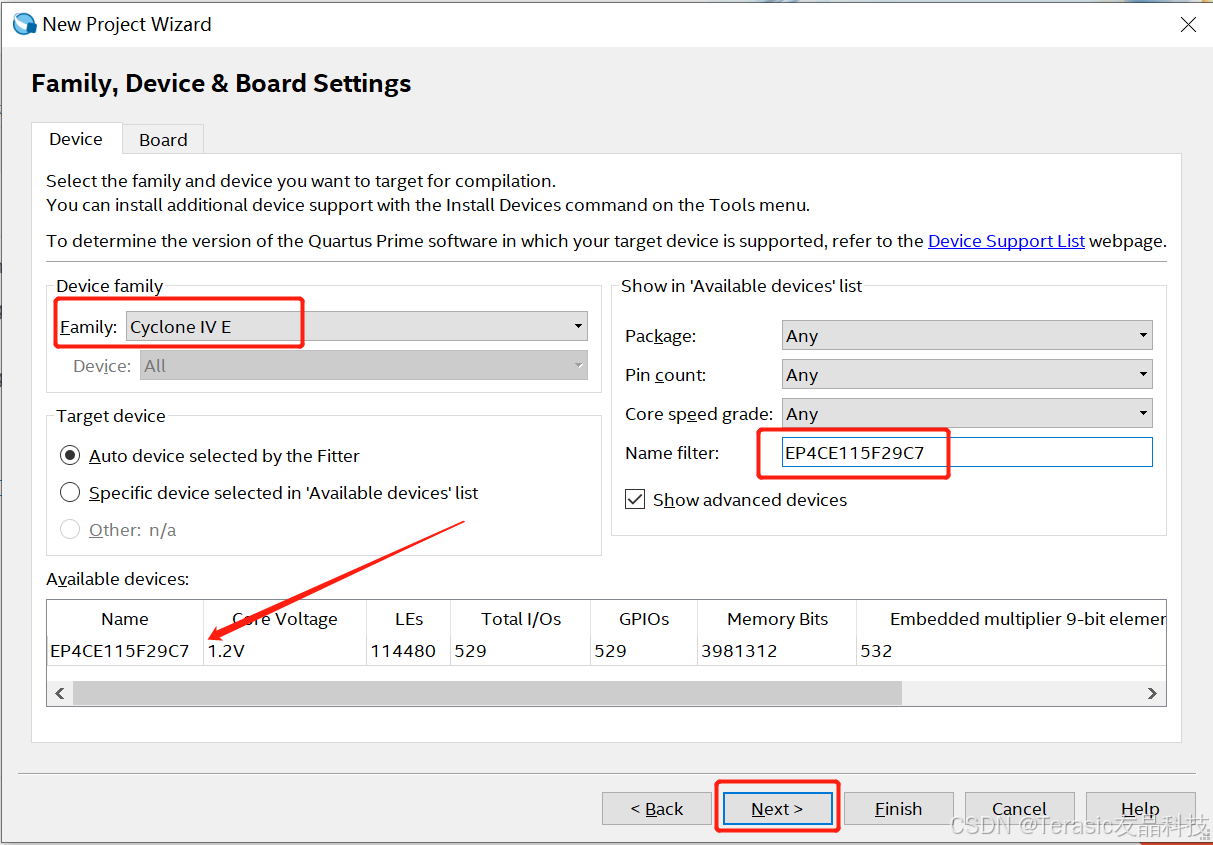

然后点击3次Next,筛选器件EP4CE115F29(DE2-115开发板正好是这个FPGA器件):

然后再点击2次Next,然后点击Finish完成工程创建:

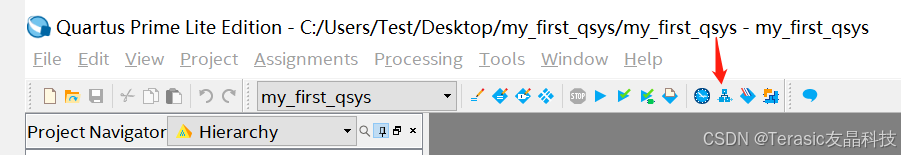

点击Platform Designer图标:

弹出窗口:

弹出窗口:

2. 添加Intel IP

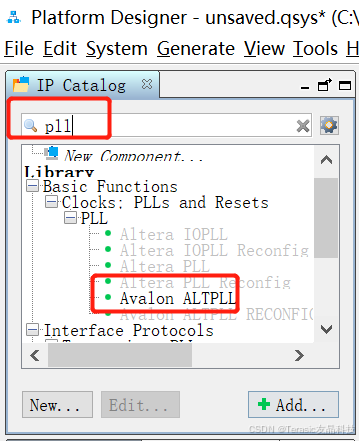

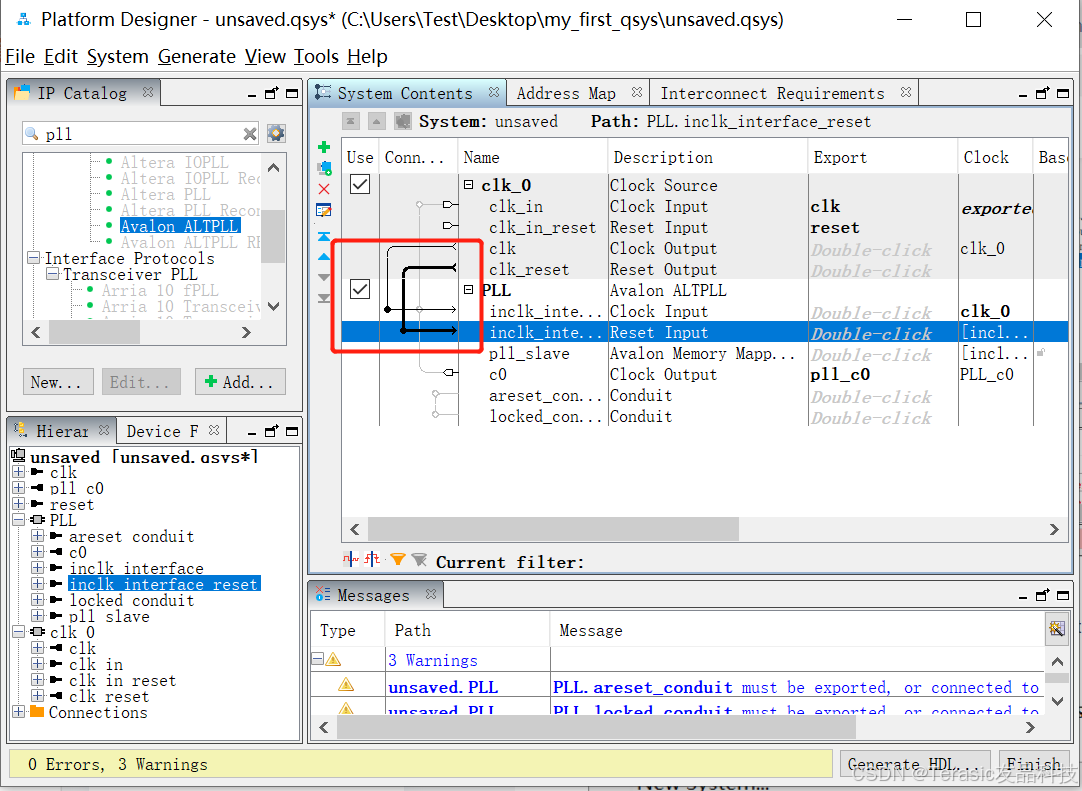

这时qsys打开一个未保存的系统,其中一个时钟源组件已经实例化。要添加另一个IP块,请使用左侧列中的IP Catalog窗格。在搜索栏中,开始键入pll,然后双击Avalon ALPLL添加一个PLL 组件:

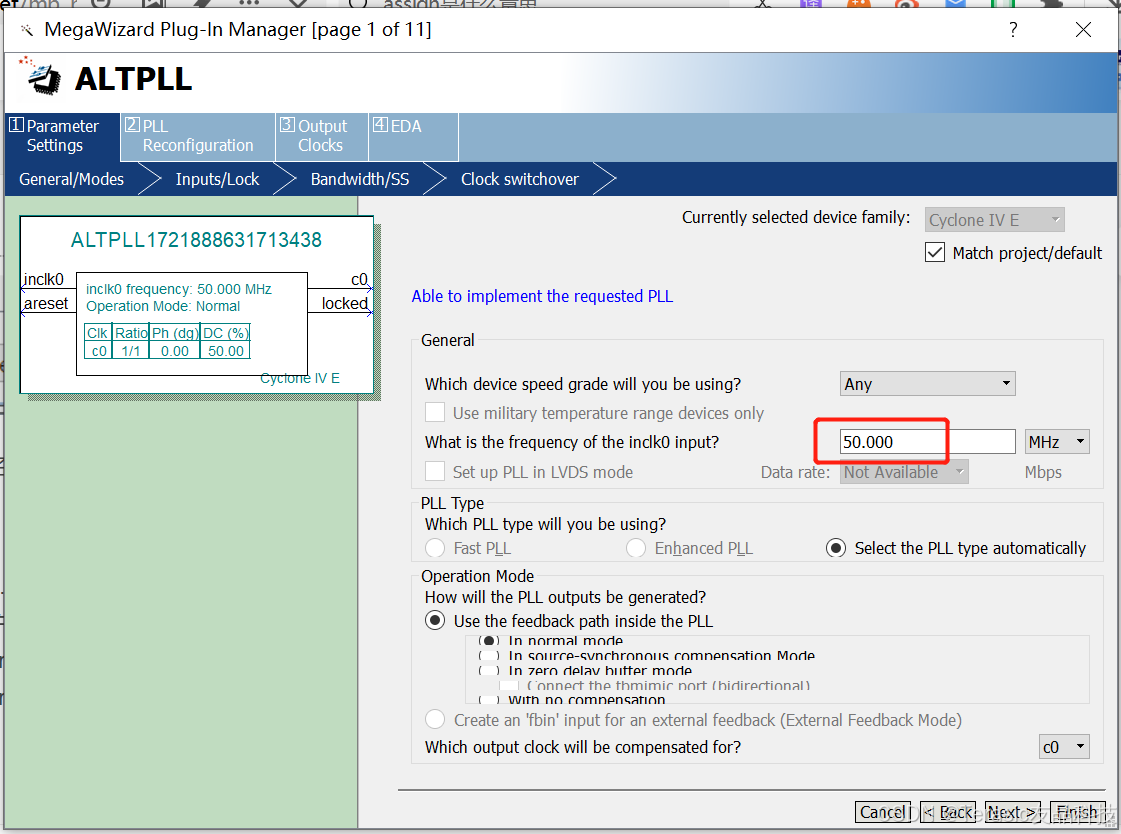

设置输入时钟50MHz,

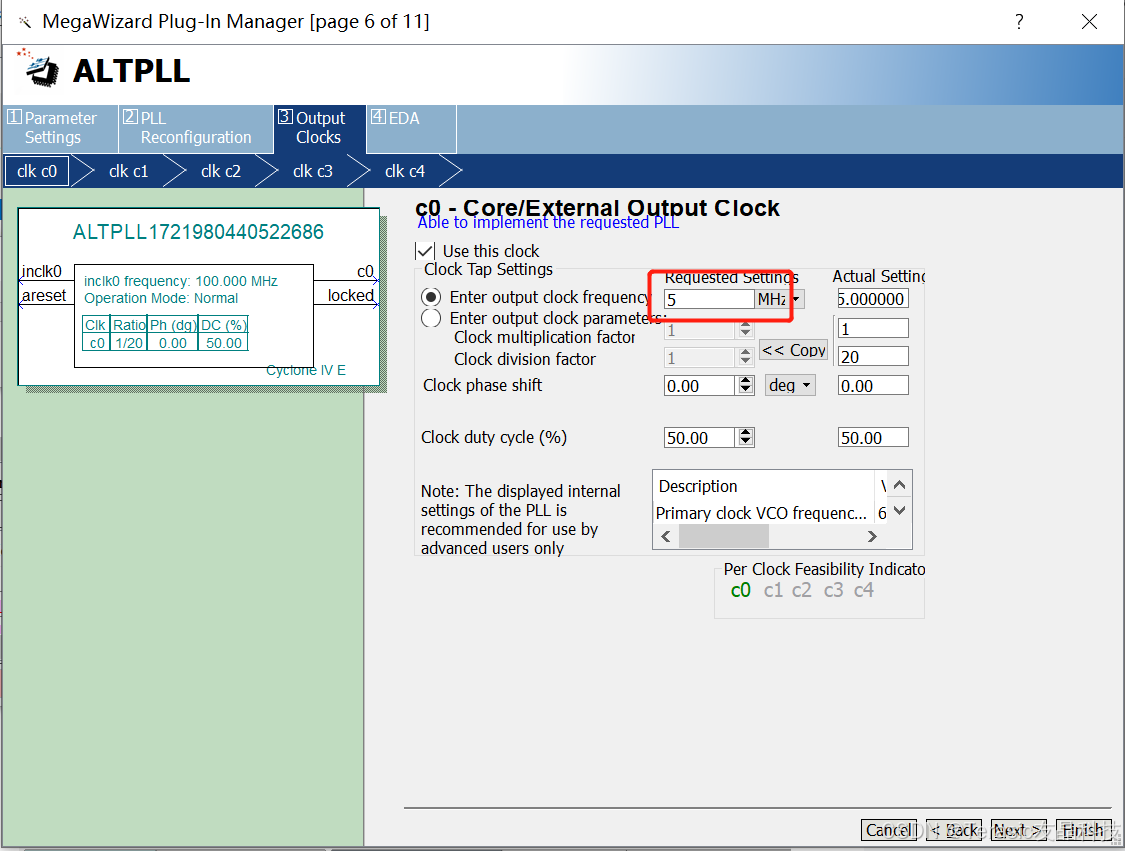

输出5HZ,

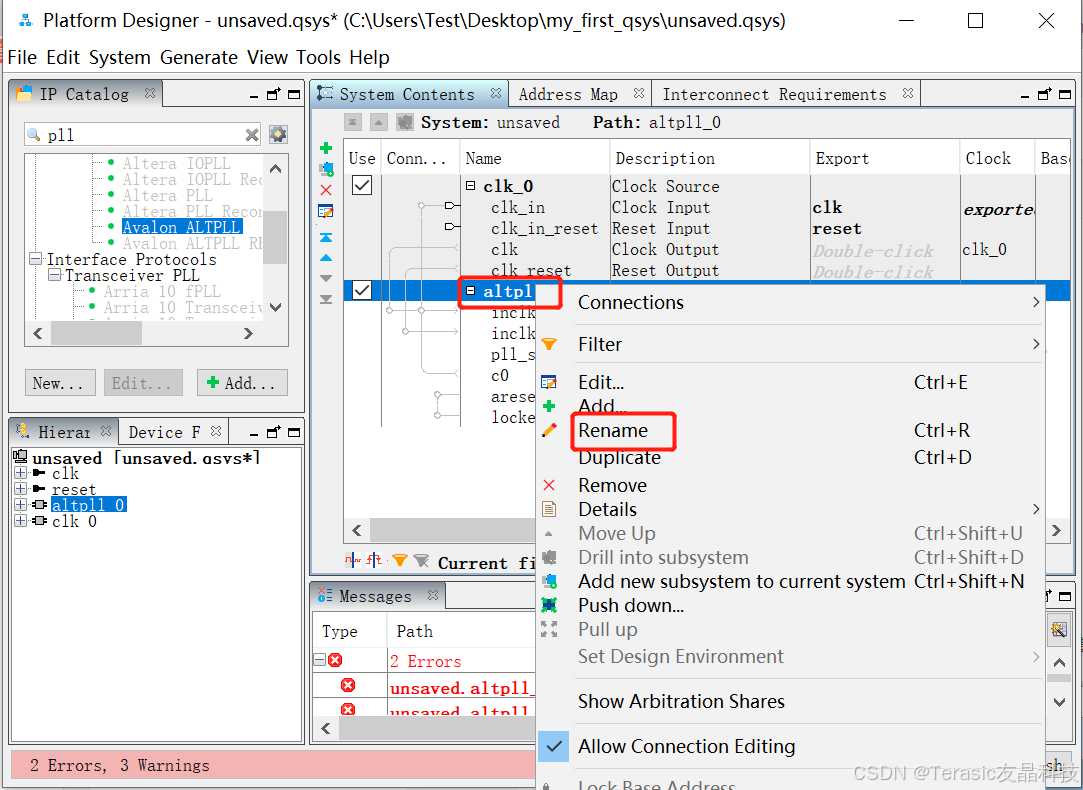

重命名为PLL,

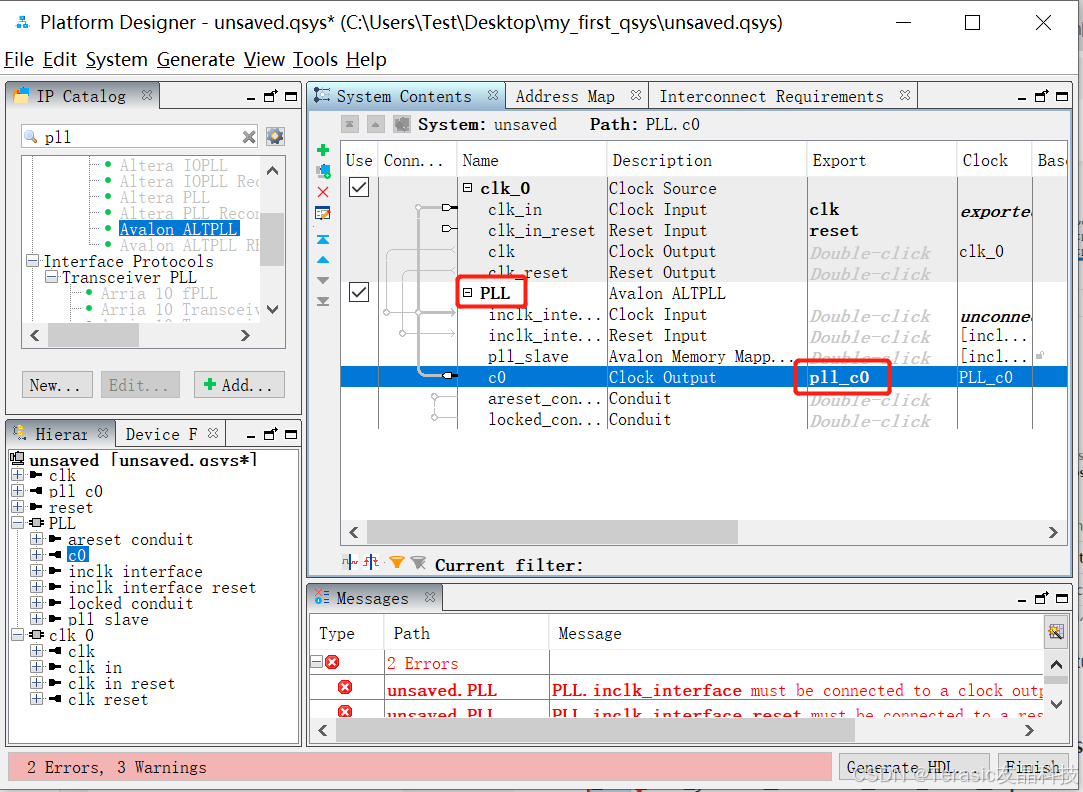

然后双击PLL 的c0信号的Export列将该信号导出为pll_c0:

为PLL模块IP连接时钟和复位信号。

为PLL模块IP连接时钟和复位信号。

3. 添加自定义IP

继续添加IP。这次添加用户自定义IP。

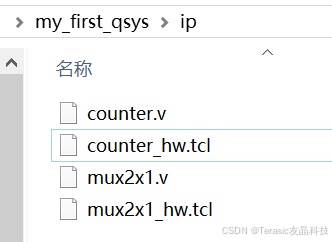

按照教程Platform Designer 自定义IP(用于纯RTL设计)-CSDN博客 制作mux2x1 IP和counter IP,IP完成以后拷贝IP的2个文件到my_first_qsys工程目录下:

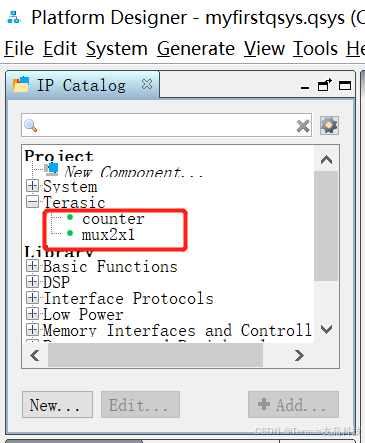

这时Platform Designer IP Catalog窗口会出现mux2x1和counter 的IP(如果没有出现就要检查两个IP的.tcl文件内,.v文件路径有没有修改成相对路径):

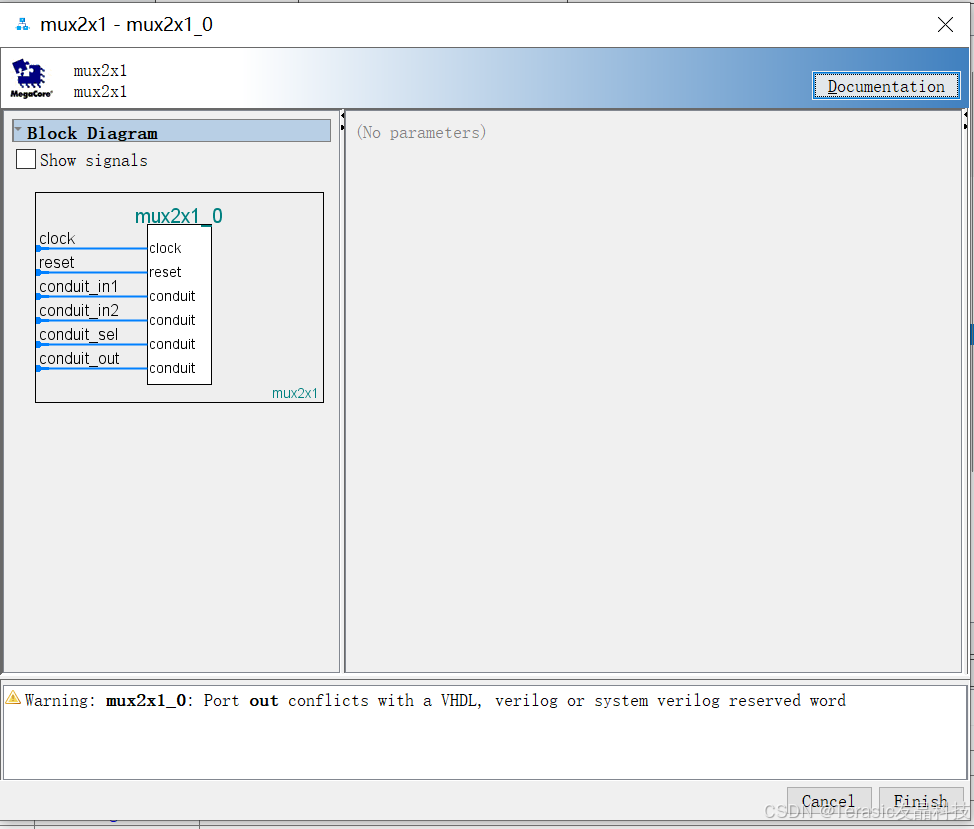

双击mux2x1将该自定义IP 添加到Platform Designer系统当中:

直接点击Finish完成mux2x1 IP 的添加:

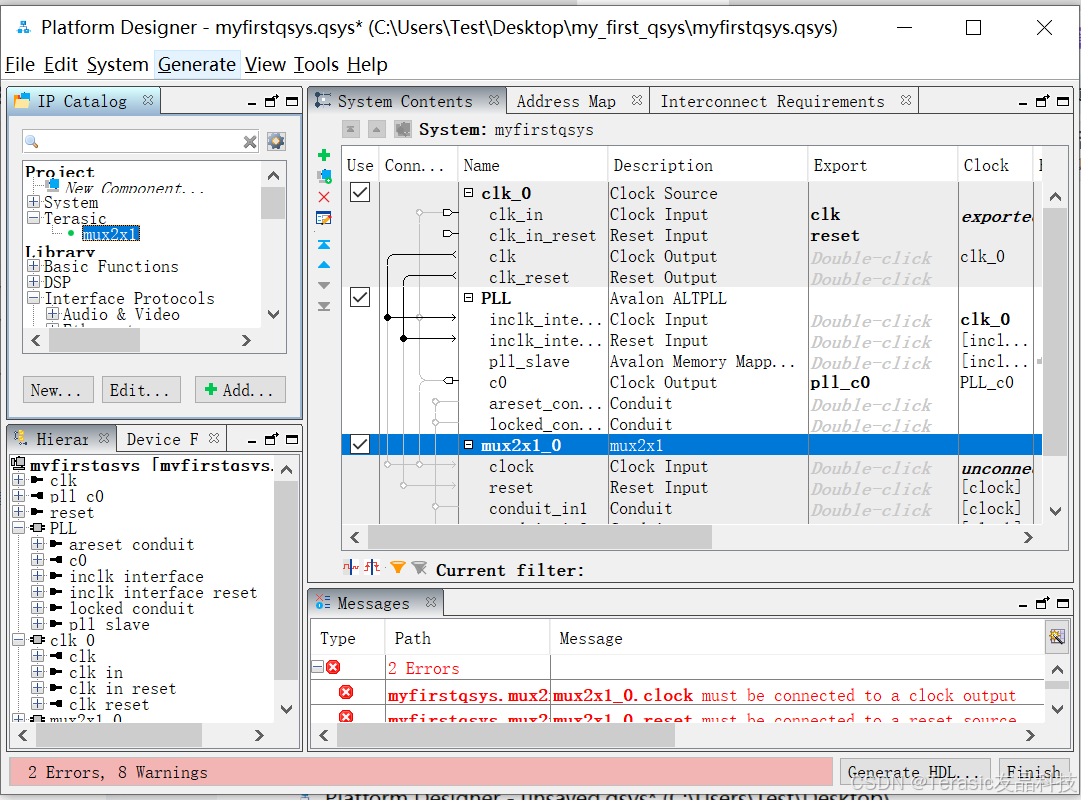

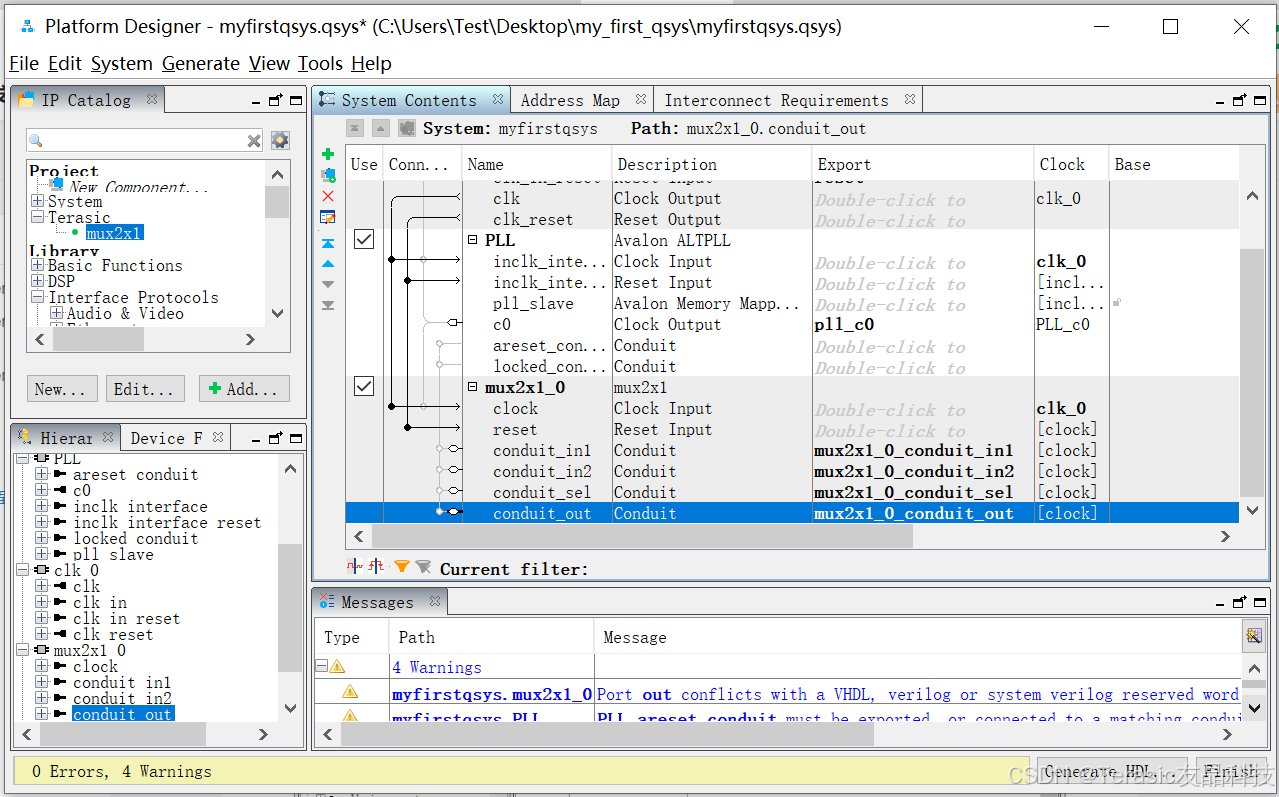

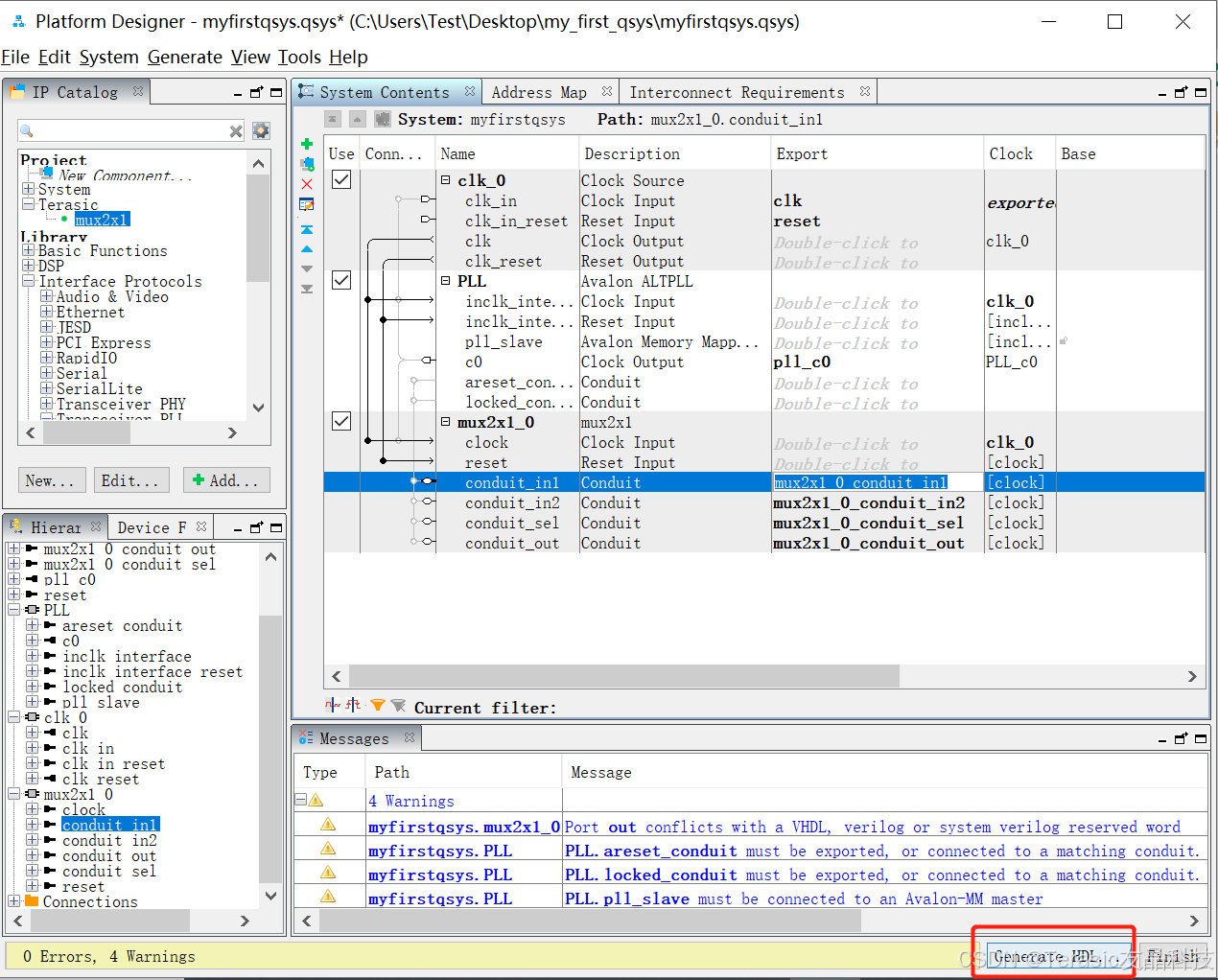

为mux2x1 IP 连接系统的时钟和复位信号。然后导出mux2x1的这些信号:mux2x1_0_conduit_in1、mux2x1_0_conduit_in2、mux2x1_0_conduit_sel、mux2x1_0_conduit_out.

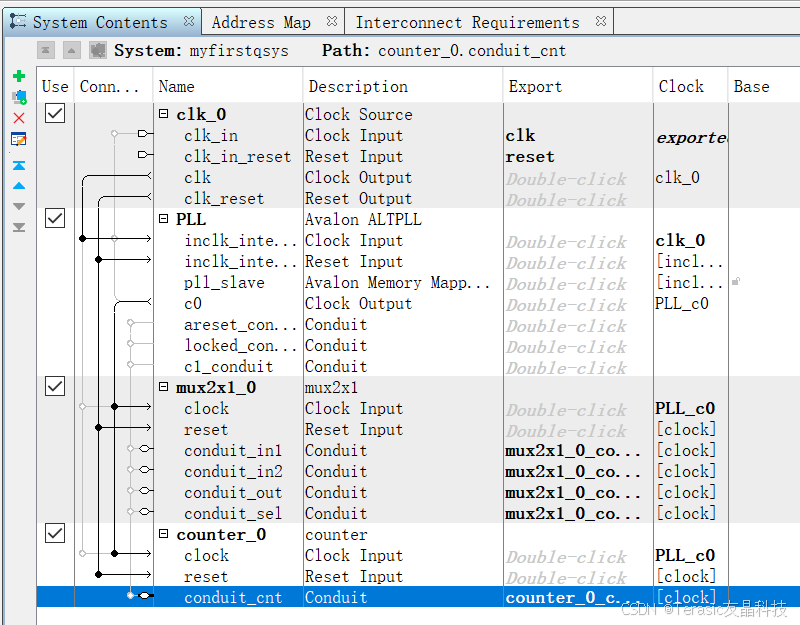

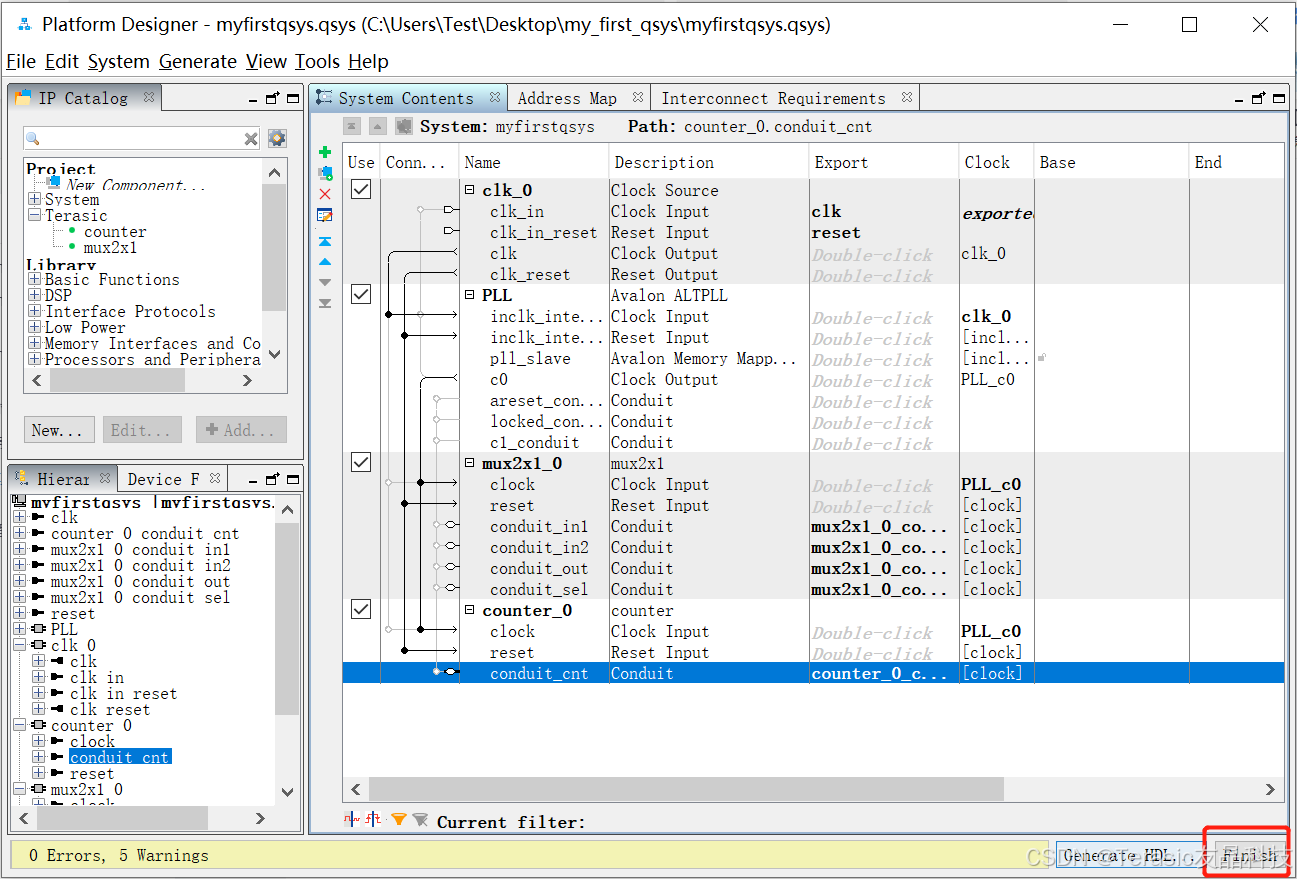

用同样的方法继续添加counter IP。连接时钟和复位信号,并导出counter_0_conduit_cnt信号:

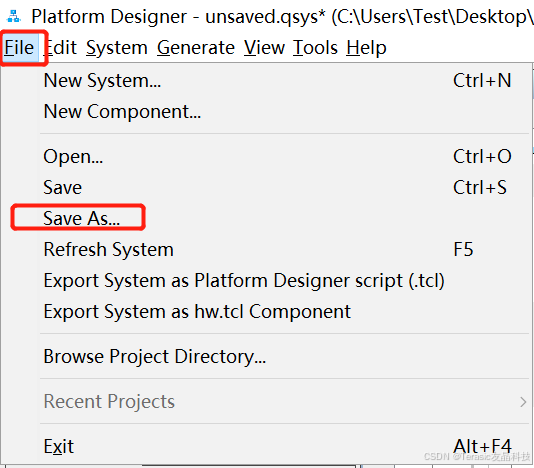

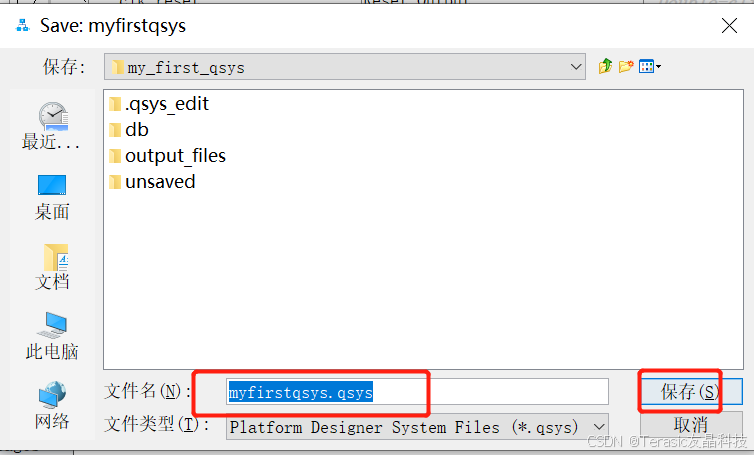

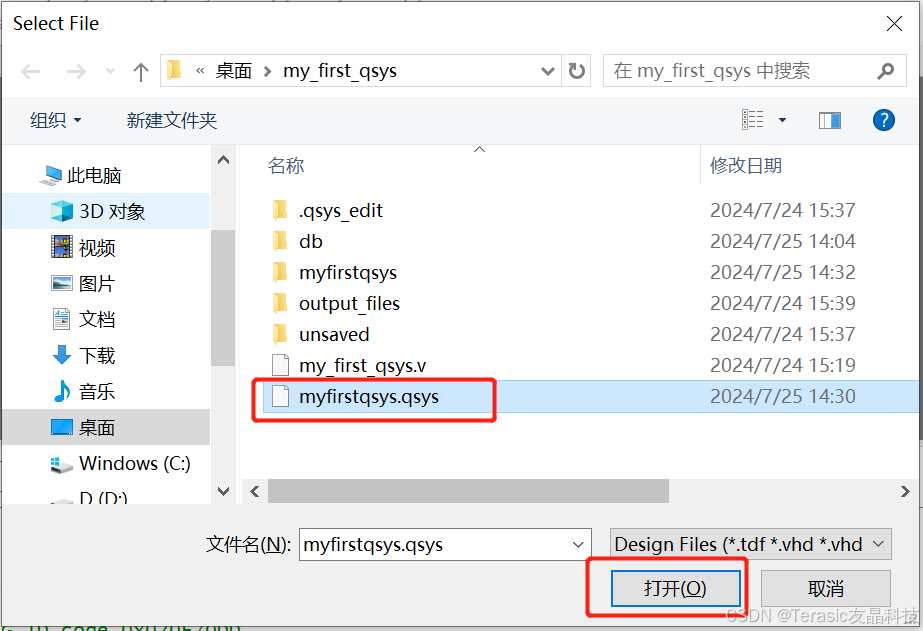

Qsys系统设置已经完成,现在是时候将其整合到Intel Quartus软件工程中了。首先,保存Qsys系统并命名为myfirstqsys.qsys。

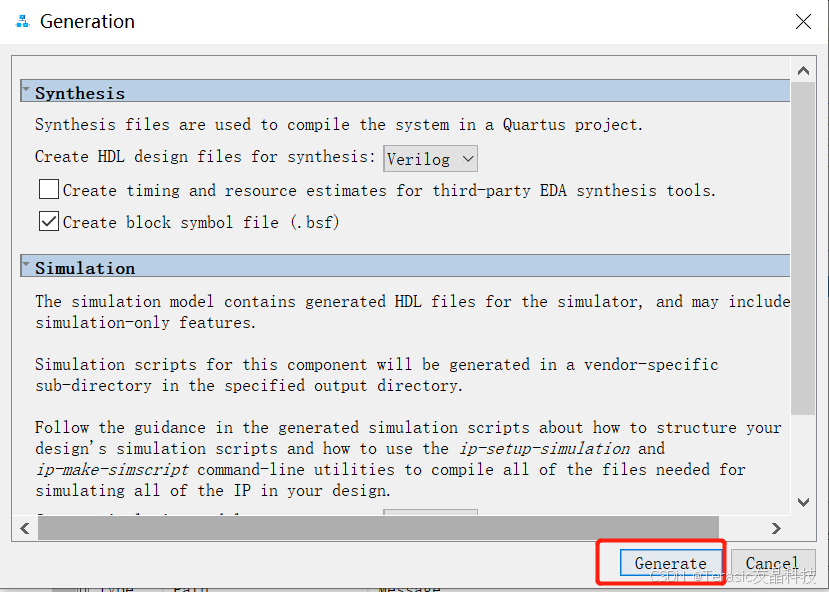

当保存完成时关闭保存窗口。然后点击Generate HDL...。

打开Generate窗口,然后单击Generate按钮。

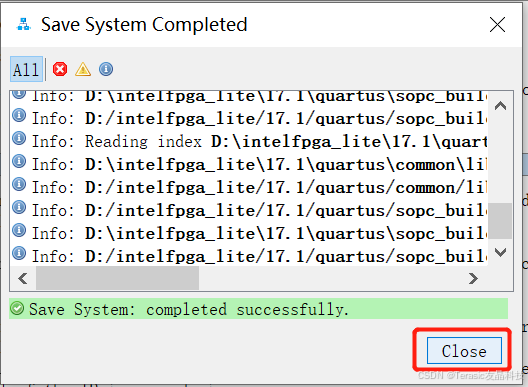

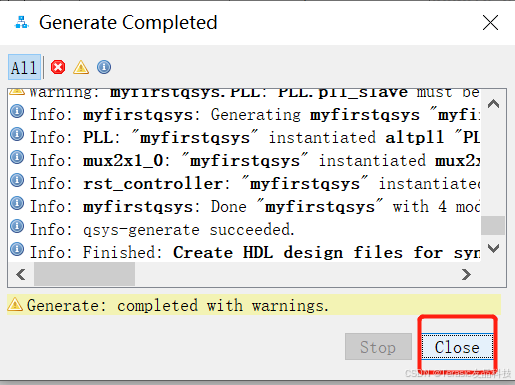

Qsys现在将为IP和互连生成HDL文件。完成后,单击Close按钮。

然后单击Qsys窗口右下角的Finish按钮。这将关闭Qsys。

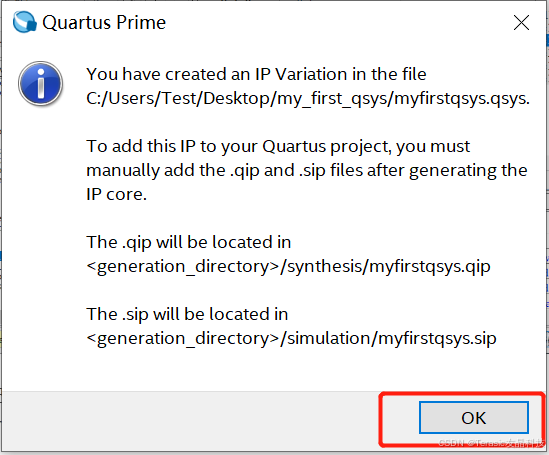

接着将出现提示.qip文件添加到Intel Quartus软件工程的说明。

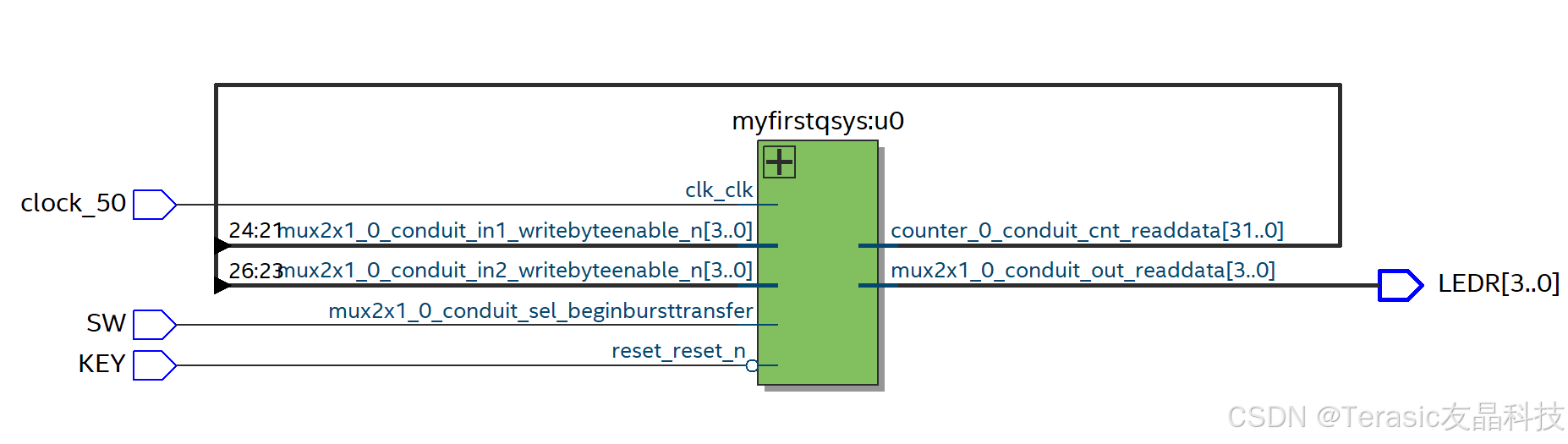

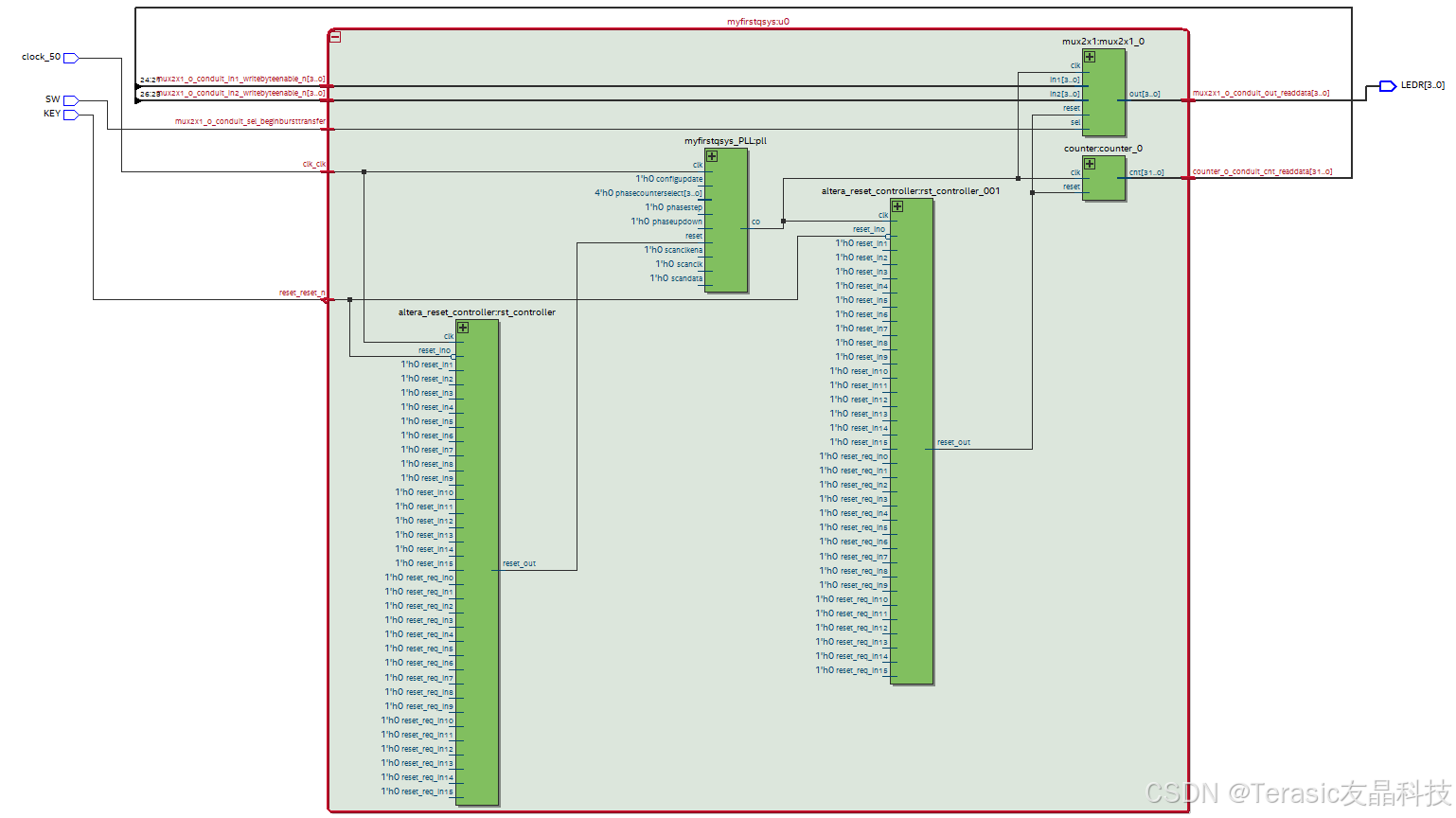

Qsys系统的RTL视图(这个需要整个工程分析综合以后才能查看到):

-

- 将Qsys系统整合到Intel Quartus软件工程中

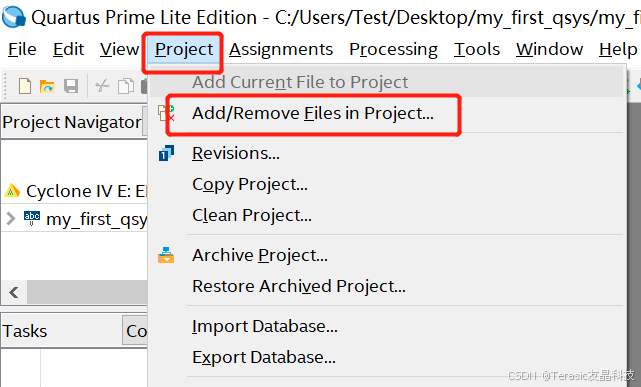

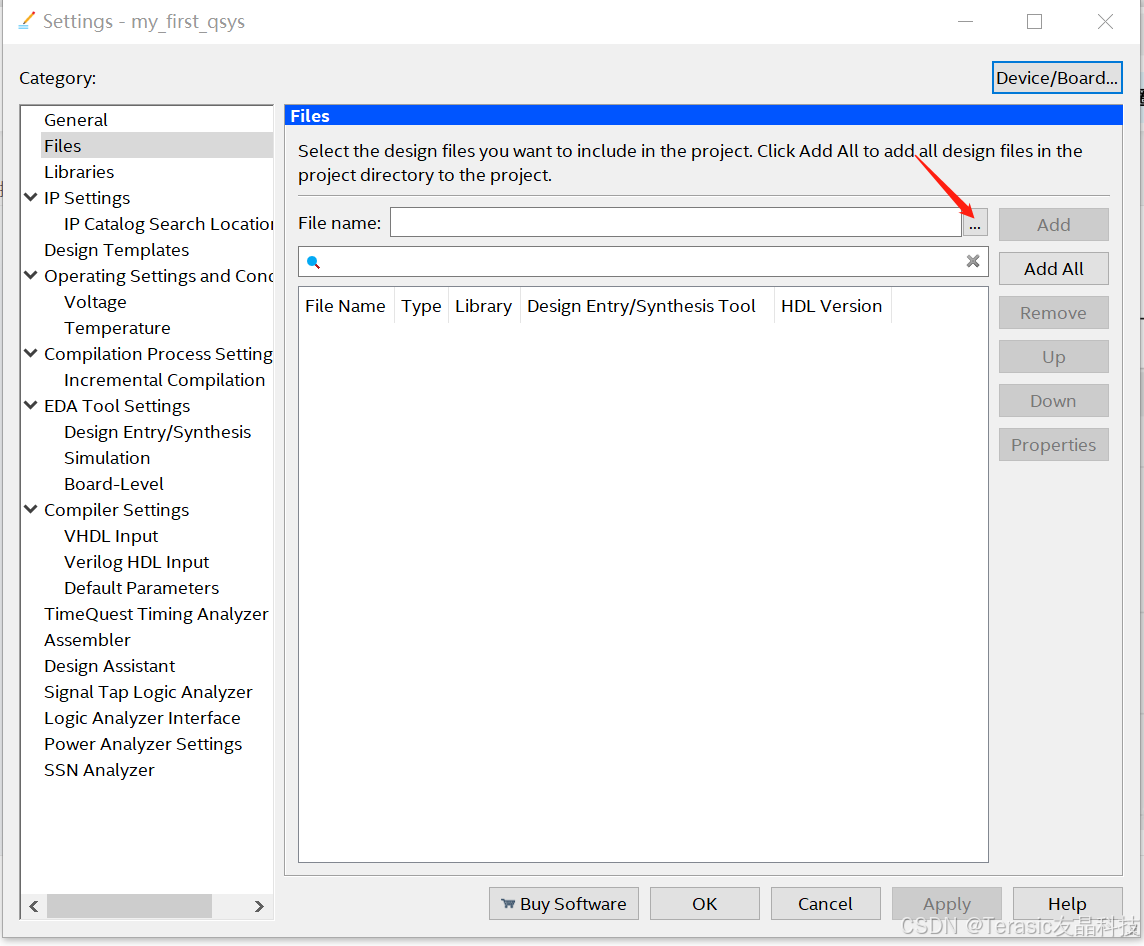

本节将描述如何将新生成的Qsys输出合并到my_first_qsys工程中。

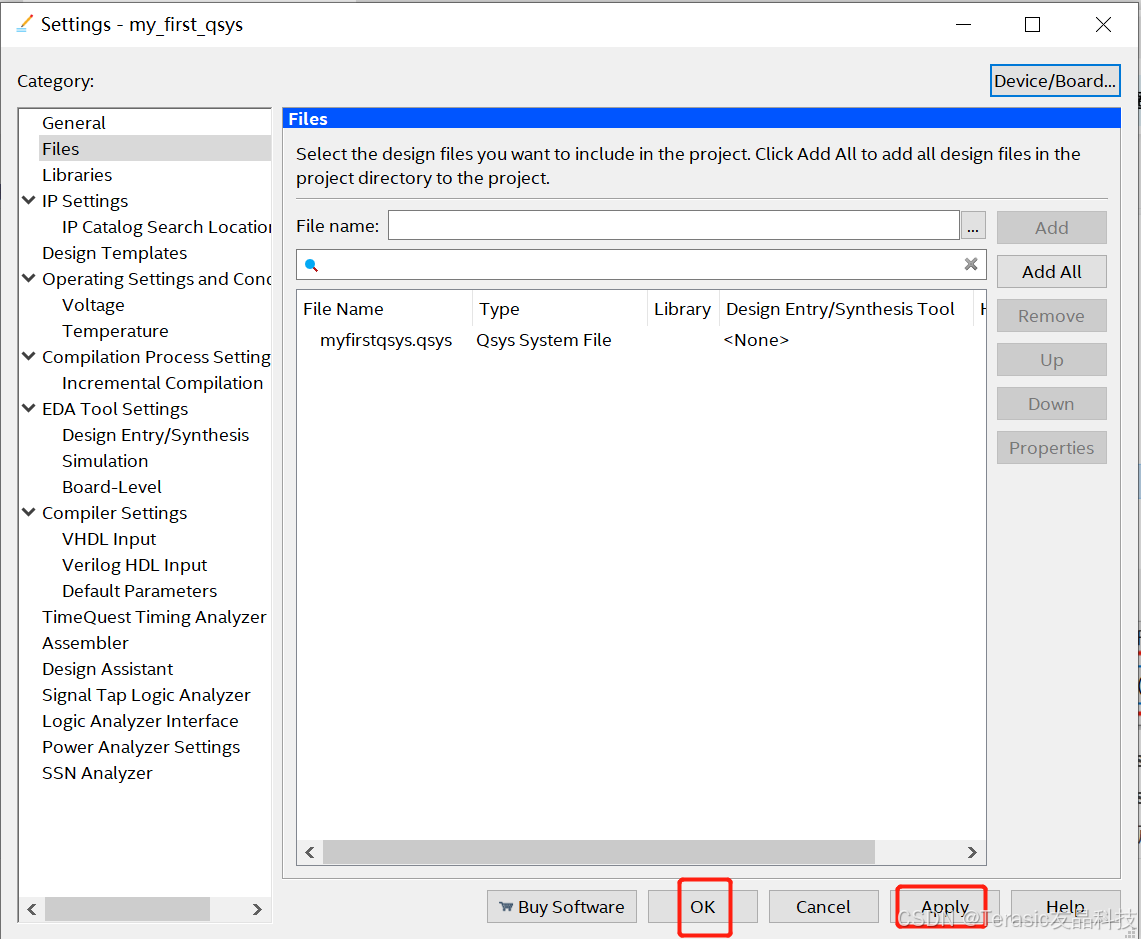

首先将Qsys生成的.qsys文件添加到my_first_qsys工程中。

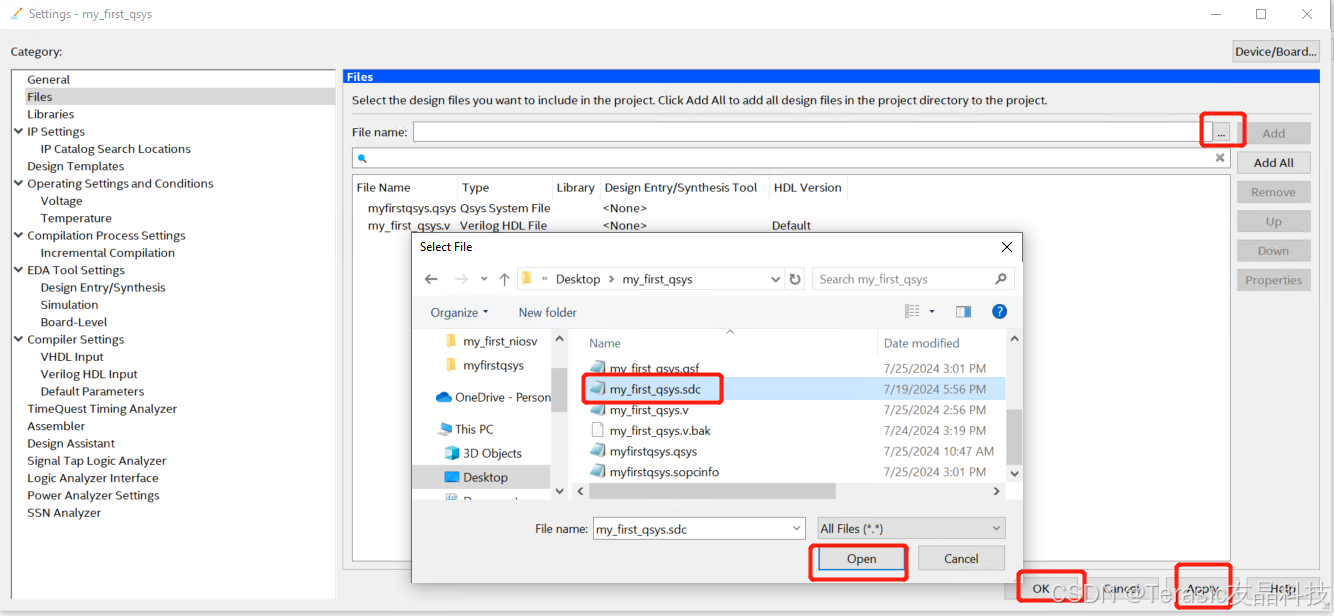

点击File Name的...按钮:

选择myfirstqsys.qsys文件然后点击打开:

然后点击Apply和OK按钮,这样就把.qsys文件添加到工程当中去了:

然后点击Apply和OK按钮,这样就把.qsys文件添加到工程当中去了:

4. 创建顶层文件

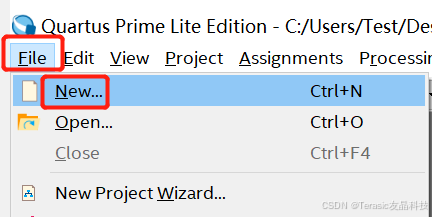

新建Top文件:

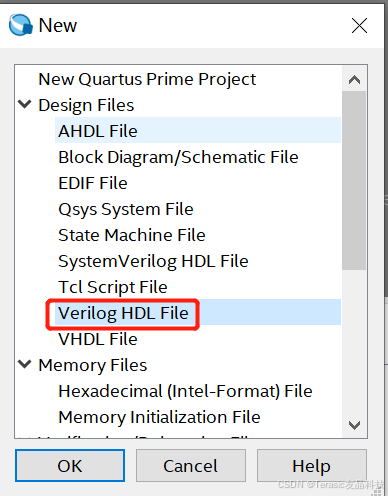

选择新建Verilog HDL File:

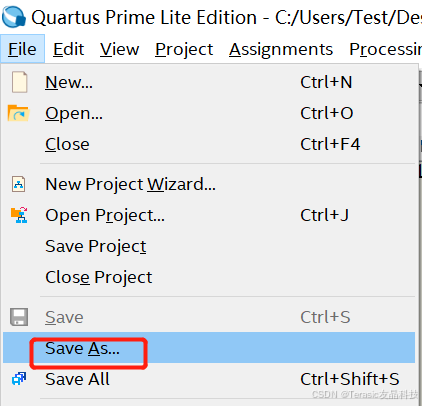

点击File——Save as将.v文件保存为my_first_qsys.v:

在my_first_qsys工程的Top Level文件中敲入如下代码:

module my_first_qsys(

input clock_50,

input KEY,

input SW,

output [3:0] LEDR

);

endmodule接下来是在顶层文件my_first_qsys.v当中例化qsys系统。

Qsys为生成的系统创建一个实例化模板文件,在本例中,它是Intel Quartus软件工程my_first_qsys\myfirstqsys文件夹中的myfirstqsys_inst.v文件。使用它可以很方便地在顶层HDL文件中实例化Qsys生成的系统。

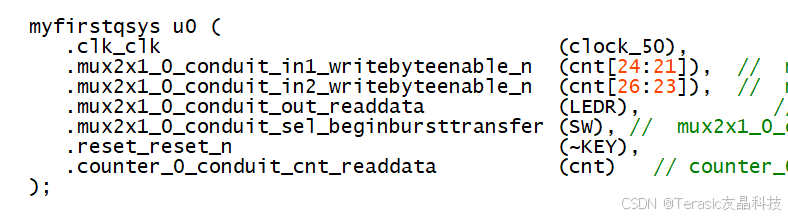

myfirstqsys_inst.v文件内容如下:

myfirstqsys u0 (

.clk_clk (<connected-to-clk_clk>), // clk.clk

.mux2x1_0_conduit_in1_writebyteenable_n (<connected-to-mux2x1_0_conduit_in1_writebyteenable_n>), // mux2x1_0_conduit_in1.writebyteenable_n

.mux2x1_0_conduit_in2_writebyteenable_n (<connected-to-mux2x1_0_conduit_in2_writebyteenable_n>), // mux2x1_0_conduit_in2.writebyteenable_n

.mux2x1_0_conduit_out_readdata (<connected-to-mux2x1_0_conduit_out_readdata>), // mux2x1_0_conduit_out.readdata

.mux2x1_0_conduit_sel_beginbursttransfer (<connected-to-mux2x1_0_conduit_sel_beginbursttransfer>), // mux2x1_0_conduit_sel.beginbursttransfer

.reset_reset_n (<connected-to-reset_reset_n>), // reset.reset_n

.counter_0_conduit_cnt_readdata (<connected-to-counter_0_conduit_cnt_readdata>) // counter_0_conduit_cnt.readdata

);

将myfirstqsys_inst.v文件内容拷贝到my_first_qsys.v, 并进行修改。

更新的my_first_qsys.v文件内容具体如下:

module my_first_qsys(

input clock_50,

input KEY,

input SW,

output [3:0] LEDR

);

wire [31:0] cnt;

myfirstqsys u0 (

.clk_clk (clock_50), // clk.clk

.mux2x1_0_conduit_in1_writebyteenable_n (cnt[24:21]), // mux2x1_0_conduit_in1.writebyteenable_n

.mux2x1_0_conduit_in2_writebyteenable_n (cnt[26:23]), // mux2x1_0_conduit_in2.writebyteenable_n

.mux2x1_0_conduit_out_readdata (LEDR), // mux2x1_0_conduit_out.readdata

.mux2x1_0_conduit_sel_beginbursttransfer (SW), // mux2x1_0_conduit_sel.beginbursttransfer

.reset_reset_n (~KEY), // reset.reset_n

.counter_0_conduit_cnt_readdata (cnt) // counter_0_conduit_cnt.readdata

);

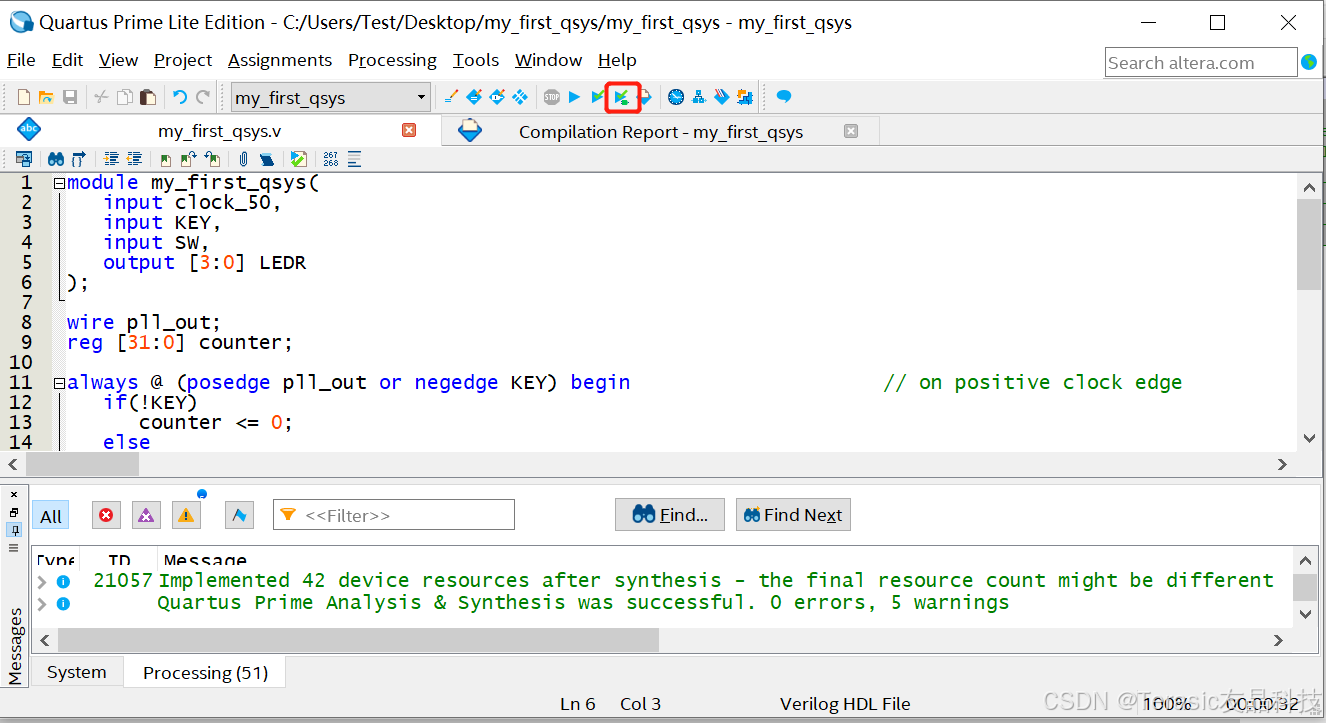

endmodule单击工具栏上的Start Analysis & Elaboration按钮,让Intel Quartus软件处理新的HDL。当Intel Quartus软件处理Qsys生成的系统时,将会有更多的消息。此过程将识别HDL源文件中的任何错误或它们在项目中的配置方式,并通知Intel Quartus软件我们在顶层模块中声明的新的顶层端口。

这时候就可以查看系统RTL Viewer视图了,图可以参见前文。

5. 引脚分配

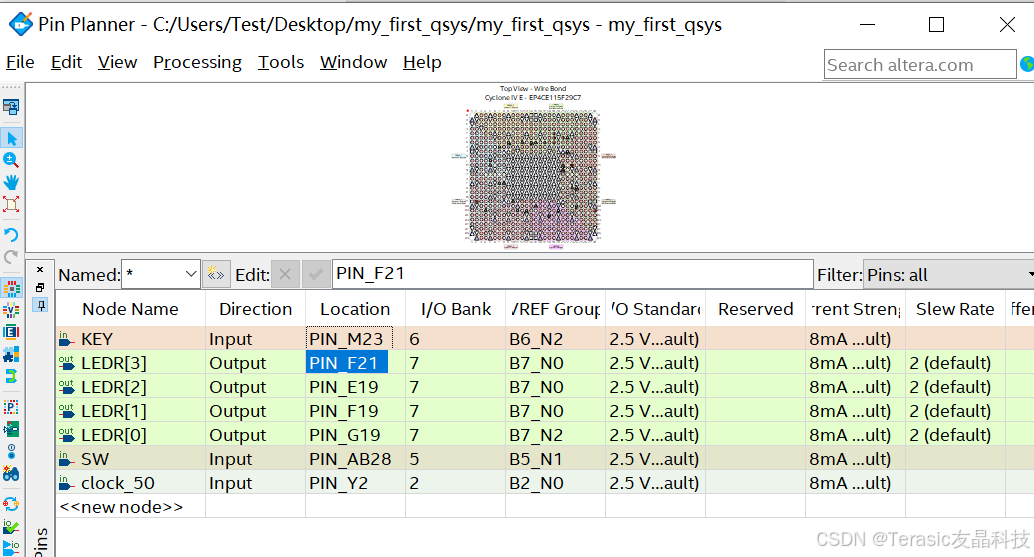

在Assignments菜单中,打开Pin Planner工具,按下图中的方式分配引脚。

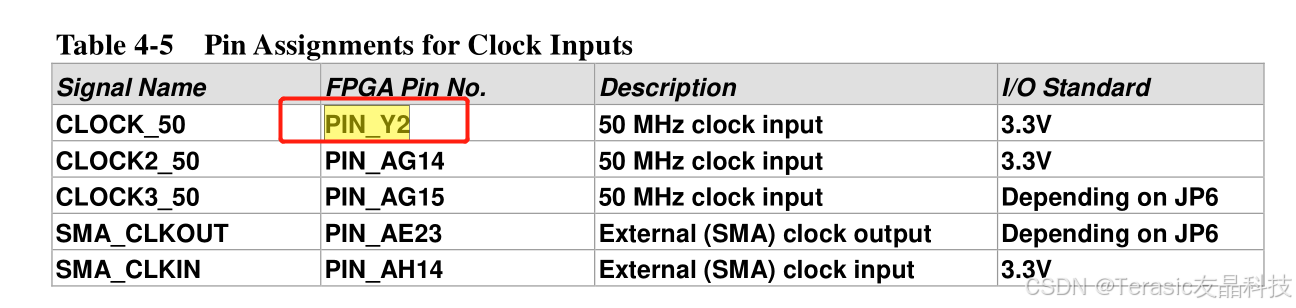

时钟引脚参考:

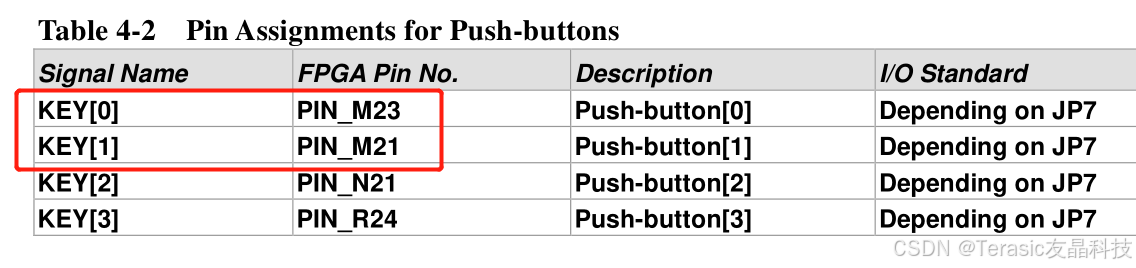

按键引脚参考(本实验只用到KEY0):

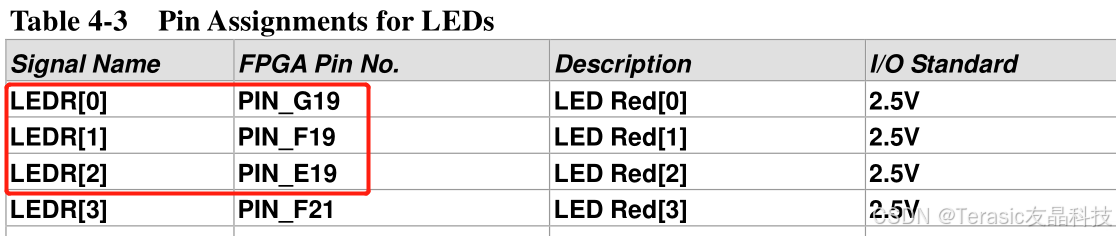

LED引脚参考:

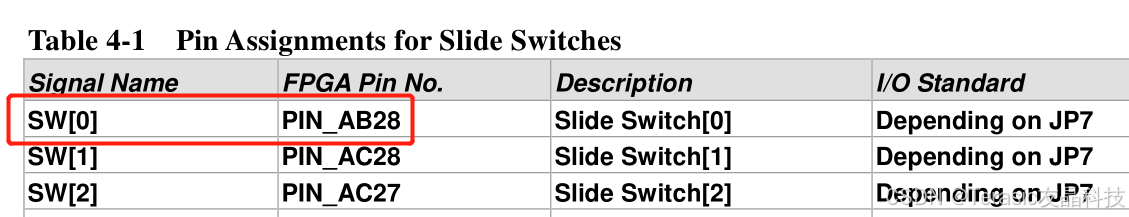

SW滑动开关引脚参考:

最终引脚分配图如下:

6. 添加约束文件

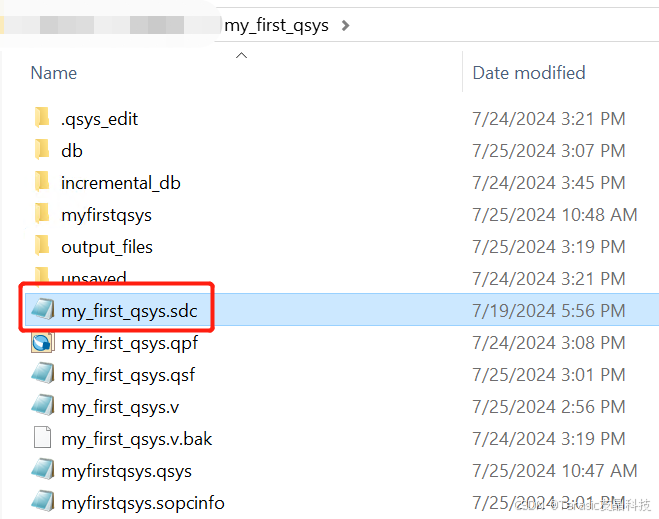

时间约束对于成功的设计至关重要。在本教程中,您将创建一个Quartus Prime TimeQuest时序分析器使用的基本Synopsys设计约束文件(.sdc)。

本文只是简单的给出时序约束代码。对于更复杂的设计,您需要更仔细考虑时序约束。

添加约束文件my_first_qsys.sdc到my_first_qsys工程目录下。

my_first_qsys.sdc文件内容如下:

create_clock -period 20.000 -name CLOCK_50

derive_pll_clocks

derive_clock_uncertainty这是最简单的时序约束内容。

第一句就是创建 50M的时钟信号;

第二句会用这个驱动 pll clock;

第三句会用这个时钟驱动不确定的时钟信号;

这样所有时钟都在这个50M约束下布线的。

添加my_first_qsys.sdc文件到my_first_qsys工程:

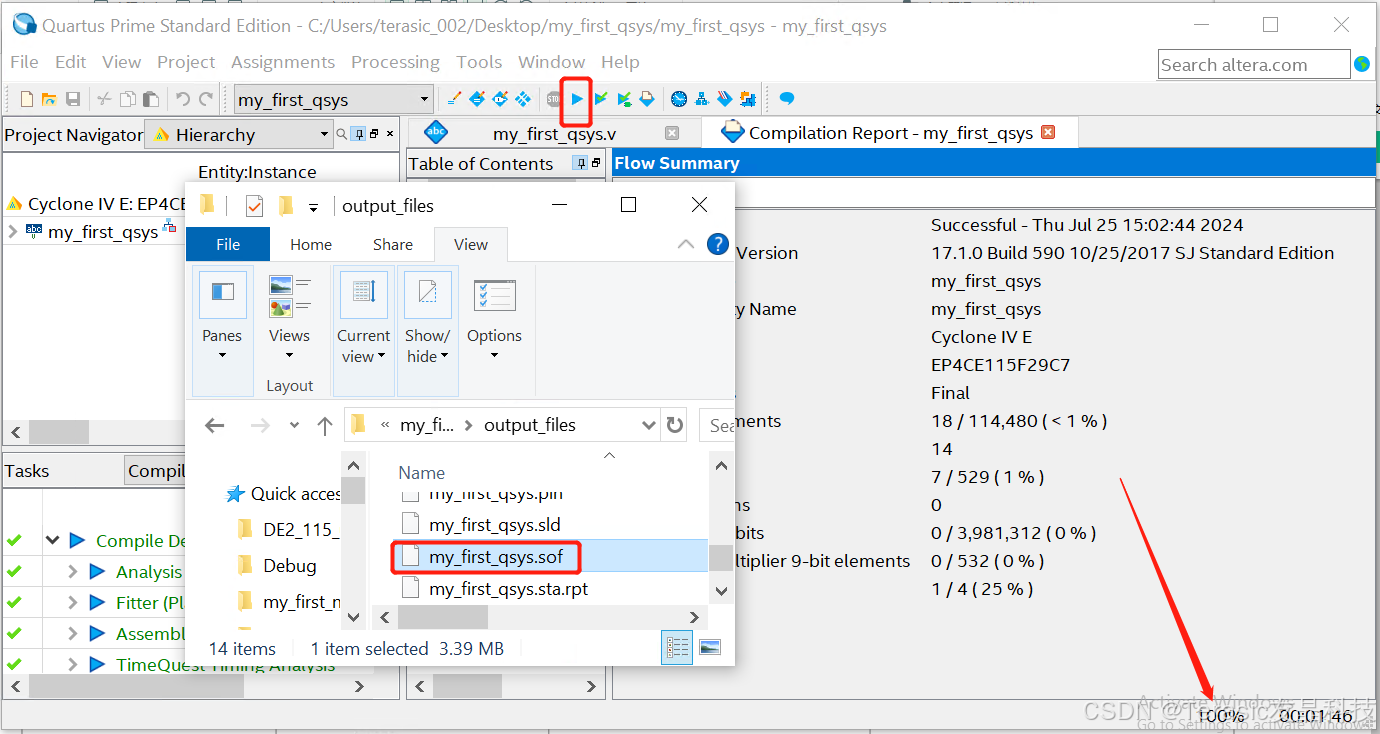

7. 编译工程

单击顶部工具栏上的Start Compilation按钮来编译整个设计。

就是这样! 您已经设计并编译了您的第一个Qsys系统。

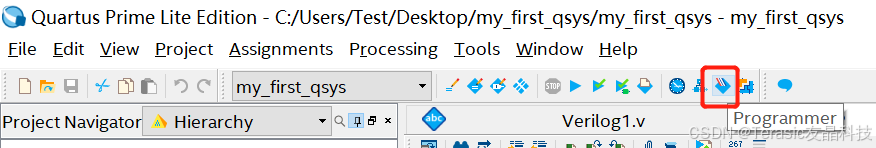

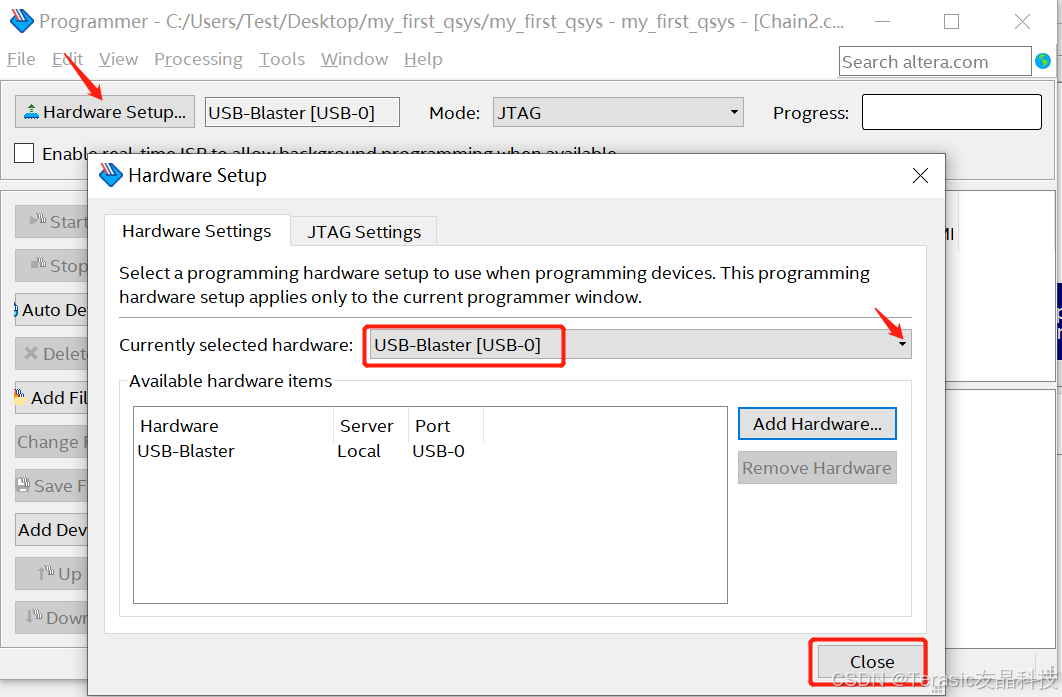

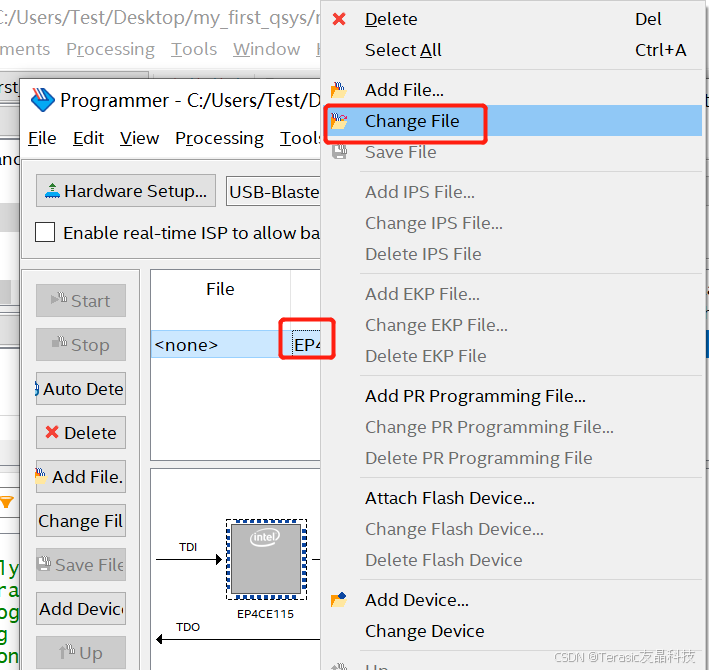

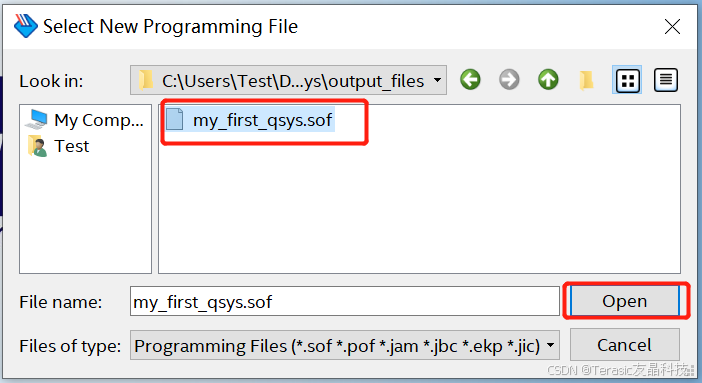

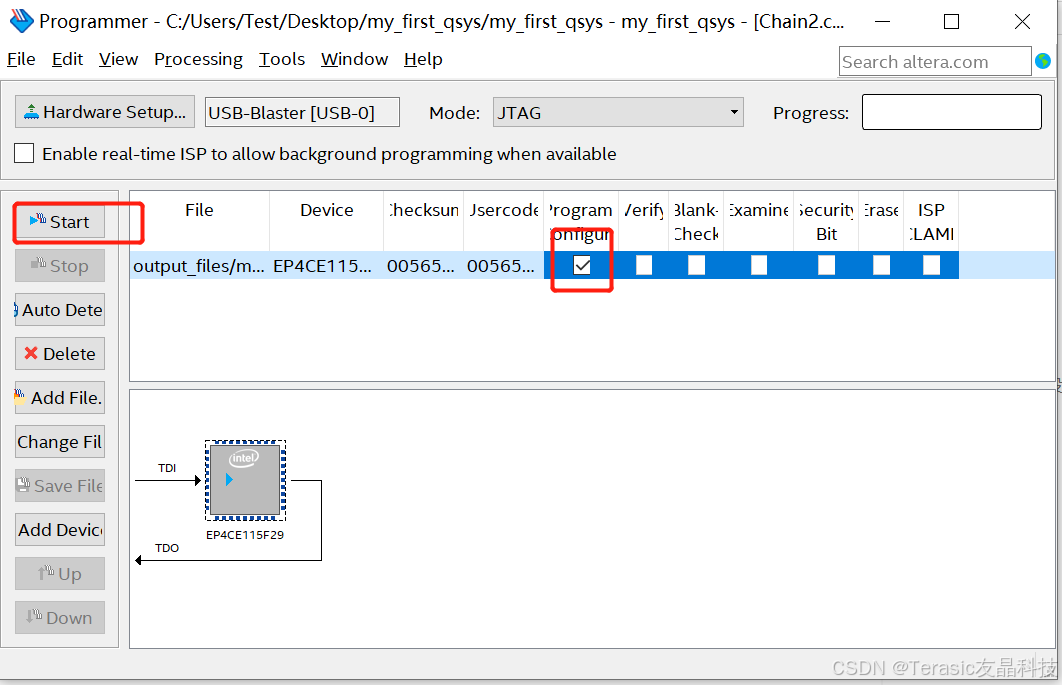

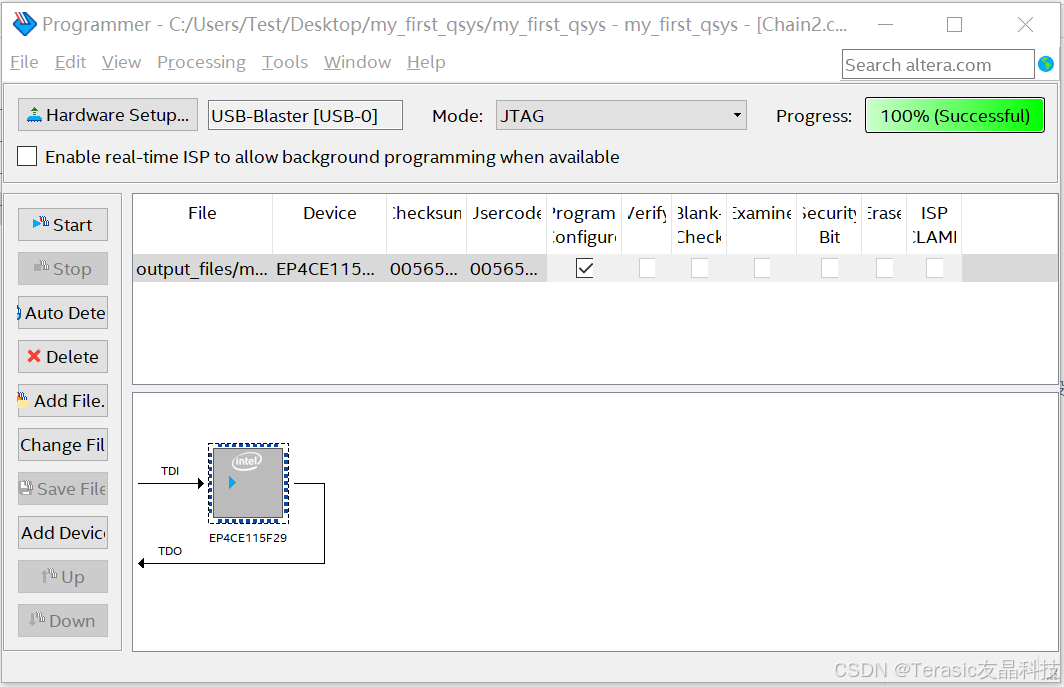

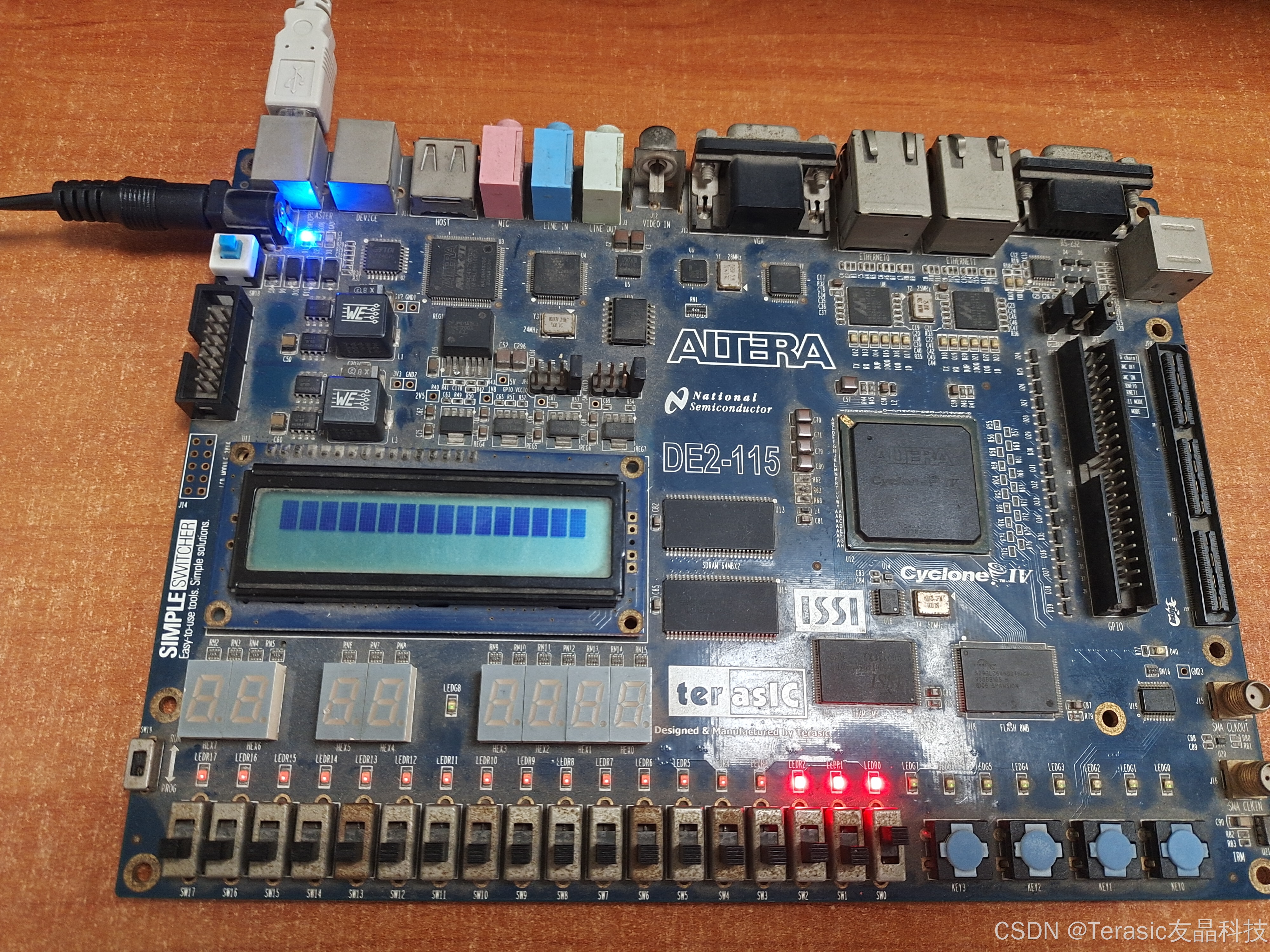

8. 配置FPGA:

9. 观察现象:

9. 观察现象:

把SW[0]拨向下,LEDR[3:0]按照计数器规则亮起来(速度快):

把SW[0]拨向上,LEDR[3:0]按照计数器规则亮起来(速度慢);

按KEY0复位则不闪烁。

七、更多教程参考

【入门教程一】基于DE2-115的My First FPGA 工程-CSDN博客

Platform Designer 自定义IP(用于纯RTL设计)-CSDN博客

【入门教程三】基于DE2-115的Nios V工程——My First Nios V-CSDN博客

另外,Intel官方的Platform Designer教程请参考:【Intel官方教程】Intel 平台FPGA设计工具Platform Designer的使用详细详解_哔哩哔哩_bilibili

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)