简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

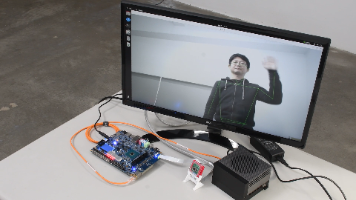

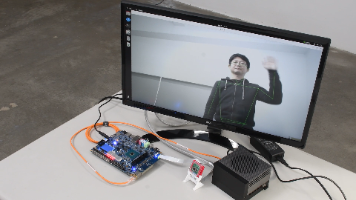

Terasic推出基于DE25-Standard FPGA的传感器桥接方案,实现高带宽、低延迟的边缘AI处理系统。该方案通过MIPI CSI-2接口采集1600万像素摄像头数据,经FPGA实时处理后转换为10GbE网络数据包传输至NVIDIA Jetson AGX Orin平台,支持YOLOv8(n)实时姿态估计。DE25-Standard作为传感器与GPU间的加速桥,具备原生连接、确定性低延迟处

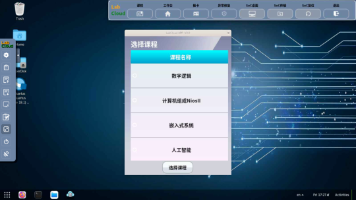

LabCloud 不仅可提供丰富的课程(如数字逻辑、计算机组成、嵌入式设计、人工智能等),还提供了众多网页交互功能,如文件上传下载、作业提交、特色课程定制等等;LabCloud 是通过 B/S 架 构 (Browser/Server)实现将 FPGA 硬件和 FPGA 开发环境搬移至云端,使用者无需搭建任何开发环境,只需使用浏览器访问 LabCloud 即可随时随地在任意终端进行 FPGA 学习与

Terasic推出基于DE25-Standard FPGA的传感器桥接方案,实现高带宽、低延迟的边缘AI处理系统。该方案通过MIPI CSI-2接口采集1600万像素摄像头数据,经FPGA实时处理后转换为10GbE网络数据包传输至NVIDIA Jetson AGX Orin平台,支持YOLOv8(n)实时姿态估计。DE25-Standard作为传感器与GPU间的加速桥,具备原生连接、确定性低延迟处

Quartus Prime软件中集成了UART控制器:UART(RS-232 Serial Port)Intel FPGA IP。UART(RS-232 Serial Port)Intel FPGA IP用于在Intel FPGA上的嵌入式系统与外部设备之间进行串行字符流通信。该IP实现了RS-232协议,并提供可调节的波特率、校验位、停止位和数据位。

在上一个教程My First FPGA工程当中,模块创建直接用Verilog code 写的,那是一个最简单的系统, 如果遇到稍微大一点规模系统,直接的code编写将会显得非常费时了,其实Intel还有另外一个非常好用的工具帮助工程师快速设计FPGA工程,那就是Platform Designer(Qsys)。图形界面,简化系统开发复杂性工程师在设计过程中可调用Intel Quartus 软件IP(

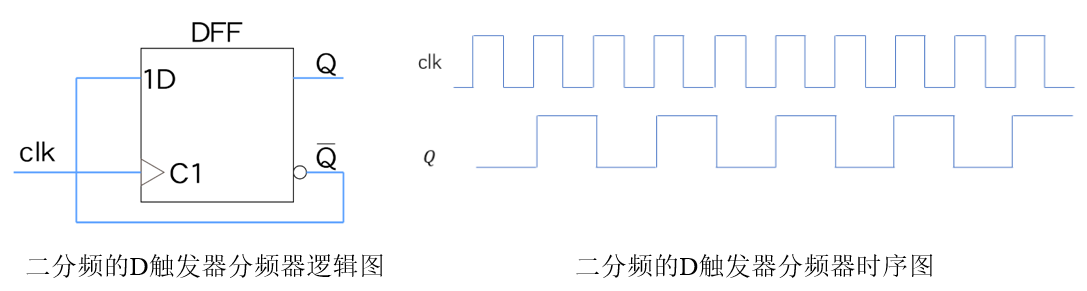

D触发器方式实现偶数分频器

在数字电路中,7段数码管是一个应用非常广泛的显示器件,它有7个可独立点亮的线段(LED灯), 用户可以通过控制点亮7个线段中某些线段来显示十六进制数0~F。目前有两种类型的7段数码管显示器件:共阴极数码管和共阳极数码管。共阴极数码管是7个LED的阴极端一起接地,每个阳极端单独连接到控制端(比如接到FPGA的GPIO pin)。共阴极数码管器件是高电平有效。共阳极数码管是7个LED的阳极端一起连接V

写法就是有三个always 块,一个时序逻辑采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件、描述状态转移规律,第三个模块使用同步时序的方式描述每个状态的输出。三段式代码容易维护,时序逻辑的输出解决了两段式组合逻辑的毛刺问题,但是从资源消耗的角度上看,三段式的资源消耗多一些。Verilog语言可以依靠不同的always语句块实现硬件电路的并行执行,但在实际工程中,不仅需要并行

在实现VGA色块显示之前读者需要先了解VGA显示原理和ADV7123的控制,有了这些基础之后再去贪吃蛇游戏里面实现色块显示就非常简单了。

本教程将以全加器为例,选择DE2-115开发板的Cyclone IV EP4CE115F29C7 FPGA,使用Quartus Lite v18.1,循序渐进的介绍如何创建Quartus工程,并使用Quartus Prime软件的University Program VWF工具创建波形文件,对全加器的功能进行仿真。使用University Program VWF工具进行仿真,其实也是调用Model