简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

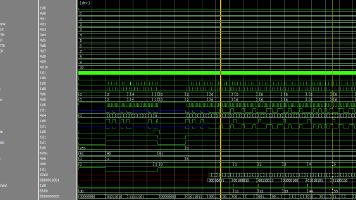

摘要:本文记录了一次利用AI工具Claude Code快速完成FPGA模块设计的实战经历。作者在不查阅手册的情况下,仅用1小时就实现了包含UART通信、协议解析和PWM控制的完整功能模块。测试显示,AI辅助开发在模块定义、状态机编写、Testbench生成等环节效率提升8-15倍,总耗时从传统3.5小时缩短至25分钟。虽然AI能生成高质量代码,但仍需人工验证位宽、锁存器等关键问题。文章认为,AI将

摘要:本文总结了Xilinx 7系列、UltraScale/UltraScale+ FPGA及MPSoC器件使用LVDS接口的关键注意事项。重点包括:1) HP Bank的LVDS输出需1.8V VCCO,HR/HD Bank需2.5V;2) LVDS输入允许VCCO不匹配但需禁用内部终端电阻;3) 不支持原生LVDS_33标准;4) 双向LVDS必须严格匹配VCCO电压;5) 必须确保信号电平符

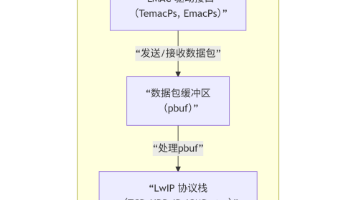

本文档详细介绍了在Zynq XC7Z035平台上实现PL端DMA数据传输与PS端LWIP UDP通信的技术方案。系统架构分为PL和PS两部分:PL端通过AXI DMA控制器将数据写入DDR特定区域,PS端通过DMA中断触发数据读取,添加包头后使用LWIP协议栈进行UDP发送。文档包含完整的Vivado硬件设计流程(Block Design配置、IP核连接、地址分配)和SDK软件实现(DMA初始化、

本文总结了基于Vivado工具的FPGA时序收敛流程与方法,涵盖三个阶段:分析诊断、优化调整和验证收敛。详细介绍了时序分析基础、常见问题诊断、RTL与实现优化技巧,包括控制集优化、布局规划等。提供了高级方法如QoR建议、约束调整和多角分析,以及最终验证步骤。文中包含实用Tcl命令、GUI工具推荐和最佳实践建议,强调早期分析、渐进优化和团队协作。通过系统应用这些方法,可有效提高FPGA设计的时序收敛

摘要: ZYNQ中AXI BRAM通过AXI BRAM Controller实现PS与PL的高效数据交互。硬件设计需在Vivado中配置AXI BRAM Controller和BRAM Generator,并分配地址空间。BRAM支持单/双端口模式,可自定义位宽与深度。软件上,PS可通过裸机指针或Linux的/dev/mem、UIO驱动访问BRAM,适用于缓存、共享内存等场景。注意事项包括位宽匹配

LwIP在ZYNQ上的轻量级TCP/IP协议栈实现 LwIP是一个开源的轻量级TCP/IP协议栈,专为资源受限的嵌入式系统设计。在ZYNQ平台上,LwIP能充分利用ARM处理系统和FPGA可编程逻辑的协同优势,提供高效网络通信。它支持多种协议(IP/UDP/TCP等)和三种编程接口(Raw/Callback API、Netconn API和Socket API),可根据性能需求灵活选择。实现步骤包

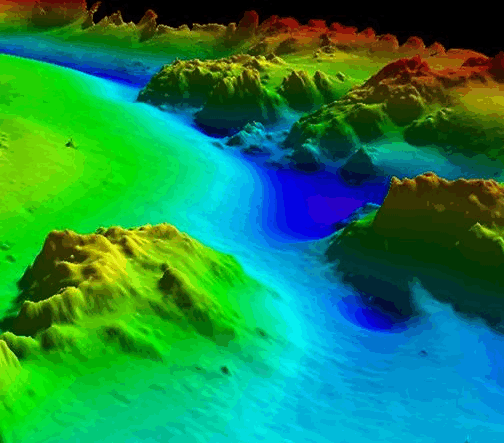

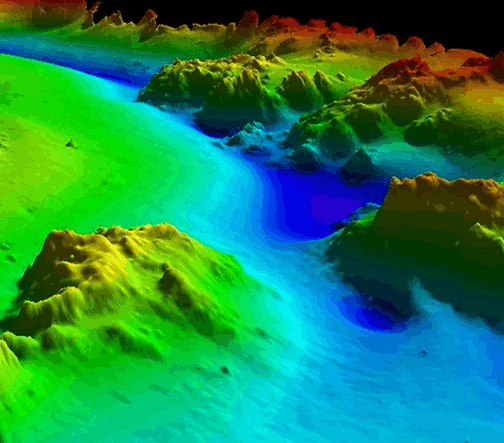

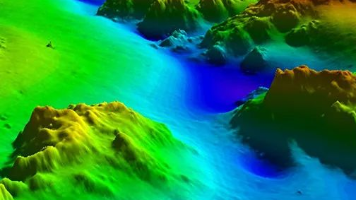

SONIC 2020 是一款高度集成、软件定义实时可调频率与波束角,适应不同水深与测绘需求。嵌入式处理,减少外部硬件依赖。丰富的操作模式(UHD、MultiMode、FLS 等),支持多样化测绘任务。标准化以太网通信,便于集成与扩展。完善的传感器支持与时序同步,保障数据精度。

本文介绍了一个基于Verilog的I2C主设备接口实现方案。该模块采用状态机设计,支持7位从机地址、读写操作和多字节连续传输。主要功能包括:时钟分频生成I2C时序、状态机控制传输流程、地址/数据发送与接收、应答检测等。代码提供了详尽的注释,可直接应用于SHT45等I2C接口传感器的驱动开发。设计参数可调,支持自定义I2C时钟频率,具备忙状态指示和错误检测功能。该实现方案结构清晰,可作为嵌入式系统中

本文详细介绍了ZYNQ AXI DMA的两种工作模式:Simple模式和Scatter-Gather(SG)模式。Simple模式通过寄存器直接控制传输,实现简单但效率较低;SG模式使用描述符链表实现自动传输,适合高吞吐场景但实现复杂。文章对比了两种模式的特点,详细说明了工作流程、寄存器操作、缓存一致性处理、性能优化要点及常见问题排查方法,并提供了伪代码示例。还介绍了中断与轮询的选择策略,以及与C