简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

本实验将实现参考文章中的PS-PL间的数据转发功能。实验中PS端的数据存在DDR中,PS端通过AXI-stream FIFO将数据转变为流模式输出。

本文提出了一种用于通信系统信道估计的深度学习算法,将快速衰落通信信道的时频响应视为二维图像。目的是利用导频位置的一些已知值来找到信道响应的未知值。文中提出了一种利用深度图像处理技术、图像超分辨率(SR)和图像恢复(IR)的通用pipeline,该方案将导频值视为低分辨率图像,并使用SR网络与去噪IR网络级联来估计信道。结果表明,该方法可以有效地用于信道估计。估计误差表明该算法可与充分了解信道统计信

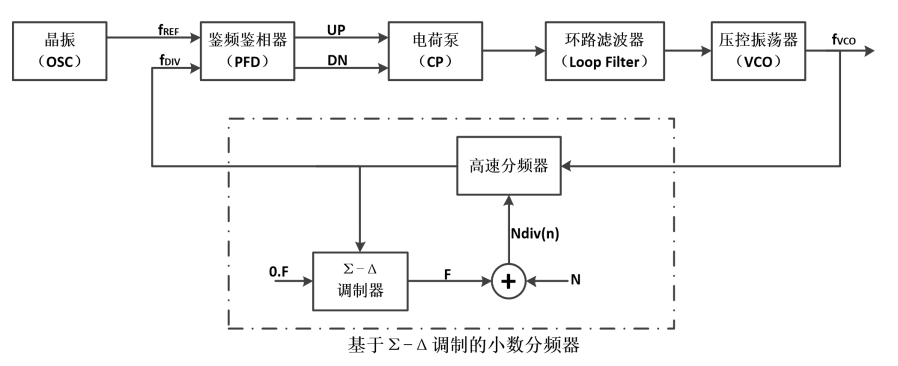

频率合成器他作为无线收发机系统的一个非常关键的模块,它的功能是用于产生本振信号,本振信号是收发机所必需的,其输出的信号的好坏决定了收发机变频信号的优劣,调频范围决定了收发机的收发频率范围,收发机工作的效率受到其频率的切换时间制约,收发机最小信道宽度受限于频率合成器的精度。直接模拟式频率合成器(Direct Analog Synthesizer,DAS)直接数字式频率合成器(Direct Digit

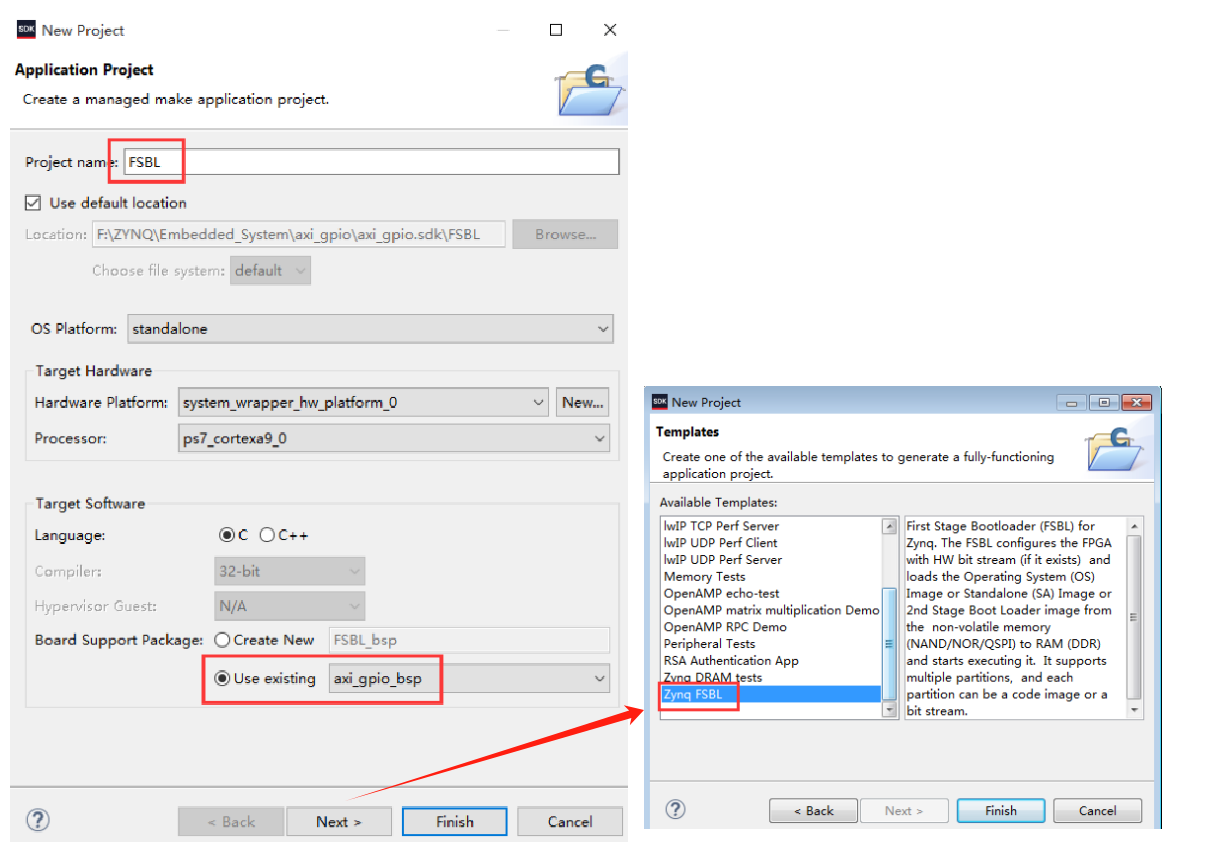

调试阶段是通过 JTAG 接口将 FPGA 配置文件和应用程序下载到 ZYNQ 器件中。但在实际应用中需要程序在上电或者复位时让程序自动运行,这个过程需要启动引导程序(Boot Loader)的参与。Boot Loader 会加载 FPGA 配置文件,以及运行在 ARM 中的软件应用。

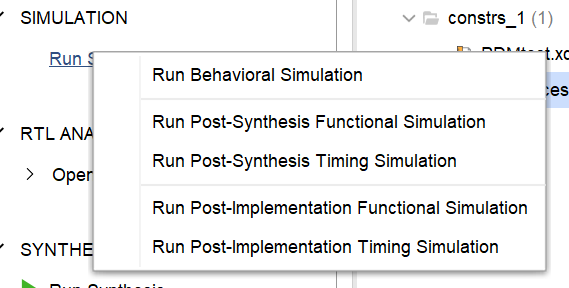

在数字电路设计过程中,通常涵盖三个主要阶段:源代码编写、综合处理以及电路的实现,相应地,电路仿真的应用也与这些阶段紧密相关。根据不同设计阶段的需求,仿真可以被划分为RTL行为级仿真、综合后的门级功能仿真以及时序仿真。这样的仿真流程框架不仅适用于FPGA/CPLD的设计,而且也同样适合于集成电路(IC)的设计。**如果行为仿真下面的四个模式是灰色的无法选中说明你还没有对你的文件进行综合和布局布线还未

PCIe,英文缩写为PCIe或者PCI Express,一般用于CPU与外部设备进行高速连接(GPU,声卡),PCIe是点对点,全双工的差分传输信号总线。

FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。

CIC (Cascaded Integrator-Comb) 滤波器是一种常用的数字信号处理滤波器,主要用于降采样(decimation)和升采样(interpolation)操作,它具有简单的硬件实现、高效的运算速度以及适用于需要快速处理的应用场景等优点。

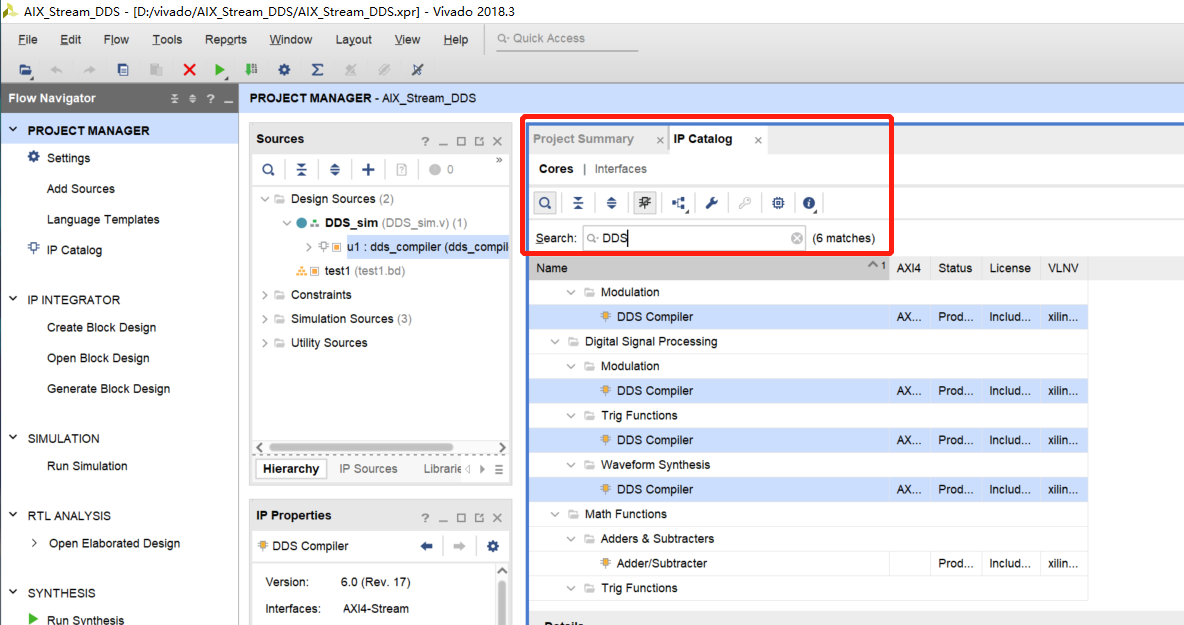

Vivado DDS; DDS(Direct Digital Synthesis,直接数字频率合成),作为信号发生器使用,在Quartus中也叫NCO(Numerically Controlled Oscillator,数字控制振荡器),是软件无线电中的重要组成部分。

UART广泛应用于微控制器和计算机之间的数据通信,如GPS模块、蓝牙模块、GSM模块等。UART是一种通用在嵌入式设计中,UART用于主机与辅助设备通信UART通常被集成于其他通讯接口的连结上。UART 通道有两条数据线:每个设备上都有一个 RX 引脚和一个 TX 引脚(RX 用于接收,TX 用于发送)每个设备的 RX 引脚都连接到另一个设备的 TX 引脚。此时,需要在两个UART设备上指定相同的