简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

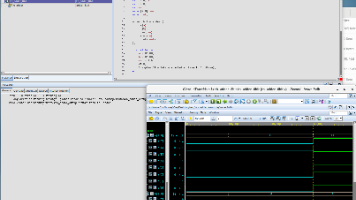

芯片设计-利用VCS+Verdi仿真实现 8位加法器

本文介绍了使用VCS和Verdi工具进行Verilog仿真验证的完整流程。首先通过source命令设置环境变量,创建项目目录并编写8位加法器设计文件(adder_8bit.v)和测试平台(tb_adder_8bit.v)。然后使用VCS命令编译生成可执行文件simv,运行仿真验证加法器功能。最后通过Verdi工具查看波形文件(wave.fsdb),分析信号时序关系。整个过程涵盖了从环境配置、代码编

从零开始上手大模型—— 01.环境配置

Docker Desktop 是一个。它会在你的Windows系统内部,悄悄地创建一个小型的、高效的Linux虚拟机(默认基于WSL2技术)。

到底了