简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

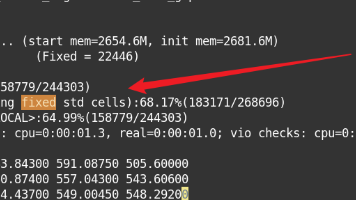

文章摘要:标准单元在物理设计中有五种放置状态:unplaced(初始状态)、placed(布局后)、fixed(不可移动单元,如ENDCAP等)、cover(完全锁定)和soft_fixed(全局布局固定但细节可调)。其中fixed状态单元在布局工具中不可移动,check place命令会分别统计包含/不包含fixed单元的密度。图文展示了fixed单元实例和密度检查结果。(98字)

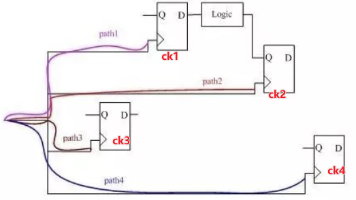

摘要:时钟偏差(skew)与布局布线相关,可通过设计优化降低影响;抖动(jitter)源于时钟源内部工艺,无法消除但需留设计余量。时钟不确定性(clock uncertainty)用于缓解抖动影响,考虑悲观情况(setup提前/hold延后)。在PR流程中,CTS前需手动添加skew补偿ideal时钟的乐观估计,CTS后则采用实际布线值。图示展示了三种时钟时序特性的差异。(149字)

电迁移效应(electro-migration effect)是指在导致金属离子移位,宏观上表现为金属变形,,久而久之可能会使芯片中的net发生短路或断路,进而造成芯片工作失效。简单来说,就是。从上面的介绍,我们可以知道,如果导体的电流密度越大,那么造成EM效应的可能性就越高。如果导体温度过大,热运行效应强也会导致EM效应更显著。因此我们在讲EM能力的时候指的就是是。

因此我们对于signal EM的问题,首选方法是NDR设置net宽度来降低电阻,从而使金属层更承载的电流密度更大,也被称为EM能力更强。因此在CTS之前,我们要进行NDR规则的设置,比如设置net为2倍的space,后续route时,工具会遵循此约束来生长时钟树。因为时钟信号在芯片中是一个非常关键的信号,因此我们通常希望它使用的金属层有更好的EM能力。,从而导致open/short,从而失效。由于

本文总结了两种常用IC设计命令:1)查看dont use单元的指令为dbGet [dbGet -p head.libCells.dontUse true].name;2)查看dont touch实例的指令为dbGet [dbGet -p top.insts.dontTouch true].name。这些命令在PR(布局布线)过程中可以有效避免因搜索结果错误带来的问题。

主要原因是显卡降频,显卡带不动的问题。

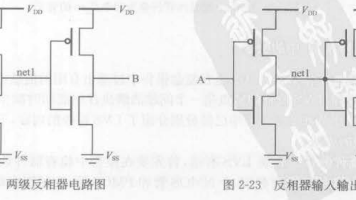

如第二级反相器的输入与输出短接造成电路中 netl 成为同一节点(图 23) ,使电路总节点数减为 个,与网表中 个节点数目不 LVS 就会报错。告知我们电路中存在开路或短路问题。版图和电路原理图比对。电气连接关系检查:包括电源信号、地信号、输入、输出、以及器件所有连接节点。确保所画版图与设计电路完全一致就是 LVS 工具要做的工作。

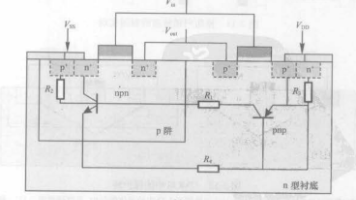

CMOS 工艺中形成的许多寄生元件如果不作处理会产生门锁效应 (latch up effect)。如图,下面是一个 CMOS 工艺制成的反相器电路截面图:由与的存在,又由于阱区和衬底寄生电阻R2和的存在。使,在瞬态干扰下一旦某 个寄生品体管具有足够的基极偏置电压,使正反馈电路进入工作状态,将使电流不断放大,最终导致电源和地之间形成极大的导通电流,破坏电路正常工作甚至烧坏整个芯片。

时钟树综合(CTS)主要通过命令操作实现,关键步骤包括:1)设置时钟树单元列表,确定可用缓冲器和反相器;2)通过ccopt配置文件优化时钟约束;3)生成时钟树规格并执行综合。完成CTS后可使用clock tree debugger查看延迟分布,并通过timingDesign检查时序,必要时用optDesign修复问题。CTS目标是构建低延迟、低偏斜的时钟网络,合理的约束配置直接影响综合效果。