简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

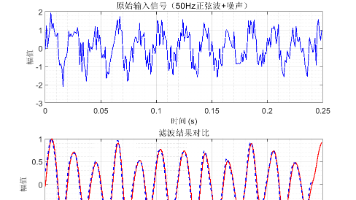

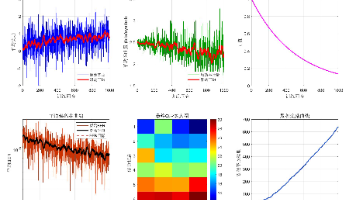

本文介绍了分布式算法(DA)在15阶FIR滤波器中的实现方法。该方法通过位分解、查表替代乘法运算,显著降低硬件开销。推导过程包括:输入数据位分解、乘加运算按位拆分、LUT查找表设计等关键步骤。MATLAB程序实现了基于DA的FIR滤波器,包含系数量化、LUT预计算、位分解查表等核心模块。测试结果表明分布式FIR与传统FIR滤波效果一致,验证了算法正确性。该方法特别适合FPGA实现,能有效解决高阶F

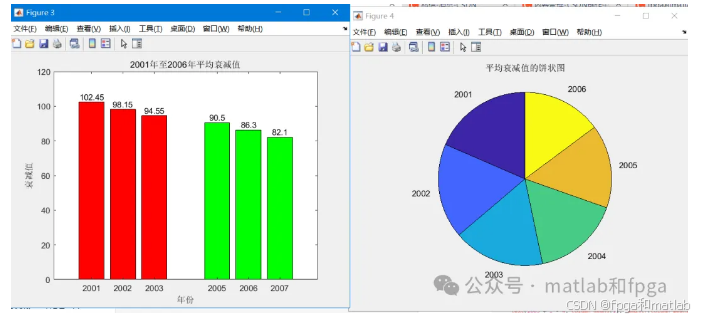

这可就给那些没什么电脑操作基础,尤其是对编程一窍不通的朋友们带来了不小的困扰,他们在使用这些工具的时候,往往会觉得困难重重,不知道从哪儿下手。接下来呢,咱们就简单地唠唠,怎样利用如今方便好用的 AI 工具,来帮一帮那些不会编程的朋友们轻松地制作出各种各样的统计图表呀。而对于那些要求更高、更专业一些的情况呢,人们往往就得借助编程工具了,像 MATLAB、VC 之类的。跟进一步,如果需要更复杂的图,比

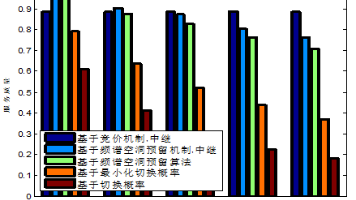

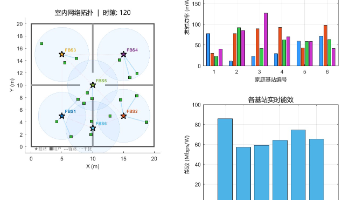

本文提出了一种基于中继协助的认知无线电频谱切换机制。该机制在网络中引入中继节点(RN),协助次用户(SU)完成频谱感知、目标信道筛选和链路切换,解决了SU本地感知盲区、切换时延高和链路易中断的问题。通过建立网络拓扑模型和中继协助模型,分析了协作通信对系统性能的影响。仿真结果表明,该机制能有效提高频谱利用率和通信可靠性,特别是在频谱资源稀缺或用户数量增加的情况下。核心算法采用竞价拍卖模型进行频谱资源

摘要:本文提出了一种基于强化学习的水声通信自适应调制方法,用于解决传统反馈机制因传播时延导致的信道状态信息过时问题。通过将水声信道建模为有限状态马尔可夫模型,并采用Q-learning算法建立状态-动作映射,使系统能够自主选择最优调制方式。MATLAB仿真结果表明,该方法在时变水声信道中能有效提高系统吞吐量,同时保持误码率在目标阈值以下。完整程序代码已提供,包含详细注释和操作视频。

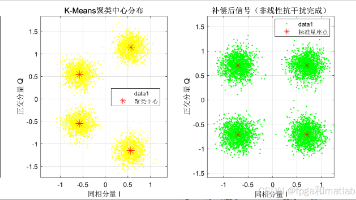

摘要:本文提出一种基于K-Means聚类的非线性抗干扰算法,用于解决光通信系统中由克尔效应和光电器件引起的非线性失真问题。算法分为训练和补偿两个阶段:训练阶段通过K-Means聚类学习失真星座点的中心位置,补偿阶段利用纠正向量对实时信号进行修正。MATLAB仿真结果表明,该方法能有效改善星座图发散现象,提升系统性能。完整程序代码已上传至CSDN平台,适用于matlab2022a/2024b版本。

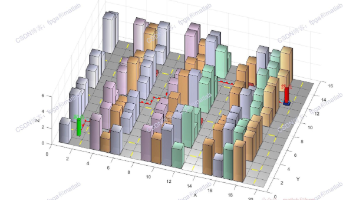

本文介绍了一种基于Q-Learning强化学习的无人驾驶小车城市道路行驶控制系统。系统将城市道路环境离散化为网格世界,定义小车的状态空间、动作空间(上、下、左、右、静止)和奖励函数。通过Q-Learning算法迭代训练,小车逐步学习最优行驶策略。Matlab仿真程序实现了三维城市场景的可视化,展示小车沿最优路径行驶过程。仿真结果表明,系统能有效使小车学会避开障碍物、遵守车道约束并到达目标位置。完整

本文提出一种基于深度Q学习的室内无线网络功率分配算法,用于解决家庭基站密集部署时的同频干扰和能耗问题。通过构建包含信道增益和干扰水平的状态空间,将连续功率离散化为动作空间,以能效作为奖励函数,采用深度神经网络逼近Q值函数。MATLAB仿真结果表明,该算法在能效、传输速率和功率控制方面均优于传统Q学习和注水算法,实现了动态环境下的资源优化分配。完整程序已上传至CSDN平台。

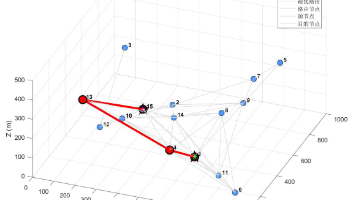

摘要:针对无人机自组网(UANET)中传统AODV路由协议因仅考虑跳数而导致的频繁断链问题,本文提出一种基于Q-Learning算法的改进路由方案。该方法将路由选择建模为马尔可夫决策过程,通过智能体与环境交互学习最优Q值表,综合考虑跳数、链路稳定性和节点剩余能量来选择最优路径。Matlab仿真结果表明,该算法能有效提高路由成功率,降低平均跳数,并在动态拓扑变化中保持稳定性能。完整仿真程序已在CSD

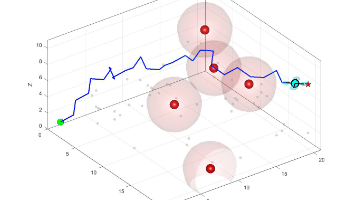

本文提出一种基于Q-Learning的无人机三维路径规划方法。通过构建包含静态和动态障碍物的三维栅格环境模型,设计多因子奖励函数(包括碰撞惩罚、目标趋近引导等7个因子),采用ε-greedy探索策略进行训练。MATLAB仿真结果表明,该方法在2000轮训练后收敛,成功率超过85%,能有效实现动态环境下的安全避障路径规划。完整程序已上传至CSDN平台(MATLAB 2024b版本)。

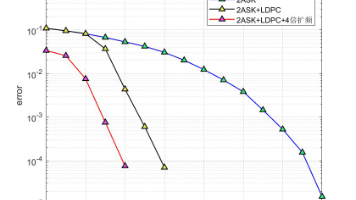

本文介绍了基于2ASK调制解调、LDPC编译码和扩频技术的通信系统设计与仿真。系统采用2ASK调制将数字信号转换为模拟信号,通过LDPC编码提高纠错能力,并利用扩频技术增强抗干扰性。仿真结果表明该系统能有效提高通信可靠性,特别是在低信噪比条件下。文中详细阐述了各模块原理,包括2ASK调制解调、LDPC编码和扩频技术的工作原理。完整MATLAB程序已上传至CSDN,支持2022a/2024b版本运行