简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

Complex Digital Hardware Design学习笔记(四)——SERDES IP

SERDES 瓦片在ASIC和FPGA中的设计集成了多种功能和能力,以促进高速数据传输,同时确保可靠性和测试灵活性。随着技术的发展,保持低抖动、优化时钟分配和增强错误校正机制变得日益重要,以支持复杂的通信协议。

【从零开始学ROS】ubuntu20.04+clion+ros环境搭建

ROS(机器人操作系统)是一个开源机器人开发框架,提供工具库和通信机制帮助开发者快速构建机器人应用。其核心是松耦合分布式通信架构,将系统拆分为独立节点模块,通过话题(异步发布/订阅)和服务(同步请求/响应)实现解耦通信。ROS支持节点跨进程/设备运行,具有容错性强、开发效率高、复用性好等优势。关键组件包括节点、节点管理器、消息/服务定义及参数系统,文件系统以功能包为基本单元。环境搭建需匹配Ubun

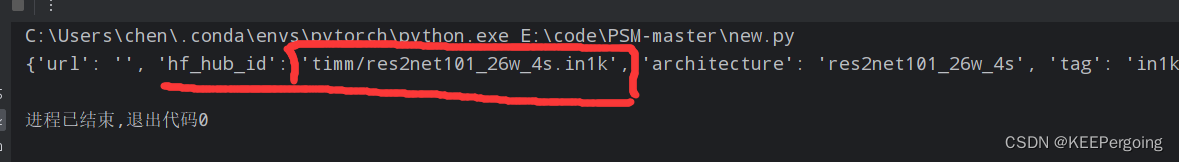

timm模块加载预训练模型报错——解决

timm模块加载预训练模块网络连接问题

到底了