简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

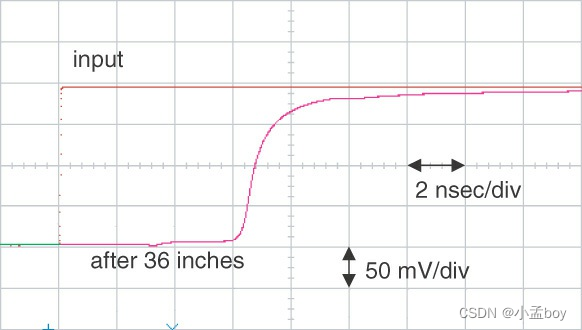

阻抗不连续会对传输信号的失真产生巨大影响。这将导致接收信号上升时间变差的直接后果。即使是没有损耗的线路也会因阻抗不连续而出现上升时间下降。这就是为什么为传输线、电路板过孔和连接器建立准确的模型如此重要——以准确预测仿真中的信号质量。这就是为什么在高速互连设计中尽量减少不连续性如此重要的原因。

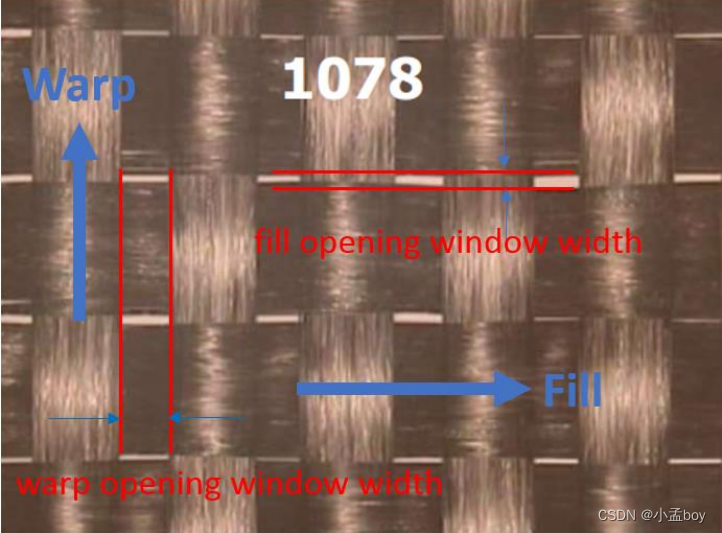

树脂和玻纤布的Dk差异很大,E-glass的Dk大约在6.8,low-Dk glass大概在4.8,而大多数PCB材料所用的树脂Dk是2.7-3.0,所以不管是常规的E布和low-Dk玻布,其Dk都是跟树脂有很大差异的。当差分对中的一条线分布在玻纤束上,另一条分布在开窗上时(即分布在树脂上),两条线的电场会穿透不同的材料,感知到的Dk也会不同,结果就是差分对内产生skew,Dk差异越大,skew越

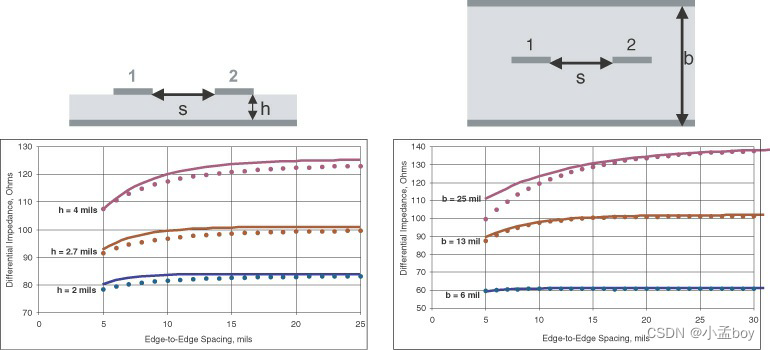

当信号线和返回平面之间的耦合度大于两条信号线之间的耦合度时,返回路径平面将会出现明显的返回电流,返回平面会影响信号线的差分阻抗。

1. cmd指令pip install pydub,安装pydub库,当然,还需要ffmpeg库,pip install ffmpeg安装或者下载ffmpeghttps://ffmpeg.zeranoe.com/builds/,解压安装后将路径复制到python安装路径下如D:\Python\Python37\Lib\site-packages,找到ffmpy.py,复制到对应位置,见下图。之后新

什么是 stitching via和aggressor via?stitch的意思为缝合,在AD中,有一个功能为via stitching,就是在走线两侧添加过孔,效果如下stitching via其实就是没有走线的过孔。https://www.altium.com/documentation/15.1/display/ADES/((Via+Stitching+and+Via+Shie...

以下内容摘自英文版的信号完整性分析一书(SIGNAL INTEGRITY By Eric Bogatin):The noise between two adjacent transmission lines can be measured in the configuration shown in Figure 10-3. A signal is injected into one end of

1、什么是Insertion Loss和Return Loss?经典的《Signal and Power Intergrity》中在S参数一章作了如下定义:Insertion loss is a measure of what is lost from the signal when the interconnect is "inserted" between the two ports of..

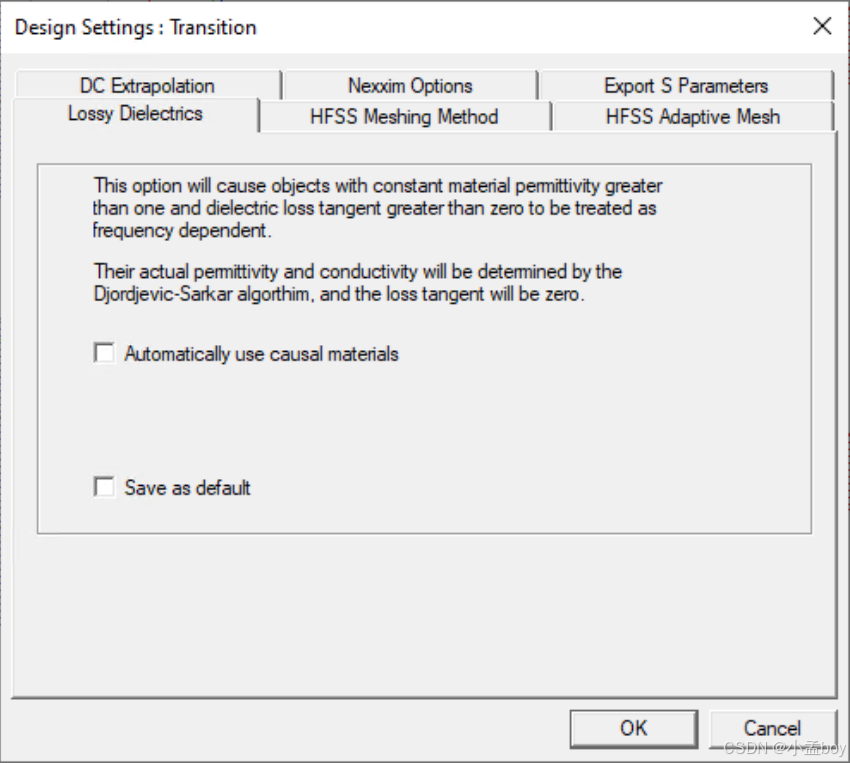

从HFSS 3D LAYOUT菜单中,选择Design Settings打开窗口,会有六个选项:DC Extrapolation, Nexxim Options, Export S Parameters, Lossy Dielectrics, HFSS Meshing Method, and HFSS Adaptive Mesh.

VGA接口公头和母头详细定义如下:普通串口定义如下:上公下母,每个引脚的定义见下方表格: