简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

connecting to sesman on 127.0.0.1:3350sesman connect oksending login info to session manager, Please wait...login failed for user fpga

最近在做FPGA视觉机器人,考虑到晚上机器人视线不好,萌发了给机器人做一个小型灯补光的想法。咱是机器人肯定要整点智能的对不对,思来想去觉得环境光传感器是个不错的选择。

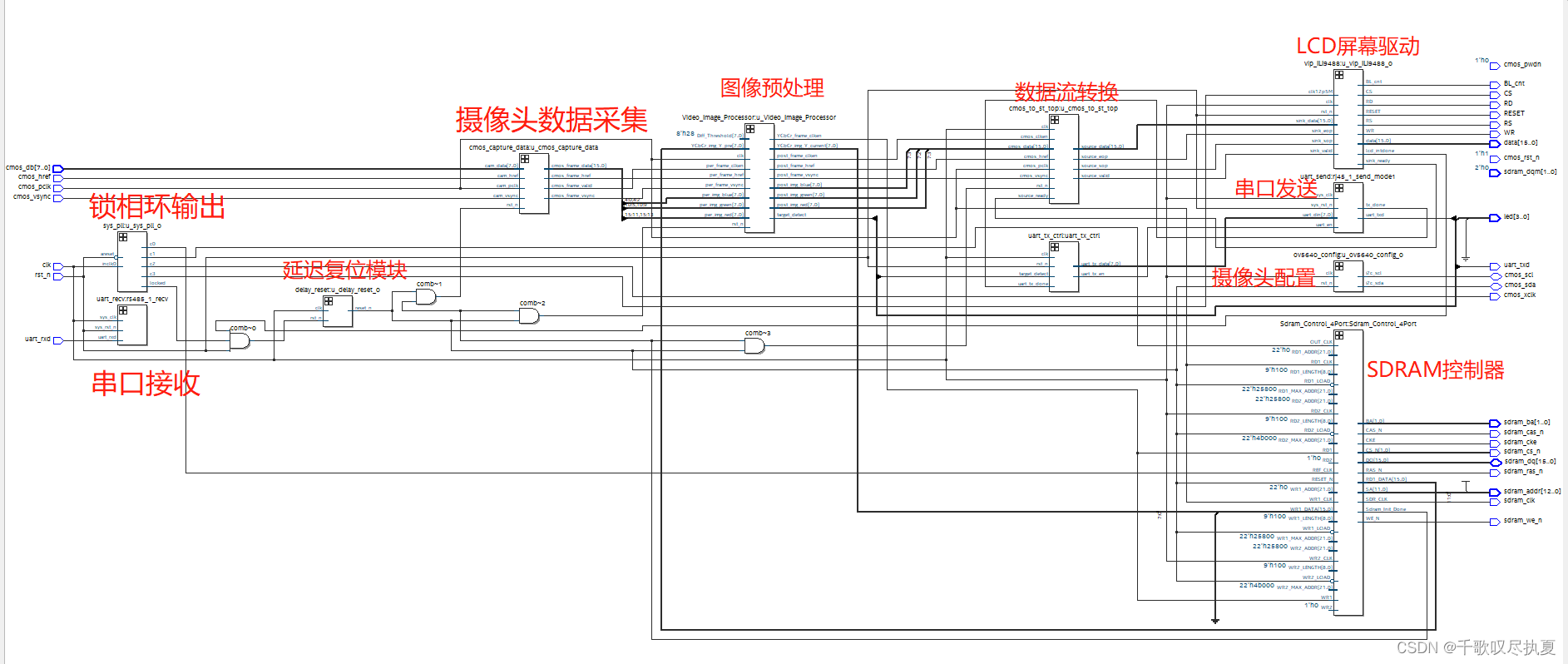

本系统在图像采集之前,由于板载晶振与摄像头模块及 TFT-LCD 模块频率不一致,所以在系统工作之前,需要设计锁相环模块输出与OV5640摄像头一致的时钟信号。时钟输入后,根据 OV5640 的手册进行寄存器配置,使 OV5640 的工作模式符合本系统的设计需求。CMOS 传感器采集进来的图像进入到图像处理模块,输出当前帧的灰度,用于写入SDRAM。同时从SDRAM中读出前一帧的灰度(与当前输出相

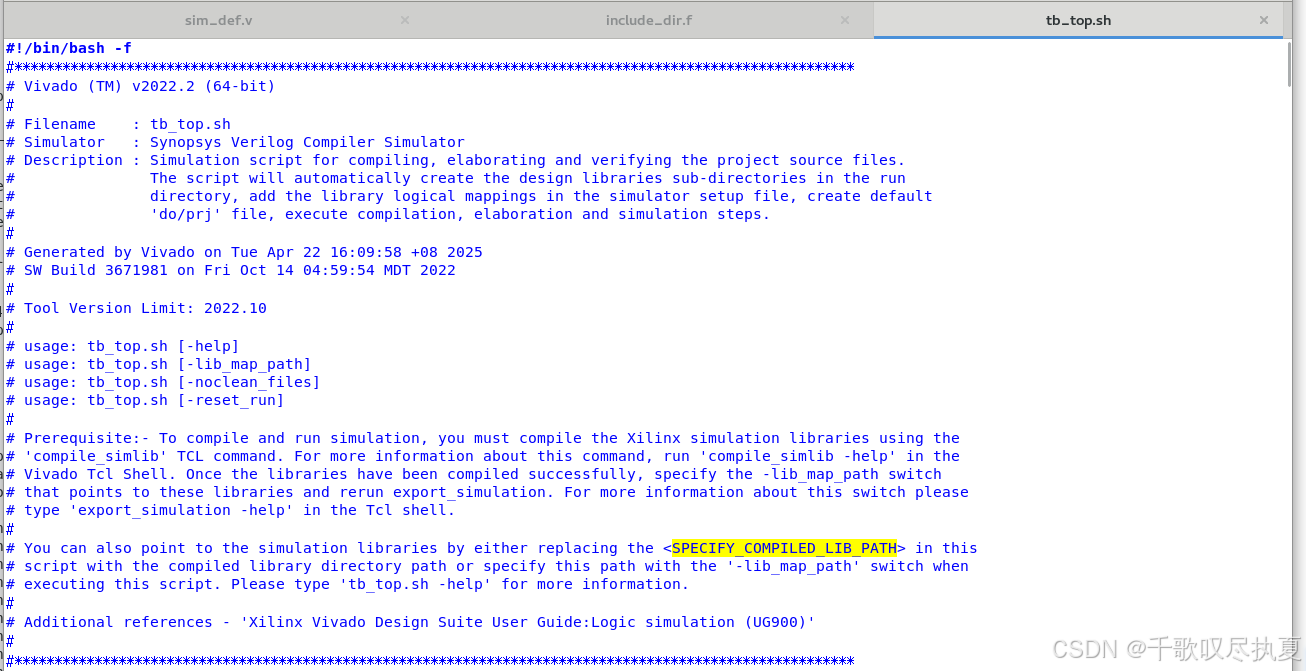

Vivado22 & Vcs18仿真联调原语缺失

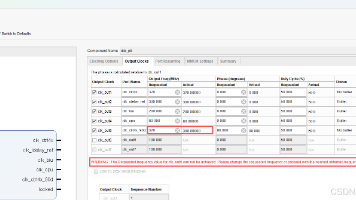

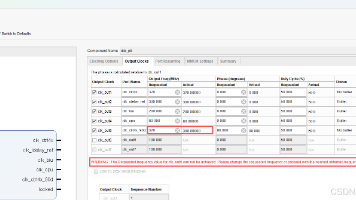

WARNING : The Requested frequency value for clk_out5 can not be achieved.Please change the requested freguency or proceed with the nearest obtained freguency value of 300.00000使用clk_out1和5改成400M反而可以,

关于AMD 9950X3D装Linux系统的一些问题(解决)

WARNING : The Requested frequency value for clk_out5 can not be achieved.Please change the requested freguency or proceed with the nearest obtained freguency value of 300.00000使用clk_out1和5改成400M反而可以,

下载vitis 2024.2后,无法创建基于.XSA的platform,在file选项里找不到new platform选项,在welcome页点击create platform component没有反应,example里也没有任何东西。

话说一个资深工程师出国的时候带了一块 FPGA 开发板。海关问道:“这是什么东西?”工程师说:“FPGA 开发板”。海关又问:“FPGA 是什么?”。工程师回答说:“你想让它是什么,它就是什么(It can be whatever you want)

目录日常·唠嗑前言一、认清逻辑设计二、时序逻辑电路设计三、扩展:呼吸灯实验日常·唠嗑 第一次建立《零基础学FPGA》专栏,是在2021年2月2日,已经过去了一年了,目前只更新了4篇。总说要更新,却总是拖更,直到这两天有关注的朋友提起,才想起来,在这里跟各位关注我的朋友说声抱歉。 &n