简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

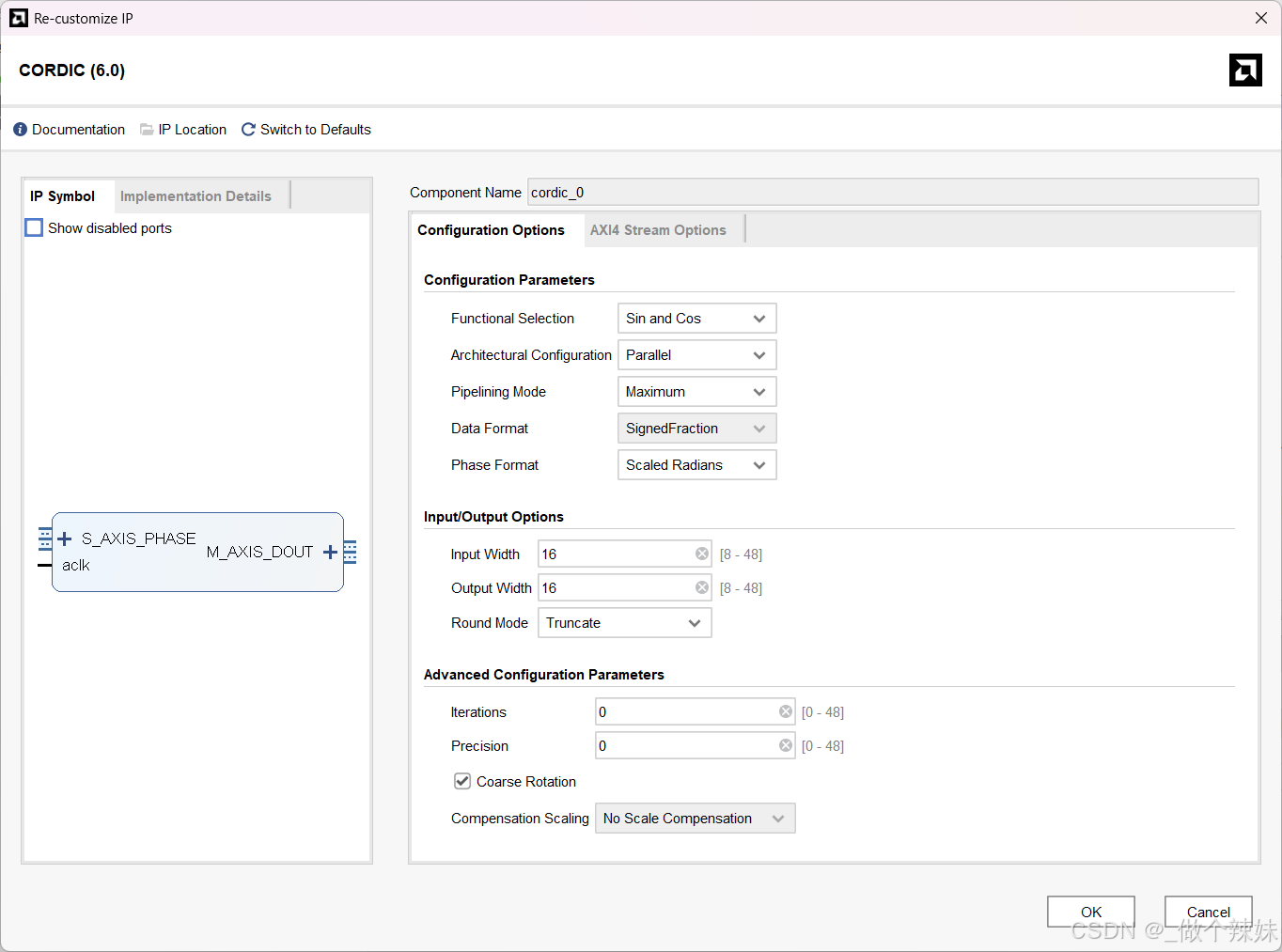

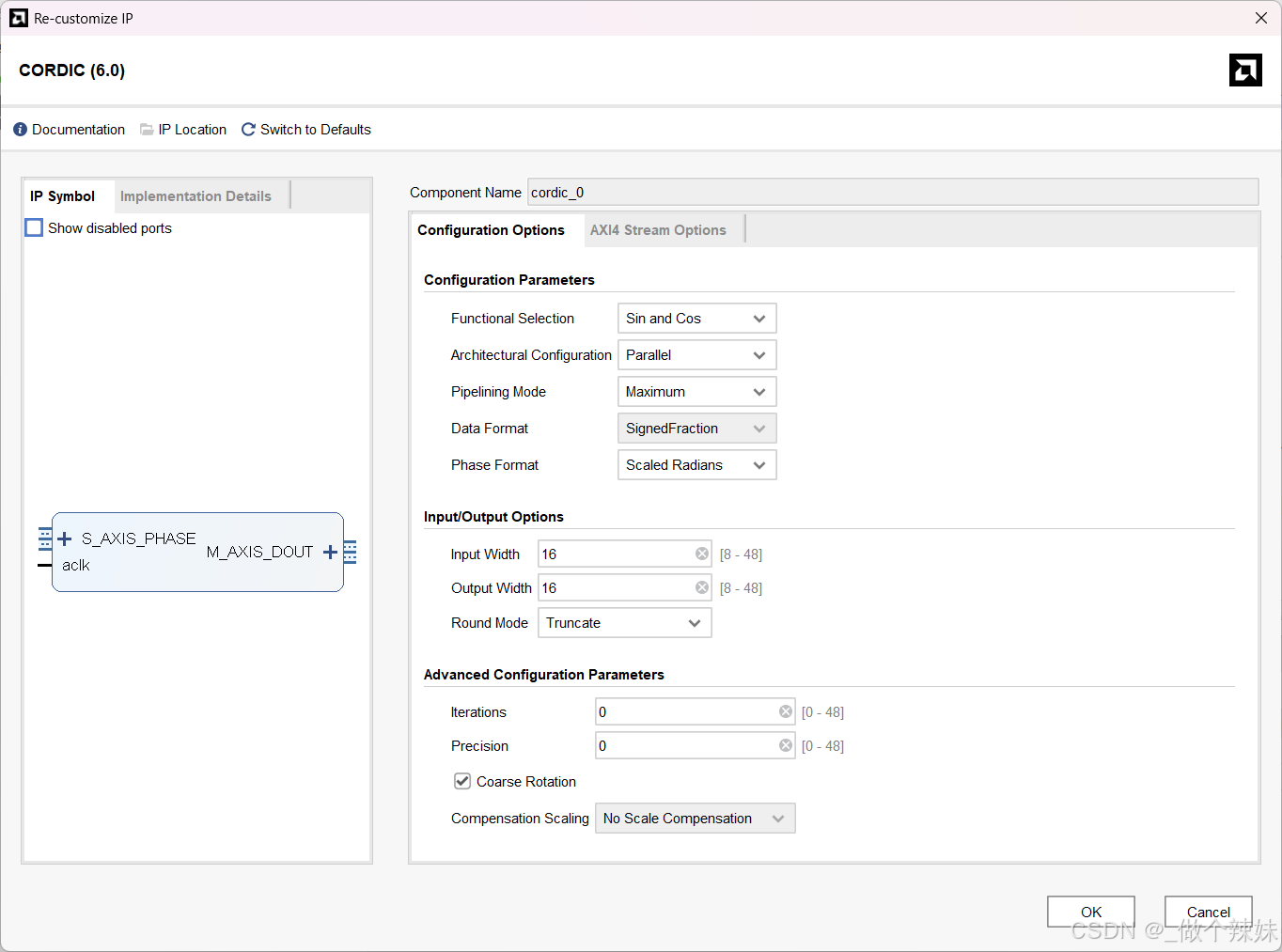

CORDIC IP核的使用,文章包含IP核的配置以及示例所用的HDL、testbench代码

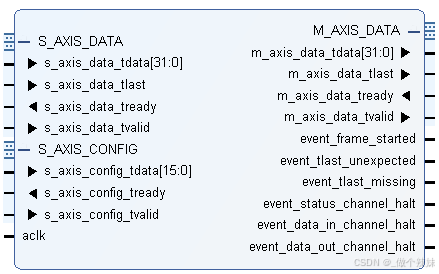

FFT IP核详述,每个参数的含义,配置说明,输入输出接口描述,并结合仿真结果展示实例

使用 FIFO IP 核完成数据读写,内容包括:FIFO 介绍、IP 核配置详解、时序波形图分析、仿真结果、上板验证结果

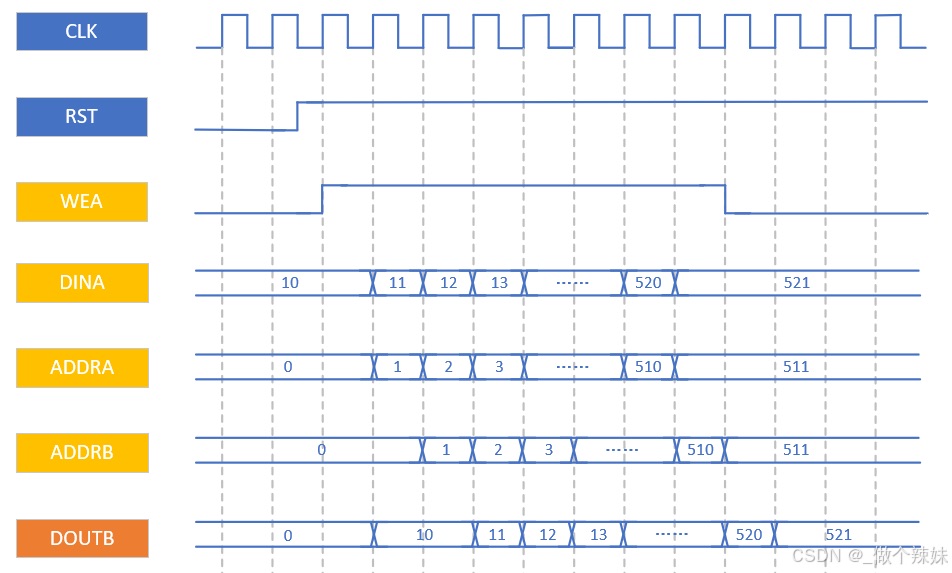

添加 Block Memory Generator IP核,对FPGA内部的 RAM 进行数据读写操作。包括:时序波形图分析、HDL代码、testbench代码、仿真结果、上板验证结果

ESP32开发 WIFI篇——极简代码连接wifi,模拟设备连接阿里云

python 语言编写监听 TCP 端口的代码,ESP32 与云服务器的连接,附完整客户端、服务器端代码

本文介绍了基于VIP的APB验证框架结构,主要包括config配置、interface接口定义、sequence序列生成、agent代理组件以及测试环境搭建。框架详细实现了APB协议的主从设备交互功能,包含读写操作、burst传输、数据校验等验证点。测试案例通过连续写、连续读、读写交替等场景验证APB功能,利用config机制控制组件激活,并通过sequence库实现多样化的激励生成。该验证框架采

CORDIC IP核的使用,文章包含IP核的配置以及示例所用的HDL、testbench代码

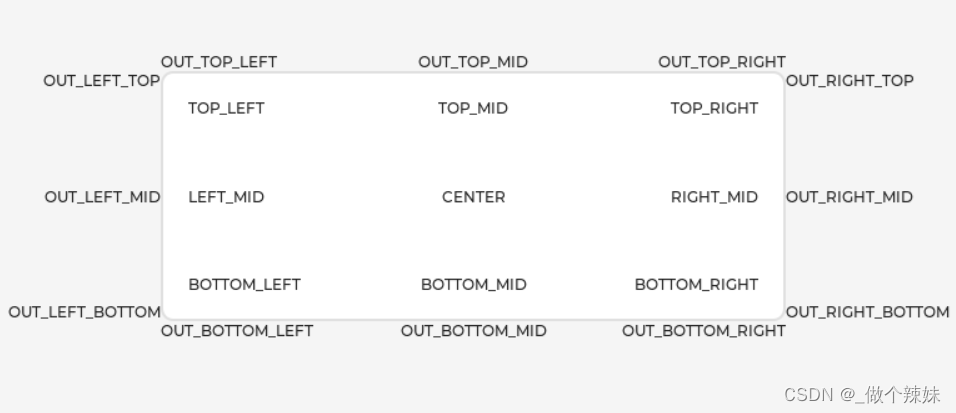

使用 ESP32 驱动 ST7735 128*160屏幕,使用 lvgl 和 lvgl_esp32_drivers,参考 lv_port_esp32 创建工程,完整说明移植过程,同时解决ST7735显示方向受限问题,并给出常见的花屏问题解决方案

本文使用的LVGL版本为7.x。介绍了常用的API 并给出了相应解释