简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

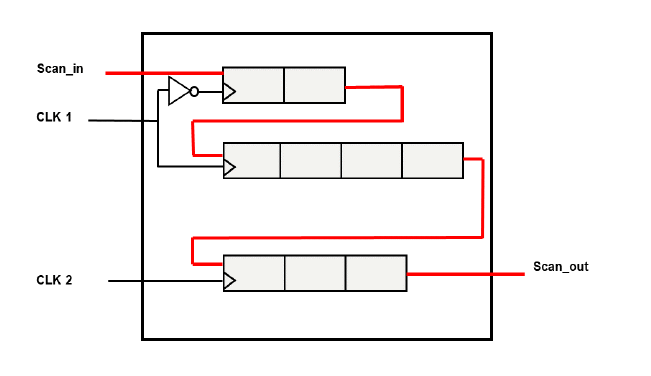

人为无法干预,如果想精细化到哪个cell需要在哪个cell之后,则需要用到以下的方法。因为scan family本身特性要求不同family不能放在一条chain,所以出来了两条chain。使用这种方法指定的cell次序可以与其他cell融合成一条chain,效果更优。这种方法与scan family是互斥的,所以需要删除之前的chain分配方案。4.通过scan family控制cell串cha

理想的时钟树(ideal clock tree)假设时钟源具有无限驱动(infinite drive)能力,也就是说,时钟可以无延迟地驱动无限多的单元。例如,如果时钟树有500个端点(endpoints),并且Skew为50ps,则表示最长时钟路径和最短时钟路径之间的时间差为50ps。在时钟树综合之后指定clock uncertainty时,不包括skew,只包括jitter,因为此时时钟树有实际

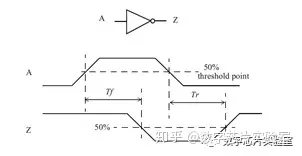

VOH是指输出引脚为逻辑1时的最小电压值。电路输出通常会带有负载或者驱动下一级的输入,VOH/IOH参数测试是为了检验DUT引脚在规定的电流条件下,输出电压是否可以按要求保持逻辑1的状态;VOL是指输出引脚为逻辑0时的最大电压值。电路输出通常会带有负载或者驱动下一级的输入,VOL/IOL参数测试是为了检验DUT引脚在规定的电流条件下,输出电压是否可以按要求保持逻辑0的状态。在数字电路中,定义输入电

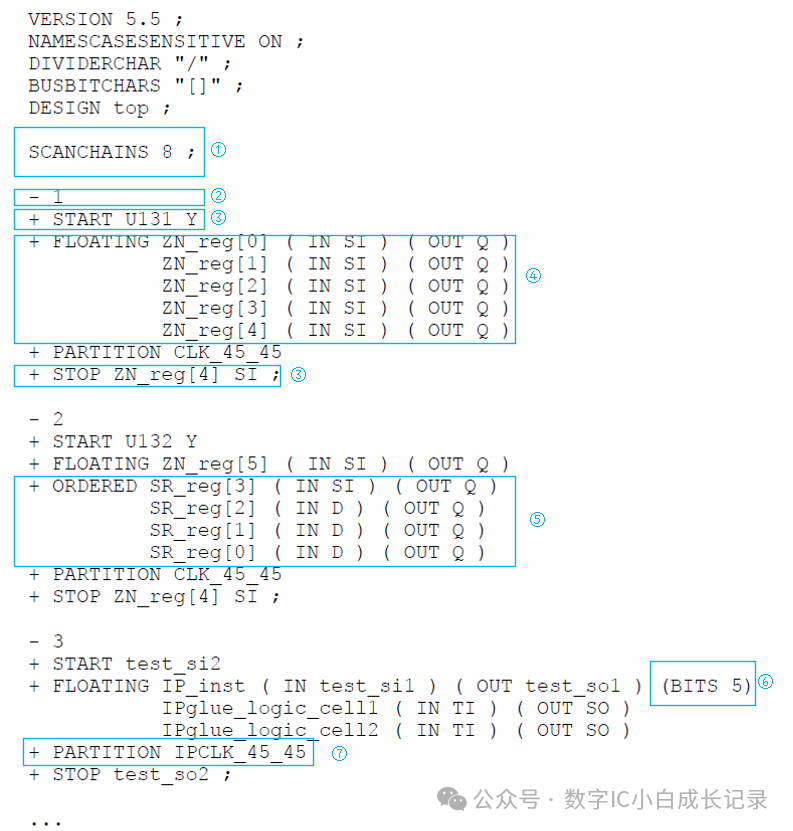

因此,scandef就可以作为中间桥梁来为scan reorder和scan repartition的操作传递这些约束信息,后端工具不需要理解复杂的dft约束,只需要遵循scandef的描述来进行优化操作就可以了。scandef文件中并不会包含design中所有的scan cell,只包含了design中可以被reorder和repartition的scan cell的信息,不能优化的scan c