简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

上一篇文章我们介绍了ScalaTest,它是Scala和Java的测试工具。而现在Chisel模块最新的标准测试工具是ChiselTest,它是基于ScalaTest的,允许我们用于Chisel测试。为了使用ChiselTest,我们同样需要在`build.sbt`里面包含`chiseltest`的库。...

前面的部分已经看到过很多函数了,现在我们可以自己定义函数然后高效利用它们了。最后,我们会利用Scala中函数式编程的特性,用Chisel实现可配置激活函数的神经网络神经元。

Scala是一个强类型的编程语言,这是把双刃剑:不好的方面,很多可以在Python上解释并执行的程序,在Scala中连编译都通过不了,因为Python是个动态类型语言;好的方面,Scala中编译通过的程序在运行时就会比Python产生更少的错误。这一篇的目的是让我们更了解作为Scala中一等公民的数据类型(types)。刚开始我们可能觉得自己写代码效率很低,但很快啊,我们就会学会去理解编译时的错误

本系列是基础的Chisel教程系列,基于官方的Chisel-Bootcamp,结合了很多Scala的知识,中间补充自己在探索过程中的思考,还会补充一些其他Chisel相关内容,这一系列的目标是基本掌握Chisel语言,为后续设计实现CPU打下坚实基础!...

本系列是基础的Chisel教程系列,基于官方的Chisel-Bootcamp,结合了很多Scala的知识,中间补充自己在探索过程中的思考,还会补充一些其他Chisel相关内容,这一系列的目标是基本掌握Chisel语言,为后续设计实现CPU打下坚实基础!...

一个CPU或者其他数字芯片,本质上都是一个大型的数字逻辑电路,如果设计一个硬件描述语言来设计CPU,必然需要支持所有数字逻辑电路的基本组件,Verilog如此,Chisel当然也不例外。这一篇文章我们就以组合逻辑电路为例,对比Chisel和Verilog的基本语法。......

上一篇的结语中提到,`UInt`、`SInt`和`Bits`都是Chisel类型,它们本身是不直接表示硬件的,只有把它们封装成为`Wire`、`Reg`或`IO`才会生成电路。这件事可以这么理解,数字逻辑电路是由连线、逻辑门、寄存器和输入输出(包括时钟和复位信号)等组成的,其中连线对应`Wire`,逻辑门对应运算符,寄存器对应`Reg`,输入输出对应`IO`。那么在Chisel中它们到底怎么使用呢

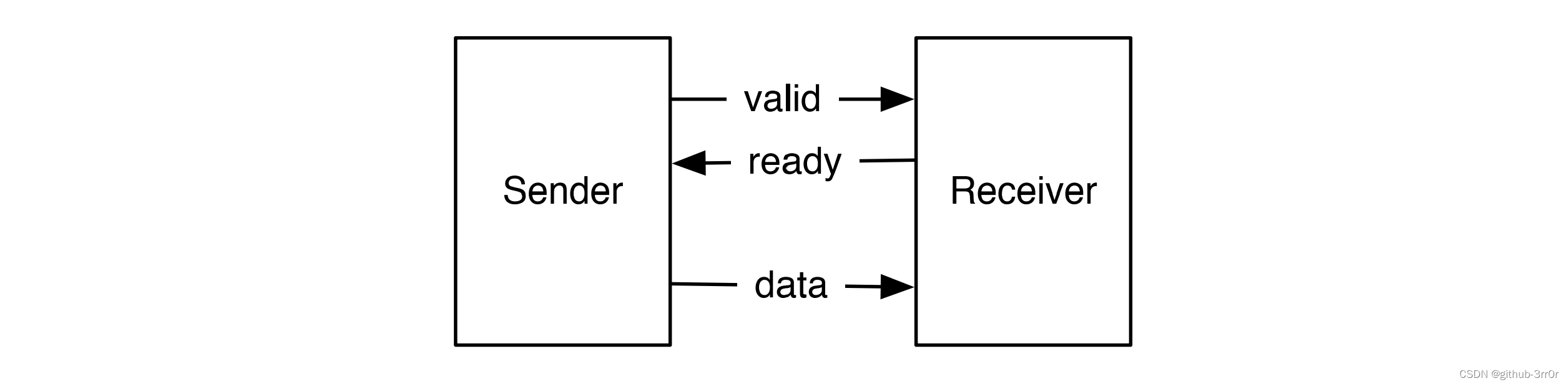

上一篇文章以Popcount为例,介绍了带数据通路的有限状态机FSMD的写法与实现,对于后面写复杂的系统有很关键的指导意义。我们可以注意到,在FSMD的实现中,状态机之间的通信我们使用了`Ready-Valid`握手协议,这是一种常见的通信接口协议,但每次都这么写显然有点复杂。而Chisel中自带了`Ready-Valid`相关的函数`DecoupledIO`,用于对数据信号进行`Ready-Va

上一篇文章介绍了移位寄存器的实现和两种常用的移位寄存器,在实现串口通信的时候会很有用,对后面的高速接口设计可能又会有一定启发。在数字设计中,不仅仅有寄存器可以保存电路的状态信号,内存(Memory,或叫作存储器,本文都用内存称呼)也是可以保存状态信息的,在处理器设计中内存还用于程序代码和数据的存放,因此十足重要。这一篇文章我们就一起来学习Chisel中的内存实现尤其是同步内存的实现和初始化。...

上一部分我们学习了简单的组合电路,这一部分介绍时序电路,与组合电路相比多了时序和状态,但也相比来说也并不是很难的东西。而时序电路对于数字设计来说特别重要,我们当然可以构造一个单周期的复杂系统,比如实现一个单周期的RISC-V处理器。但是由于这一个周期要做的事情太多太多,因此周期很长,时钟频率上不去,性能自然高不了。而时序电路是流水线的基础,通过将复杂电路划分为若干流水线阶段,既可以提高时钟频率,又