简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

/设置复选框的指示器部分样式(LV_PART_INDICATOR 和默认状态 LV_STATE_DEFAULT)//设置复选框的样式(主部分 LV_PART_MAIN 和默认状态 LV_STATE_DEFAULT)//设置文本的字体为 lv_font_montserratMedium_16,这是一种中等大小的字体。//设置复选框指示器背景的渐变方向为 LV_GRAD_DIR_NONE,即没有渐变。

标签的原型就是标签更改文本即可,而按键可以用:lv_win_add_btn_right(win, LV_SYMBOL_CLOSE)添加到窗口头的右侧,如果要在窗口头的左侧添加按钮,可以用lv_win_add_btn_left(win, LV_SYMBOL_CLOSE)代替。第二个参数是一个图像源,因此它可以是一个符号、指向lv_img_dsc_t变量的指针或文件的路径。按钮的宽度可以用lv_win

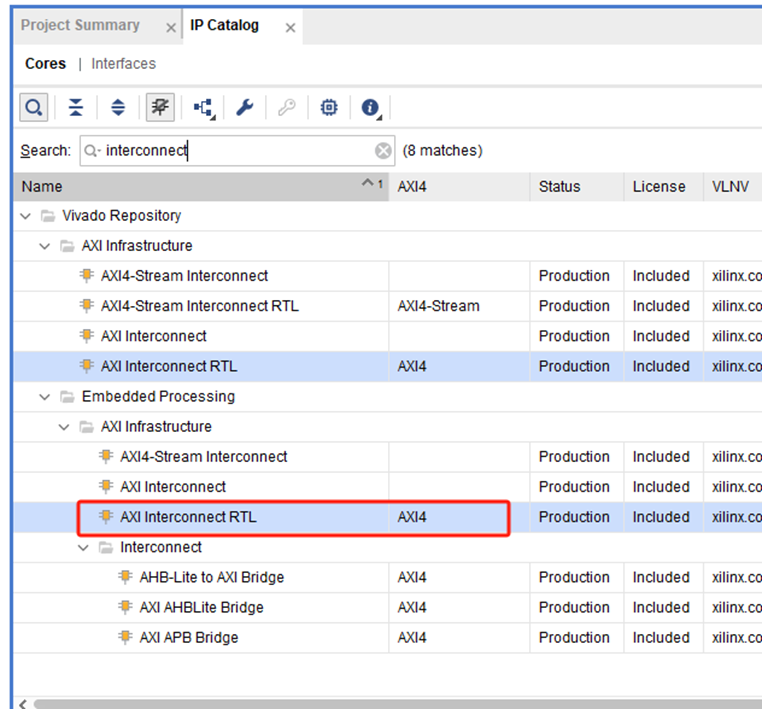

只有一个主设备,四个从设备,多个主机读写一个从机是通过主机的ID号不同来实现的,每个主机具有不同的ID号,连接到AXI Interconnect RTL IP的从机接口,AXI Interconnect RTL IP的主机接口连接到DDR4。在这里将主机id位宽设置为4,那么作为从机的DDR4的id位宽为8。在interfaces界面中,数据位宽为512位,不进行转换,使用异步时钟,仲裁模式选择轮

我们在使用一些以太网PHY和FPGA接口是RGMII接口是DDR双沿结构,还有ADC芯片也也是DDR双沿采样接口,以及CMOS视频传感器也有很多DDR双沿源同步接口。我们这里以IMX222视频传感器的的DDR为例约束input ddr 接口如何进行约束和时序分析以及收敛源同步边缘对齐fpga输入直接模式(输入端不加PLL)这是IMX222手册中DDR接口的时钟和数据的边缘对齐的源同步时序参数,此参

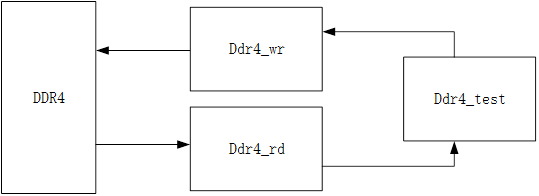

DDR4写模块根据ddr4_test模块发来的写开始信号,写数据数量,初始地址,首先通过写地址通道发送写数据的初始地址、写数据数量、和控制参数,wstrb信号作为写数据的掩码。在DDR4读模块中,根据ddr4_test模块发出的读开始信号,在读地址通道中发送读起始地址、读长度和控制信号,给DDR4发起读请求,根据读数据通道读出数据,rd_data作为读数据,rd_en作为读数据有效信号发送给ddr

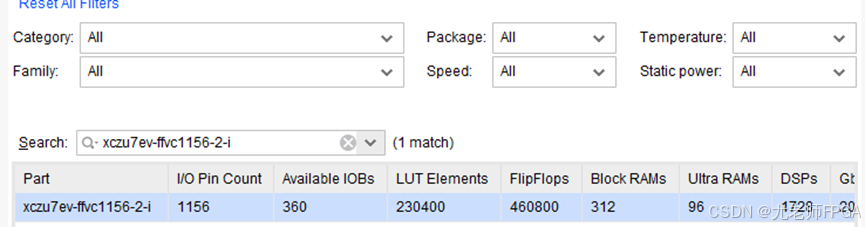

这种高带宽对于大量的数据的应用非常重要。对于Controller/PHY Mode 的选择,我们使用Controller + PHY模式,Xilinx UltraScale/UltraScale+等高端FPGA通常包含硬核PHY,选择Controller + PHY模式可直接利用硬核,降低功耗和延迟,并且此模式的开发更易上手。在Basic页面下,首先勾选上AXI4 Interface选项,我们选用

在创建完DDR4的仿真模型后,我们为了实现异步时钟的读写,板卡中在PL端提供了一组差分时钟,可以用它通过vivado中的Clock Wizard IP核生成多个时钟,在这里生成两个输出时钟,分别作为用户的读写时钟,这样就可以用异步时钟来读写ddr4数据。在基本配置中可以使用时钟输入(clk_in),时钟输出(clk_out),复位(reset),时钟锁(locked)等信号来完成Clock Wiz

所以只要根据fifo_1的几乎满(wrfifo_almost_full)信号为低电平状态就可以控制数据写入,根据fifo_2d的空(rdfifo_empty)信号为低电平状态就可以控制数据输出。如果写入的数据和读取的数据不相同,error_1就会拉高,可以通过error_1的状态判断ddr循环读写的功能是否正确。上图中,可以看到,读出的数据数量和存入的数据数量相等,并且可以观察到,测试工程中可以存

使用ZYNQ芯片和LVGL框架实现用户高刷新UI设计系列教程(第四讲)

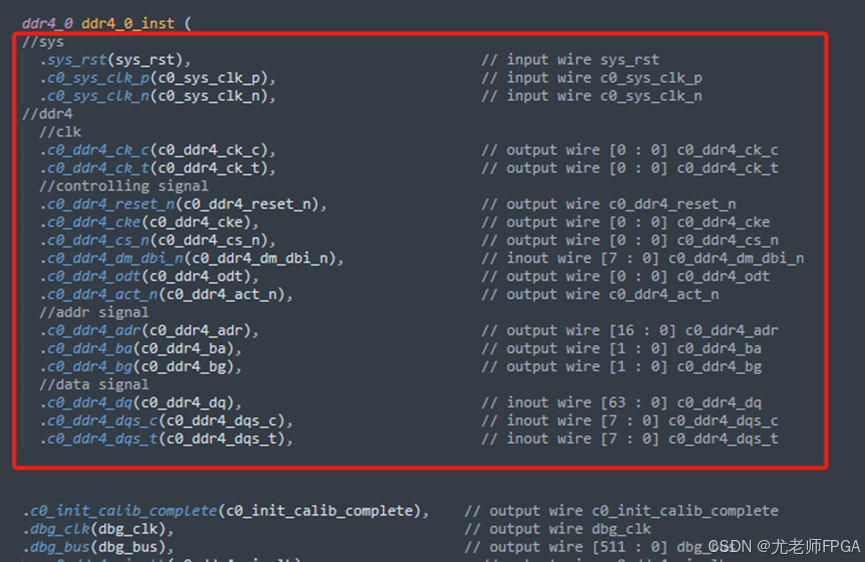

说明:ddr4 ip 接口的awlock、awcache、awprot、awqos、arlock、arcache、arprot、arqos信号在工程中没有特别要求,可以设置为0。核心模块在PL侧搭载了4片镁光(Micron)的DDR4内存,单片内存大小为1GB,数据接口16bit。在上一章我们已经把DDR4的IP核配置好了,这一章来描述一下DDR4 IP核的例化接口,以及接口的作用。awqos(a