简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

芯片流片成本惊人,工艺越先进烧钱越狠:3nm一次流片高达1亿美元,28nm也要200万美元。主要成本来自掩膜版(3nm需140+层,超1100万美元)和晶圆(3nm单片近2万美元)。以12nm安防芯片为例,首轮验证20片就需621万美元,单颗成本776美元;量产5000片才能摊薄至17美元/颗。40nm芯片验证10片成本94万美元,量产1万片才能将掩膜成本占比从94%降至2%。此外还需支付IP授权

在芯片设计中端流程时,景芯SoC会插入UPF约束中的isolation等cell,但是无法插入power switch等cell,因此,作为power switch cell的控制信号pwrdown_mux在没有负载的情况下,会被裁员掉(优化掉),因此需要设置上面MUX器件为dont_touch或者使pwrdown_mux成为module的port并禁止auto_ungroup(并设置no_bou

假如电源的工作电源为1.2V,当B模块关断电压后,B模块输出到A模块的信号(X态)可能为0~1.2V中任意电压,如果X处在中间电平0.6V,若这个信号送给电压常开域中的一个反相器,就会导致这个反相器的PMOS和NMOS都导通,就会存在一个短路电流从电源流经PMOS、NMOS再到地,造成功耗浪费。因此,当A模块电压常开,B模块电压可关断,在B模块关断电压后,B模块输出到A模块的信号需要用isolat

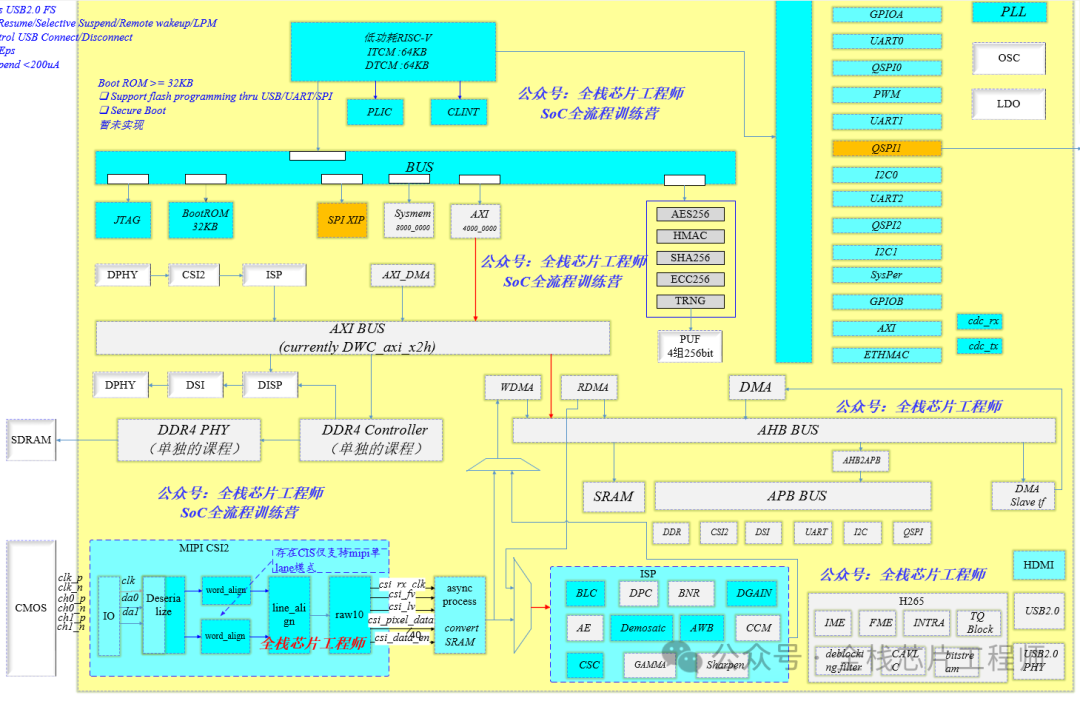

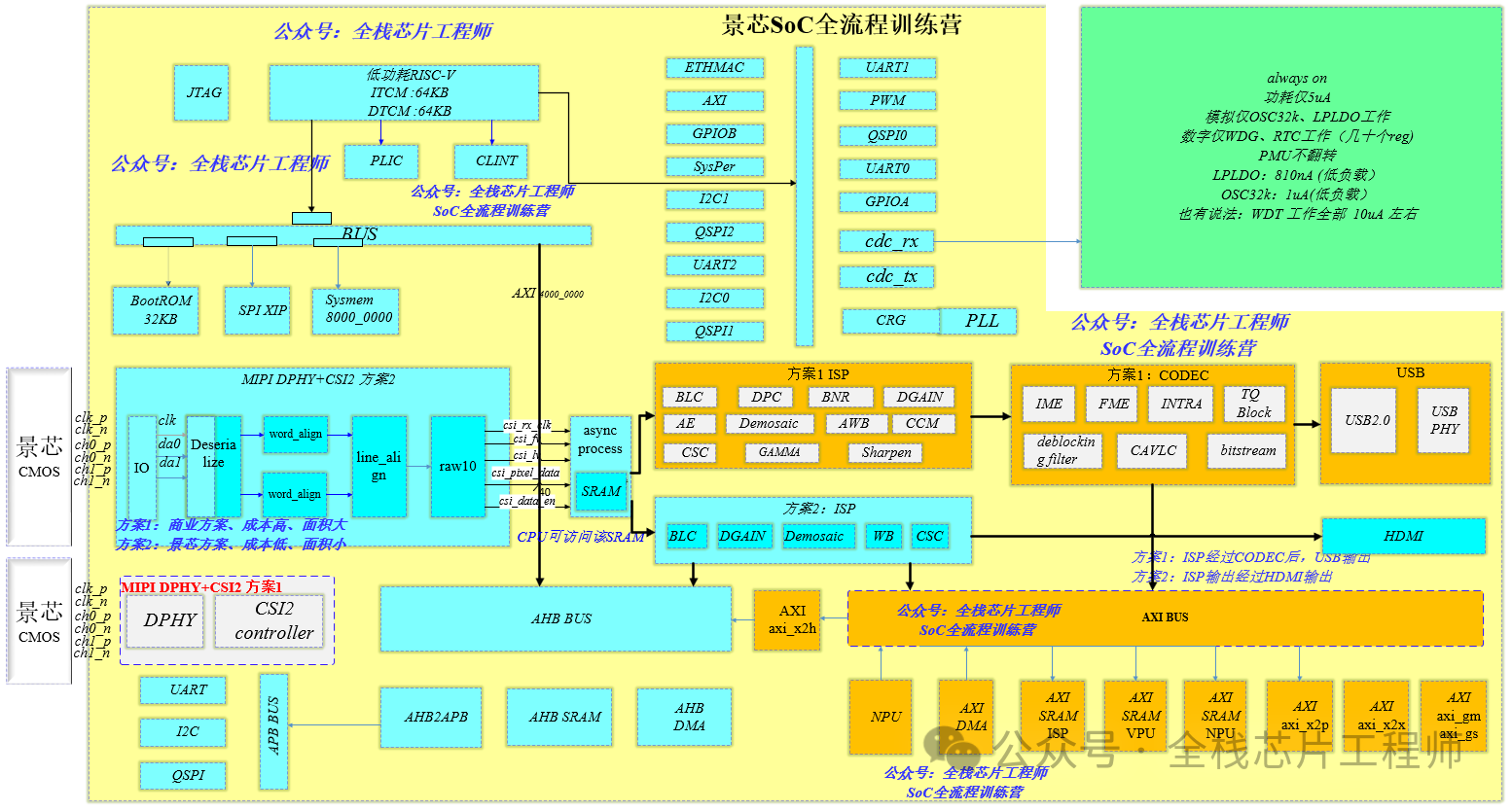

注意,景芯SoC休眠掉电时,将关键数据保存在SRAM,SRAM采用双电源设计,这样设计不仅节省了面积,还降低了设计复杂度。】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。大量使用有什么影响?提供后端设计服务,工艺包

对于LC振荡电路来说,一般产生的正弦波频率较高,若要产生频率较低的正弦振荡,势必要求振荡回路要有较大的电感和电容,这样不但元件体积大、笨重、安装不便,而且制造困难、成本高。而振荡器通常产生固定频率的信号,振荡器的频率通常由其设计决定。PLL的设计和实现通常比振荡器复杂,功耗更高,成本更高,PLL常用于需要精确频率控制和低相位噪声的应用,而振荡器则用于对频率精度要求不高的场合。每种振荡器都有其特定的

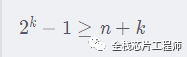

ECC纠错算法汉明码实现原理汉明码(Hamming Code)是广泛用于内存纠错的编码。汉明码不仅可检错,还可纠错。(只能发现和纠正一位错误,对于两位或者两位以上的错误无法纠正)。我们约定一串编码里1的个数是偶数个,那么这串编码里携带的信息就是对的,否则就是错的。我们可以在开头对这串编码加一位校验码实现奇偶校验。比如:我们想传输10010这串码,那么在传输的时候,就传010010,其中在开头的0就

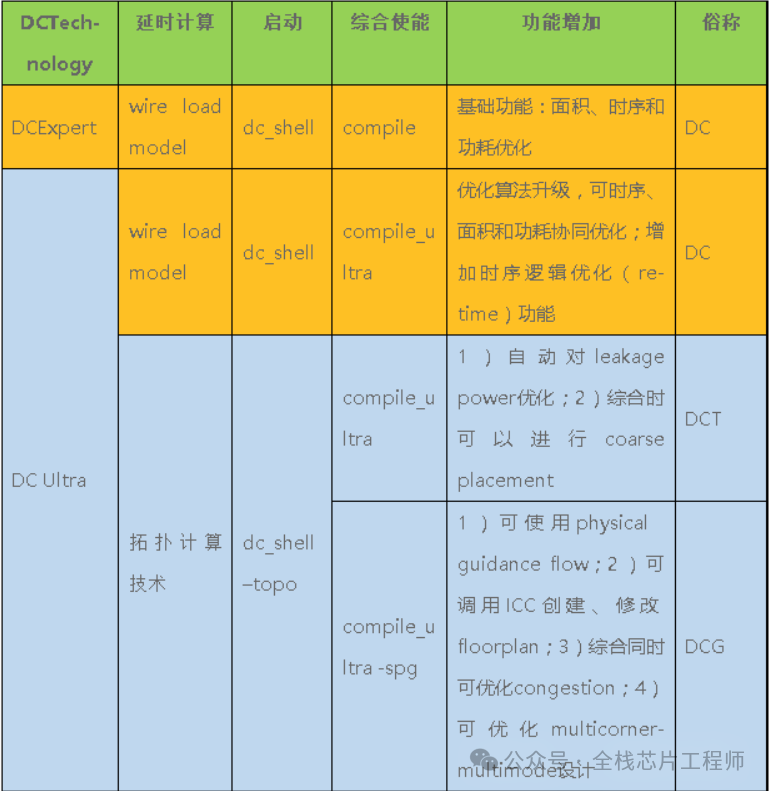

随着半导体工艺的进步以及芯片设计的日趋复杂化,传统OCV约束方式已经越来越不符合45nm及以下工艺的千万门级高速芯片设计。相对于传统OCV在path上设置统一derate值的方法,AOCV更为科学与合理的根据path的实际情况加上不同的derate值。通过科学合理的方法降低了derate值的悲观度。欢迎关注我的公众号:全栈芯片工程师上一篇OCV、AOCV时序分析(一)介绍了OCV、AOCV的原理及

时序弧静态时序分析是基于时序弧数据的时序分析。时序弧是用来描述两个节点延时信息的数据,时序弧的信息一般分为连线延时和单元延时。连线延时是单元输出端口和扇出网络负载之间的延时信息;单元延时是单元输入端口到输出端口之间的延时信息。因此一条完整路径的时序信息计算由连线延时和单元延时组成。连线延时没有功能属性,所以延时信息在分类上没有区别。单元延时中的时序弧分为基本时序弧和约束时序弧两类,其中约束时序弧用

时钟树是以平衡为目的,假设对一个root和sink设置了400ps的latency值,那么对另外的sink而言,就算没有给定latency值,CTS为了得到较小的skew,也会将另外的sink做成400ps的latency。再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:请问,如果iso cell输出都要放parent,输入放self,那么下面-applies_to_output

DVFS技术是数字后端设计中重要的低功耗技术之一。通过动态调整工作电压和频率,可以有效降低芯片的功耗,延长设备的使用寿命,并减少能源消耗。然而,DVFS技术的实施需要克服时序收敛的复杂性和工作负载预测的准确性等挑战。通过合理的策略和精确的控制,DVFS技术能够在保证性能的同时,实现功耗的优化。“2.5GHz频率 hierarchy DVFS低功耗A72培训”编辑一. 培训内容:2.5GHz hi