简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

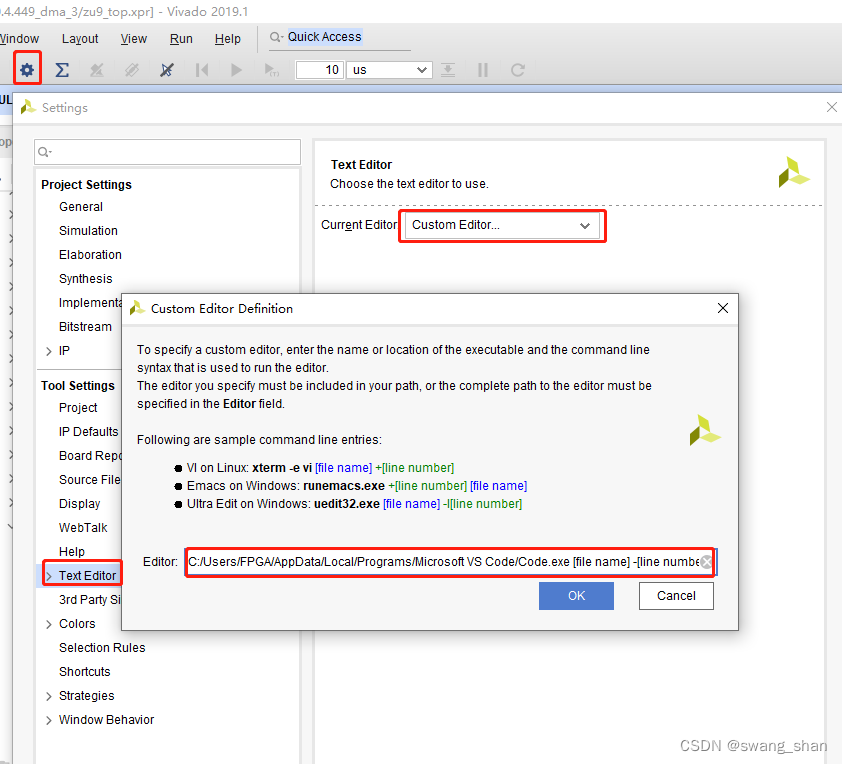

vivado-vscode 新手使用说明 - verilog

vscode联合vivado使用

vivado仿真出现问题:Failure: ERROR:add_1 must be in range [-1,DEPTH-1]

在进行 fir IP核仿真时出现的问题。解决方法:将滤波器的所有输入(此处为tdata / tvalid)均配置默认数据。此问题出现的原因:没有给ip的输入赋值,导致ip核运行出问题。

[IP_Flow 19-3805] Failed to generate and synthesize debug IPs.

问题原因:路径太长了解决方法 :把工程的路径改短

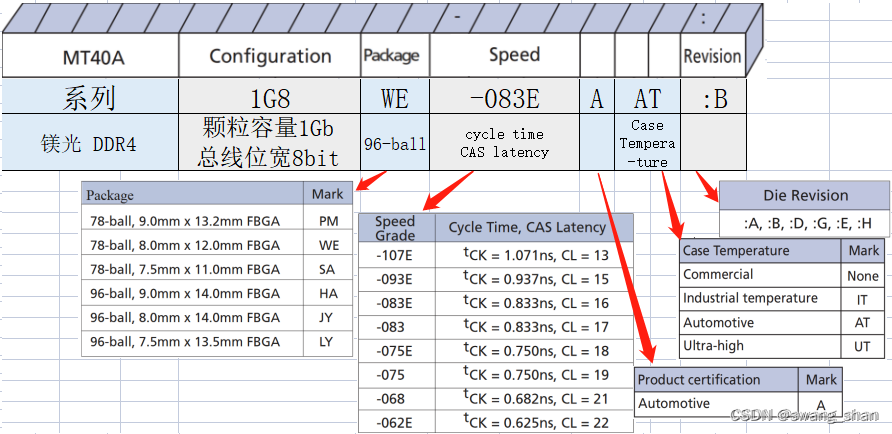

从DDR4芯片名称开始了解DDR4 --- 个人笔记

了解DDR4的基本内容

MUX数据选择器

数据选择器(multiplexer):在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,也称多路选择器或多路开关。 产品规格 有4选1数据选择器、8选1数据选择器(型号为74151、74LS151、74251、74LS153)、16选1数据选择器(可以用两片74151连接起来构成)等之分。如在数字电路中,mux6常指6路开关、mux6to1(mux6_1)常指6选1数据选择器。...

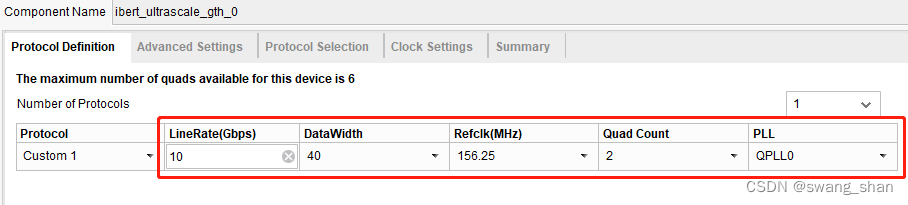

ibert测试 - UltraScale+

高速口使用前最好先进行ibert测试,确保高速口的硬件是没有问题的。

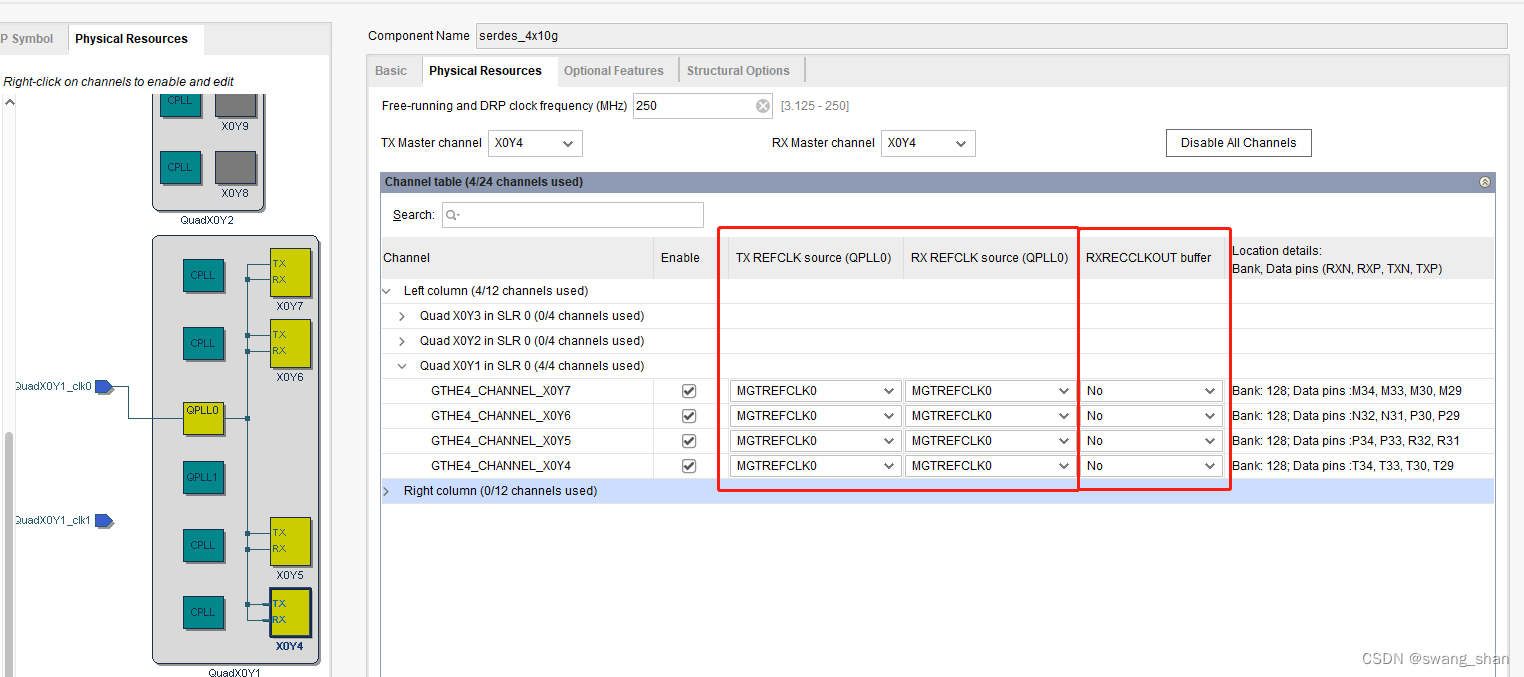

UltraScale+ GTH ip核使用

主要介绍GTH的IP核使用。

到底了