简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

的各子状态进行迁移,甚至不需要等到前一个迁移完成后才请求更改为另一个,因此当完成一个子状态的更改时,软件必须检查目前的配置,如果与设置的子状态不匹配,它必须重新更改为配置的值。如果输入的请求(配置或消息)导致了一个错误,那么在该状态下会发送一个错误消息;如果输入的请求(配置或消息)导致了一个错误,那么在该状态下会发送一个错误消息;在该状态下,可以进行配置和消息请求,不支持处理除此之外的所有其它请求

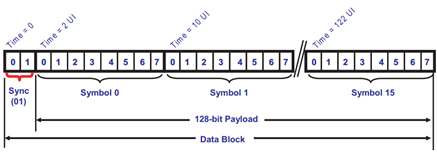

与以太网中使用的64b/66b编码类似,128b/130b无法像8b/10b编码那样将连续的0(或者连续的1)限制在较小的范围之内,理论上,128b/130b可能出现的最大的连续0(或者连续1)可以达到128(最坏的情况下)。除了TS1OS和TS2OS之外的所有的Ordered Set的所有Symbol都不会被扰码,TS1OS和TS2OS的Symbol0不会被扰码,Symbol 1~13会被扰码,

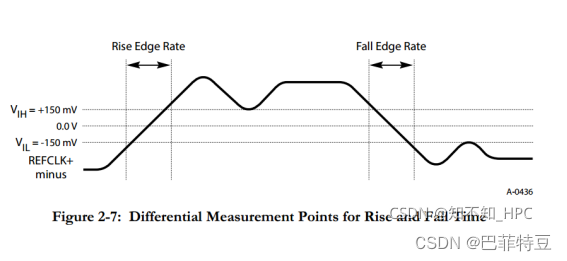

2)测试方法:以REFCLK+和REFCLK-的中心交叉点为中心的±75mV的窗口内。示波器统计测量一段时间内的VMAX & VMIN。2)测试方法:大量周期波形叠加,每个周期的REFCLK+上升沿与REFCLK-下降沿瞬时电压值相等的交叉点叠加后得出的统计区域。1)测试对象:单端波形REFCLK+的上升沿、REFCLK-的下降沿。1)测试对象:差分波形(REFCLK+减REFCLK-)。1)测试

对于PCIe总线的数据传输,我们知道其相对于PCI和PCI-X并行总线的极大不同点是使用了点对点式的差分串行链路进行信号传输,信号上已经没有并行总线的同步时钟。但任何电路都需要时钟进行驱动,特别是总线信号,发送端需要时钟驱动打出信号,接收端则需要时钟采样信号,进而识别信息。PCIe信号属于差分信号,也是同步传输方式,但是没有专门的同步时钟!我们在设计电路时,通常会提供一组100MHz差分时钟给后端

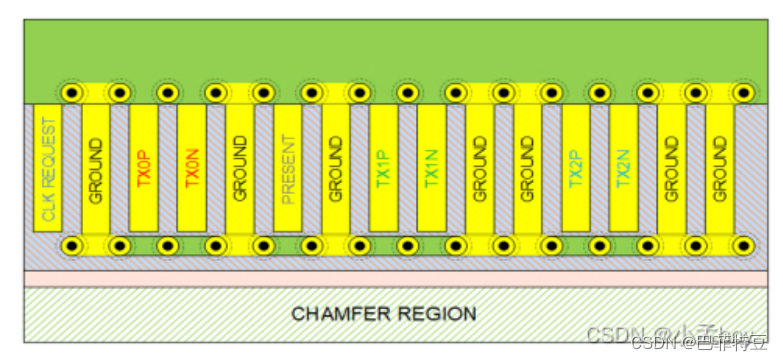

AIC金手指区域必须设计内层GND平面,以屏蔽金手指两面的串扰,这些平面从金手指北侧向外延伸1.5mm到金手指下方区域,能够有效覆盖金手指的上方1.5mm长度,屏蔽了连接器接口Tx和Rx主要的近端串扰(NEXT)。AIC应该在靠近倒角位置布置间隔1mm的GND孔,这些地孔通过和内层的GND平面相连,进一步抑制金手指边缘区域的串扰。这些过孔有效地镜像了金手指北侧的地孔。在金手指的最中间层,向外延伸3