简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

基于 KV260 + PCAM_5C 构建视频通路,通过 PYNQ 可视化图像,用以进一步处理图像数据,从 MIPI 至图像数据,包括如下要点:在 PYNQ 下通过 IIC 配置 OV5640配置 MIPI CSI-2 Rx subsystem 经验汇总AXI4-Stream 基础设施配置 Sensor Demosaic经验汇总配置 AXI VDMA经验汇总Sensor OV5640 时钟树图像数

本文以官方 A to Z Bare-metal Flow 为基准,在 VD100 硬件平台上实现的例子。包含如下内容:申请 AIE License创建 Vivado 可扩展平台(XSA)创建 Vitis 平台(XPFM)创建 AIE 应用创建 HLS 应用系统集成:VPP 链接 pl_app、aie_app创建 ps_app 应用系统集成:打包生成 sd_card.img在 VD100 硬件平台上

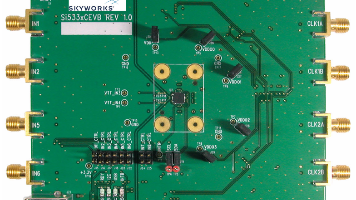

本文介绍了 Si5338 EVB 的功能和配置,以及 Si5338 芯片的特性。文档深入解析了 EVB 的可编程电压功能,包括 GUI 配置和基于 AD5263 数字电位计及 MAX8869 稳压器的原理。供电部分阐述了 VDD 和 VDDOn 对芯片和接口的影响。

本文主要介绍使用Vitis AI工具创建自定义的Xmodol,难点并不在工具本身,而是需要了解很多机器学习的知识。一个很好的出发点是使用Vitis Model Zoo库,是一个包含了大量预训练模型的资源库,这些模型涵盖了多种AI应用领域,如图像分类、目标检测、语义分割、人脸识别、自然语言处理等。

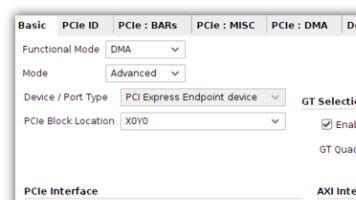

本文分享了Xilinx XDMA驱动调试的实用指南,涵盖H2C数据传输测试和性能优化。

分享 Vivado 远程开发的一些实用干货:远程 JTAG Debug远程综合实现(Run on remote hosts)vmWare 网络配置NFS 文件共享X11-forwarding

本文详细介绍了使用KV260视觉AI套件中的DPUCZDX8G深度学习处理单元(DPU)的环境搭建和开发流程。DPUCZDX8G是专为Zynq UltraScale+ MPSoC设计的,优化了卷积神经网络的计算引擎,支持广泛的运算符,使其成为执行AI推理任务的强大工具。文章从DPU的基本原理出发,解释了其工作机制,包括如何从片外存储器中提取指令以及如何在片上存储器中高效处理数据。

本博文分享在 VD100 硬件平台上,通过 Petalinux 2024.2 构建 Linux 的过程。包括:Petalinux 2024.2 的下载与安装;在 VD100 硬件平台构建 Linux 全过程;SDT 生成设备树的方法;SD 卡分区;一些常见异常的汇总和分析;

在这个快速发展的技术世界中,Zynq SoC芯片的出现无疑是一次革命性的进步。它将ARM处理器的强大计算能力与FPGA的灵活性完美结合,为工业控制和视觉AI应用带来了前所未有的便利。通过Zynq,开发者可以在同一芯片上同时进行软件和硬件的开发,这不仅简化了开发流程,还显著提高了效率。

在这个总结中,我们探讨了Resnet50,这是一个由50层构成的深度卷积神经网络,它在图像识别任务中表现出色。通过“残差学习”的创新设计,Resnet50解决了深度网络训练中的退化问题,使得网络能够通过增加更多的层来提高性能,而不会增加训练难度。我们还分析了如何在Xilinx Zynq平台上使用VART运行Resnet50模型的代码,包括模型加载、数据预处理、异步推理和结果分类。这个过程展示了如何