51单片机总结【引脚、时钟电路、复位电路、I/O端口、内部结构】

掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。对P3端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。此外,P1.0和P1.2分别作定时器/计数器2的外部计数输入(P1.0/T2)和时器/计数器2 的触发输入(P1.1/T2EX),具体如下表所示。在flash编程和校验时,P1口接收低8位地址字节。对P1 端口写“1”时,内部上拉电

1、功能简述

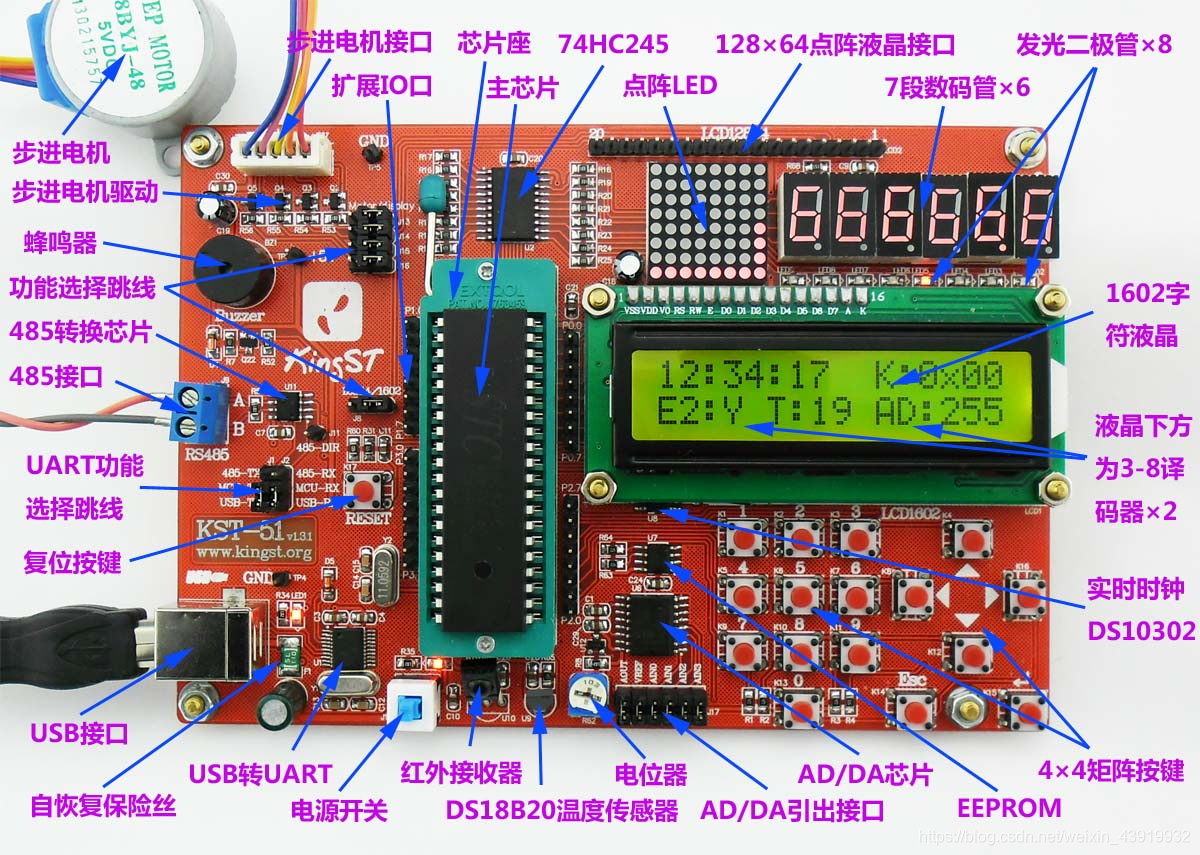

STC89C52 是一种低功耗、高性能CMOS8位微控制器,具有8K在系统可编程Flash存储器(ROM)。STC89C52具有以下标准功能:8k字节Flash(程序存储器ROM),512字节RAM(256字节内部和256字节外部),32位I/O 口线,看门狗定时器,2个数据指针,三个16位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。

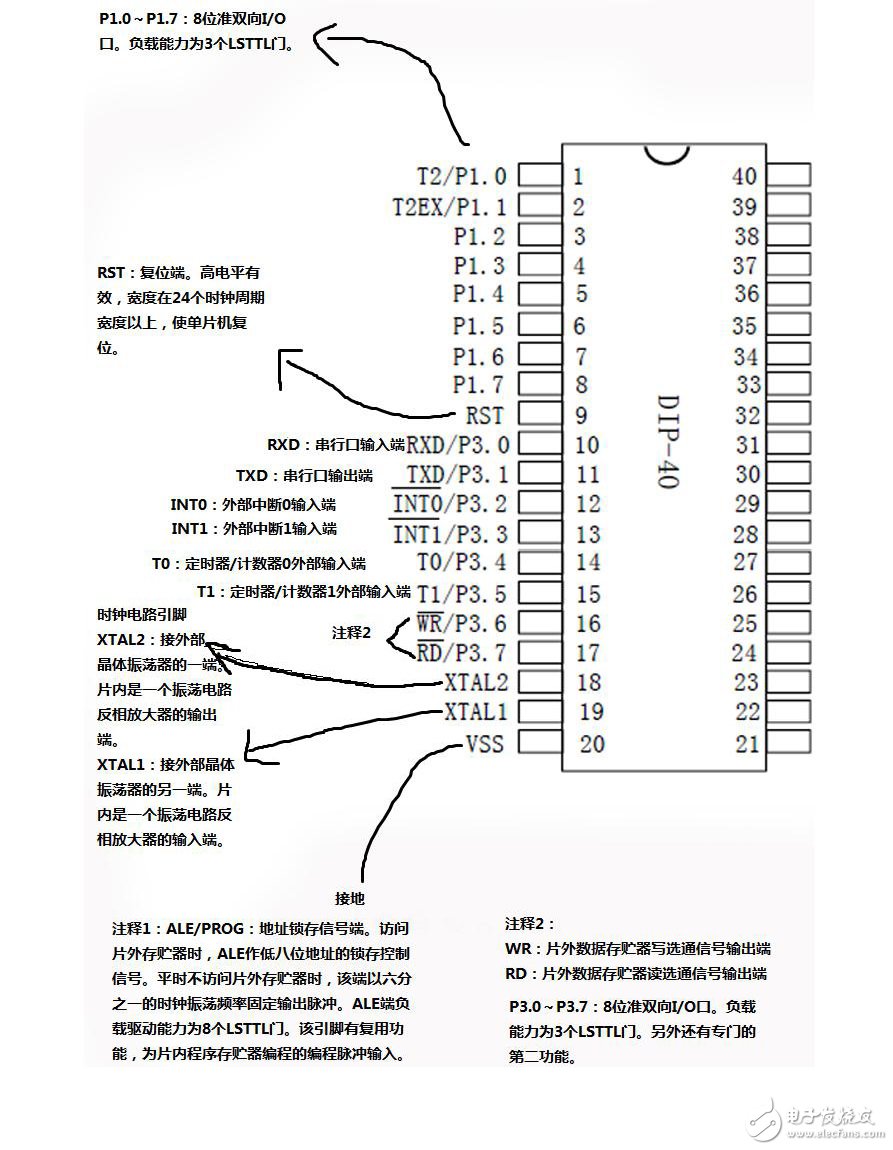

2、引脚分类

3、引脚功能

难易程度:P0>P2>P3>P1

1、P1 = 1个锁存器+一个场效应管驱动器+2个三态门缓冲期

准双向P1口:8个相同的结构电路,组成P1特殊功能寄存器(90H)

p1 输出缓冲器能驱动4个TTL逻辑电平。

用作输出端口:单片机内部相关电路除了会往给锁存器的D端送数据外,还会往锁存器CL端送写锁存器信号,内部总线送来的数据通过D端进入锁存器并从Q和端输出,当D端输入“1”,则端输出“0”(Q端输出“1”),端的“0”送到晶体管的栅极,晶体管截止,从P1端口引脚输出“1”。 当D端输入“0”,则端输出“1”(Q端输出“0”),端的“1”送到晶体管的栅极,晶体管导通,从P1端口引脚输出“0”。

用作输入端口:单片机内部相关电路会先往 P1锁存器写“1”,让Q=1、,

会使晶体管截止,关闭P1端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从 P1端口引脚输入的信号经输入三态门送到内部总线。

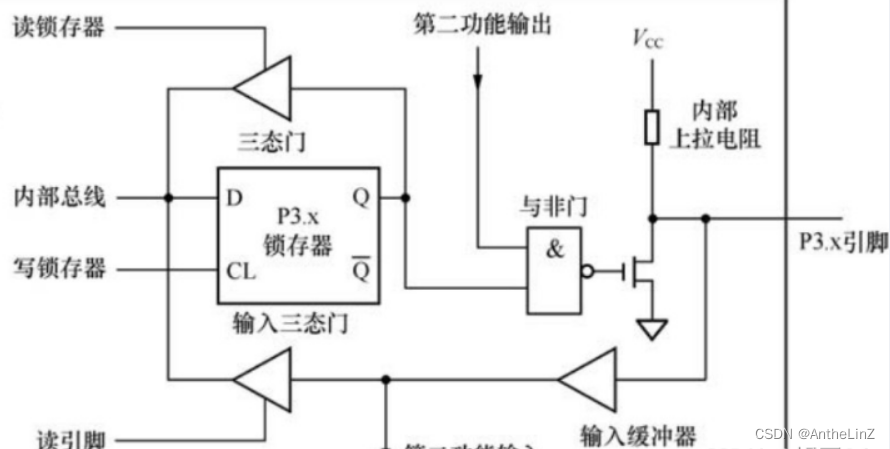

2、复用口P3特殊功能寄存器(B0H) = 1个锁存器+1个场效应管驱动器+2个三态门缓冲器+1个与非门

用作输出端口:单片机内部相关电路会送出“1”到与非门的一个输入端(第二功能输出端),打开与非门(与非门的特点是:一个输入端为“1”时,输出端与另一个输入端状态始终相反)。若要将P3端口用作输出端口,CPU给锁存器的CL端送写锁存器信号,内部总线送来的数据通过D端进入锁存器并从Q端输出,再通过与非门和晶体管两次反相后从P3端口引脚输出。

用作输入端口:单片机内部相关电路会送出“1”到与非门的一个输入端(第二功能输出端),打开与非门(与非门的特点是:一个输入端为“1”时,输出端与另一个输入端状态始终相反)。若要将P2端口用作输入端口,CPU会先往P3锁存器写“1”,让Q=1,与非门输出“0”,晶体管截止,关闭P3端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从P3端口引脚输入的信号经过输入缓冲器和输入三态门送到内部总线。

用作第二功能:

3、高8位拓展地址总线P2(A0H)= 1个锁存器+2个三态门缓冲器+1个场效应管驱动器+两路开关+非门

用作输出端口:单片机内部相关电路会送控制信号到电子开关的控制端,让电子开关与P2锁存器的Q端连接。若要将P2端口用作输出端口,CPU会通过内部总线将数据送到锁存器的D端,同时给锁存器的CL端送写锁存器信号,D端数据存入锁存器并从Q端输出,再通过电子开关、非门和晶体管从P2端口引脚输出。

用作输入端口:单片机内部相关电路会送控制信号到电子开关的控制端,让电子开关与P2锁存器的Q端连接。若要将P2端口用作输入端口,CPU会先往P2锁存器写“1”,让Q=1、,Q=1会使晶体管截止,关闭P2端口的输出电路,然后CPU往输入三态门控制端送一个读引脚控制信号,输入三态门打开,从P2端口引脚输入的信号经输入三态门送到内部总线。

用作地址总线引脚:单片机内部相关电路会发出一个控制信号到电子开关的控制端,让电子开关与内部地址线接通,地址总线上的信号就可以通过电子开关、非门和晶体管后从P2端口引脚输出。

4、低8位拓展地址总线P0口(80H) = 1个锁存器+2个三态门缓冲器+2个场效应管驱动器+两路开关+非门 +与门

用作输出端口:内部CPU会送控制信号“0”到与门和电子开关,与门关闭(上晶体管VT1同时截止,将地址/数据线与输出电路隔开),电子开关将锁存器与输出电路连接,然后CPU通过内部总线往P0端口锁存器送数据和写锁存器信号,数据通过锁存器、电子开关和输出电路从P0端口的引脚输出。在P0端口用作输出端口时,内部输出电路的上晶体管处于截止(开路),下晶体管的漏极处于开路状态(称为晶体管开漏),因此需要在P0端口引脚接外部上拉电阻,否则无法可靠输出“1”或“0”。

用作输入端口:内部CPU会先往P0端口锁存器写入“1”(往锁存器D端送“1”,同时给CL端送写锁存器信号),让,VT2截止,关闭输出电路。P0端口引脚输入的信号送到输入三态门的输入端,此时CPU再给三态门的控制端送读引脚控制信号,输入三态门打开,P0端口引脚输入的信号就可以通过三态门送到内部总线。如果单片机的CPU需要读取P0端口锁存器的值(或称读取锁存器存储的数据),会送读锁存器控制信号到三态门(上方的三态门),三态门打开,P0锁存器的值(Q 值)经三态门送到内部总线。

用作地址数据总线:单片机内部相关电路会通过控制线发出“1”,让与门打开,让电子开关和非门输出端连接。当内部地址/数据线为“1”时,“1”一方面通过与门送到 VT1的栅极,VT1导通,另一方面送到非门,反相后变为“0”,经电子开关送到VT2的栅极,VT2截止,VT1导通,P0端口引脚输出为“1”;当内部地址/数据线为“0”时,VT1截止,VT2导通,P0端口引脚输出“0”。总的来说,当单片机需要将P0端口用作地址/数据总线时,CPU会给与门和电子开关的控制端送“1”,与门打开,将内部地址/数据线与输出电路的上晶体管 VT1接通,电子开关切断输出电路与锁存器的连接,同时将内部地址/数据线经非门反相后与输出电路的下晶体管VT1接通,这样VT1、VT2状态相反,让P0端口引脚能稳定输出数据或地址信号(1或0)。

5、其他非I/O口

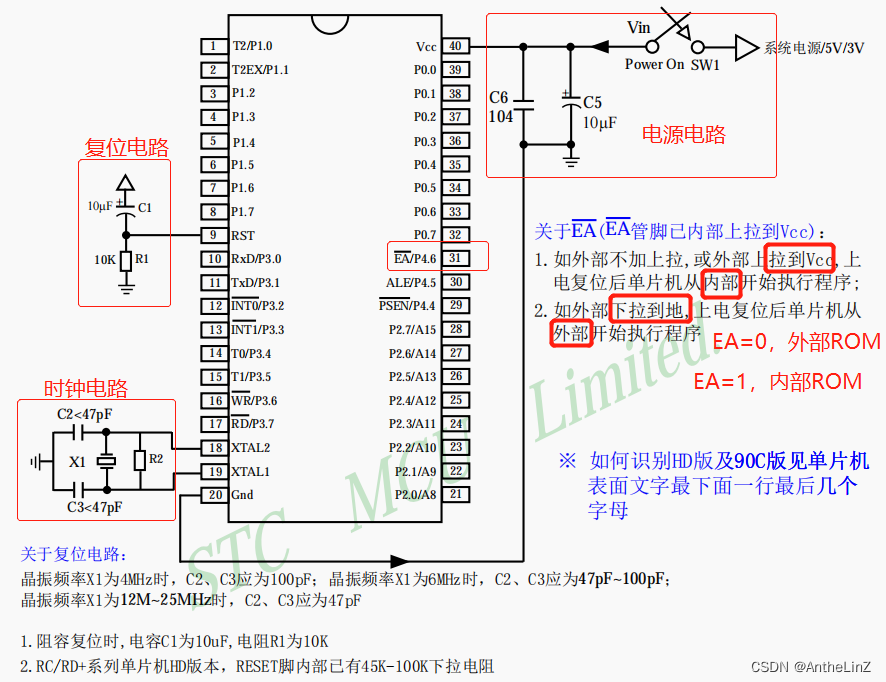

4、最小系统工作电路

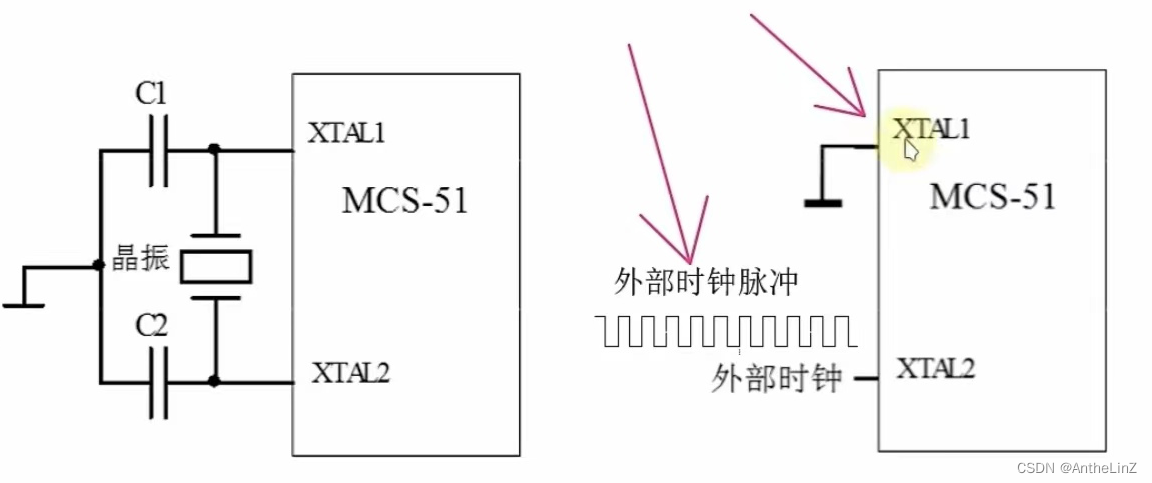

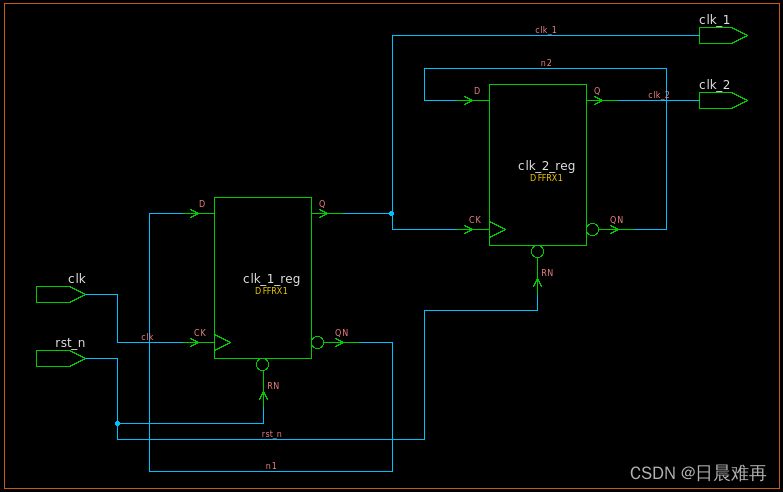

5、时钟电路——单片机的心脏

单片机需要时钟信号才能正常工作,时钟信号是脉冲信号的一种,周期固定,占宽比1:1的矩形脉冲波。时钟电路就是通过其他元器件综合来形成的时钟信号。 1.晶振时钟:通过外部晶振电路来获取时钟信号,电容用于起振。2.脉冲时钟:外部从XTAL2引脚输出时钟信号。

部分51单片机不需要外部晶振也能正常工作,优点是降低成本,缺点是RC振荡频率精度不高。

单片机的时序

是对象间按照时间顺序组成的序列关系,可以用状态方程、状态图、状态表和时序图表示。

时序与时钟的关系:时钟要受时钟节拍的制约。

时钟度量单位:时钟周期(节拍)P、状态周期S、机器周期、指令周期。

1S = 1P、1机器周期 = 6S = 12P、1指令周期 = 1~4机器周期

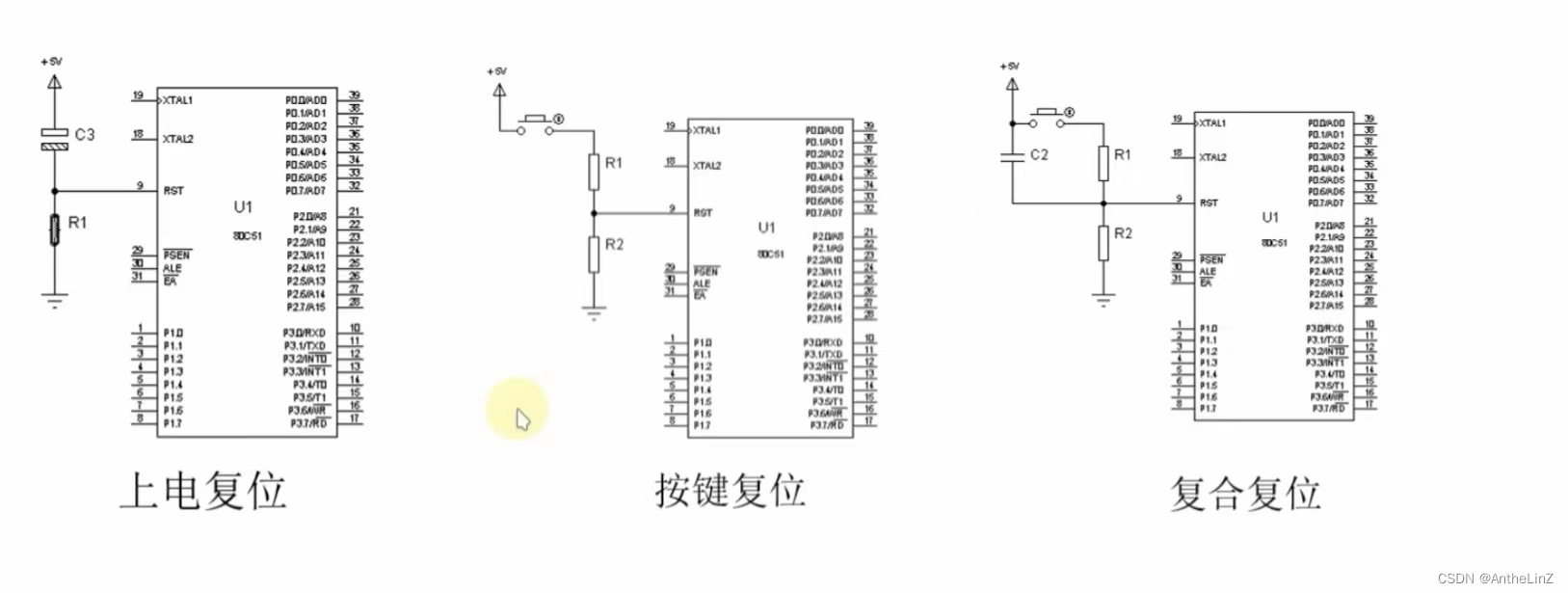

6、复位与复位电路

复位电路的首要功能是通电复位。使单片机恢复原始默认状态。P0-P3复位默认是全高电平。

复位条件:在RST/VPD引脚端出现:大于等于10ms时间的高电平3V状态。

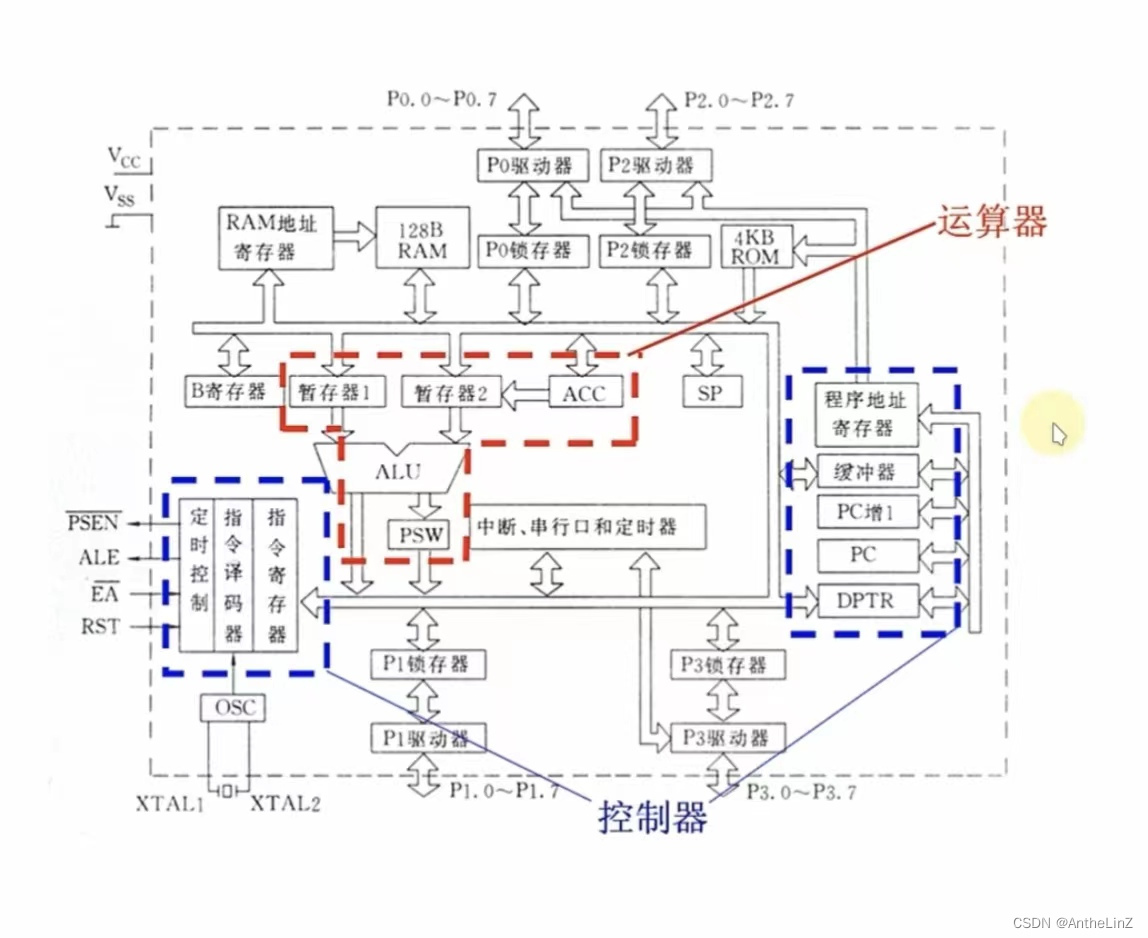

7、51内部结构

图中ROM为8k,RAM为512字节。

8、中央处理器

控制器

用途:统一指挥和控制各单元协调工作

任务:从ROM中取出指令——译码——执行指令

组成:程序计数器、指令寄存器、指令译码器、数据指针寄存器

程序计数器(Program Counter):指向下一条指令首地址,ROM存储单元的地址指针,可修改,让程序跳转运行复位时:PC=0——复位后程序从0开始运行。

指令寄存器(Instruction Register):8位寄存器,暂存指令,等待译码。

指令译码器(Instruction Decoder):将指令寄存器的指令进行译码,转为可执行的电信号,在通过定时器电路将其执行。

数据指针寄存器(Data Pointer):指向ROM或者RAM存储单元的地址指针(引导数据传送)DPTR是专门的16位的外设RAM或者外部ROM准备用于读取和写入的。

(16位寄存器的可寻址范围为2^16=64kb,可拆成两个8位独立寄存器DPL和DPH低8位和高8位)

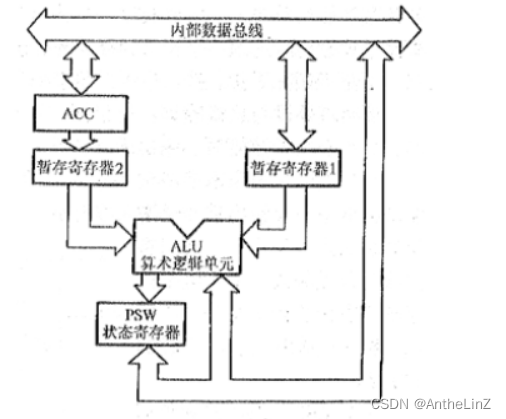

运算器

作用:对数据进行算术运算和逻辑运算。

功能:1.对暂存器中的数据进行运算。2.结果保存到ACC中。3.运行状态反映在PSW中

累加器ACC:一个8位寄存器,用来存放操作数或中间运行结果。状态值可由指令修改,是最繁忙的寄存器。

算术逻辑单元ALU:执行算术和逻辑运算,运算结果给PSW。

状态字寄存器PSW:8位寄存器,存放程序运行过程中的各种状态信息的寄存器。状态值可由指令修改

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)