记一下终于用iverilog搭建好仿真环境

动机一开始准备在linux系统里仿真的,看了非常多的教程,写的已经非常详细了,但是我这脑子还招架不住啊,最后转向在windows进行仿真,过程跟linux中其实是一样的,但是我电脑的linux系统始终找不到我的输入文件。下面记录一下(及其)详细的过程,也希望给各位刚开始接触的人有所帮助!iverilog软件下载下载入口(windows版本): http://bleyer.org/icarus/下载

动机

一开始准备在linux系统里仿真的,看了非常多的教程,写的已经非常详细了,但是我这脑子还招架不住啊,最后转向在windows进行仿真,过程跟linux中其实是一样的,但是我电脑的linux系统始终找不到我的输入文件。下面记录一下(及其)详细的过程,也希望给各位刚开始接触的人有所帮助!

iverilog软件下载

下载入口(windows版本): http://bleyer.org/icarus/

下载最新版本,即下图的第一个,里面已经包含了vvp、gtkwave的包,所以不需要额外下载。

安装完成后

安装完之后需要先配置环境变量: 右键单击桌面的计算机→属性→高级→环境变量 →双击编辑系统变量方框内的Path变量→右边新建以下两个(注意自己的路径设置),再确定就行。

配置好之后,即可开始上软件了!

iverilog是需要调用命令提示符来使用的,所以安装完成后打开桌面的快捷方式,不会出现一般软件的UI界面,而是会跳转到安装包。win+R调出面板输入cmd再回车,进入输入命令界面,然后一步一步输入命令实现仿真与gtkwave的调用,

准备环节

以下面代码为例

module time_delay_module(

input ai, bi,

output so_lose, so_get, so_normal);

assign #20 so_lose = ai & bi ;

assign #5 so_get = ai & bi ;

assign so_normal = ai & bi ;

endmodule相应的testbench

`timescale 1ns/1ns

module test ;

reg ai, bi ;

wire so_lose, so_get, so_normal ;

initial begin

ai = 0 ;

#25 ; ai = 1 ;

#35 ; ai = 0 ; //60ns

#40 ; ai = 1 ; //100ns

#10 ; ai = 0 ; //110ns

end

initial begin

bi = 1 ;

#70 ; bi = 0 ;

#20 ; bi = 1 ;

end

time_delay_module u_wire_delay(

.ai (ai),

.bi (bi),

.so_lose (so_lose),

.so_get (so_get),

.so_normal (so_normal));

initial begin

forever begin

#100;

//$display("---gyc---%d", $time);

if ($time >= 1000) begin

$finish ;

end

end

end

initial begin

$dumpfile("test.vcd");

$dumpvars(0, test);

end

endmodule需要注意的是,两个文件需放在一块!

运行方法

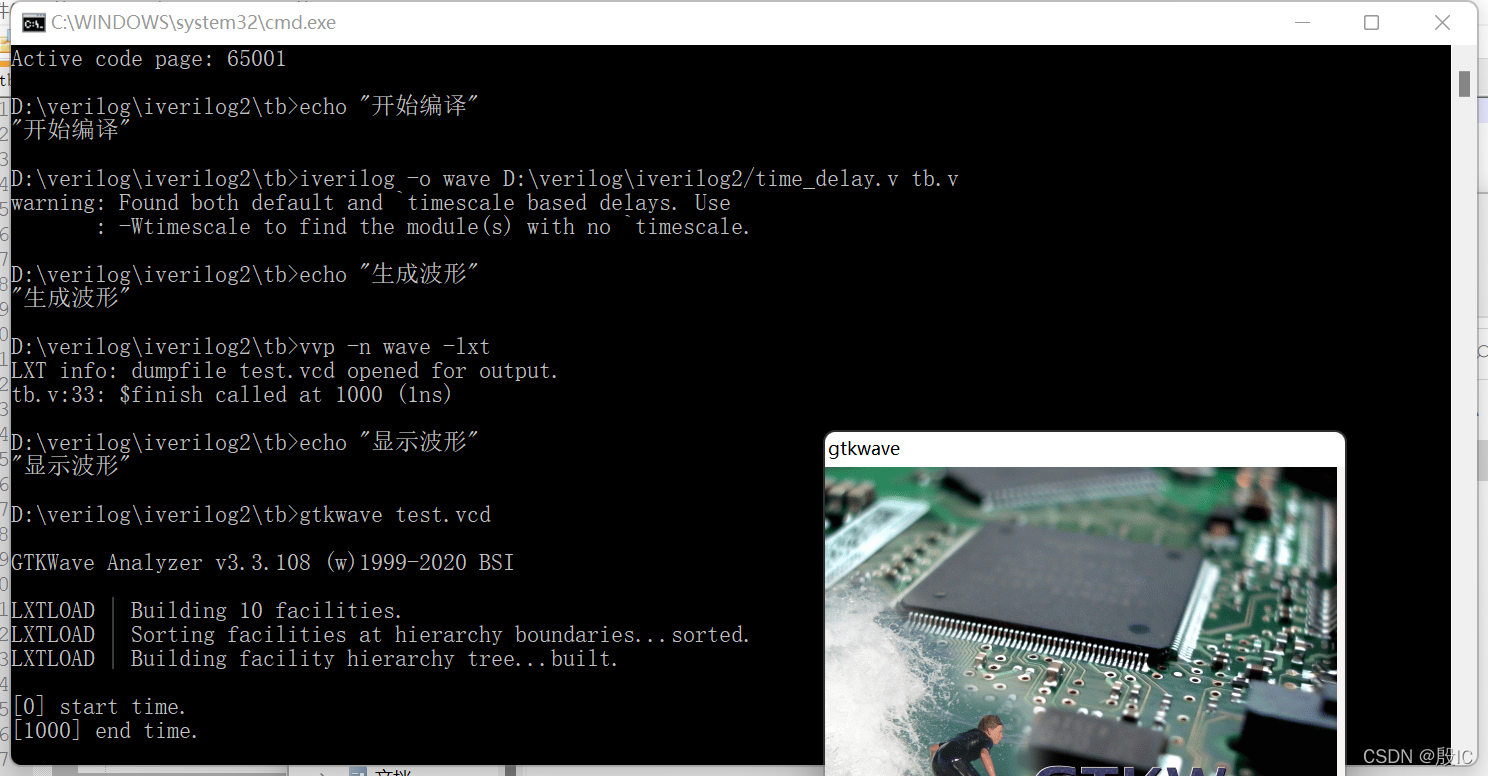

可以直接写个makefile一步到位,编辑一个.bat文件与tb放在一块(如上图),免得中间去不停输命令,本文只通过.bat运行仿真!

chcp 65001

echo "开始编译"

iverilog -o wave D:\verilog\iverilog2/time_delay.v tb.v

echo "生成波形"

vvp -n wave -lxt

echo "显示波形"

gtkwave test.vcd

pause步骤其实也是分三步,先编译产生输出文件(这里-o用来指定输出的文件名,wave即自定义的输出名,后面用的绝对路径),再通过中间软件vvp调用,最后调用gtkwave,这里test.vcd即代码块内定义的名字。

双击.bat文件,即开始仿真!!!!!

选择左边的端口,双击添加波形。

参考资料:

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)