简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

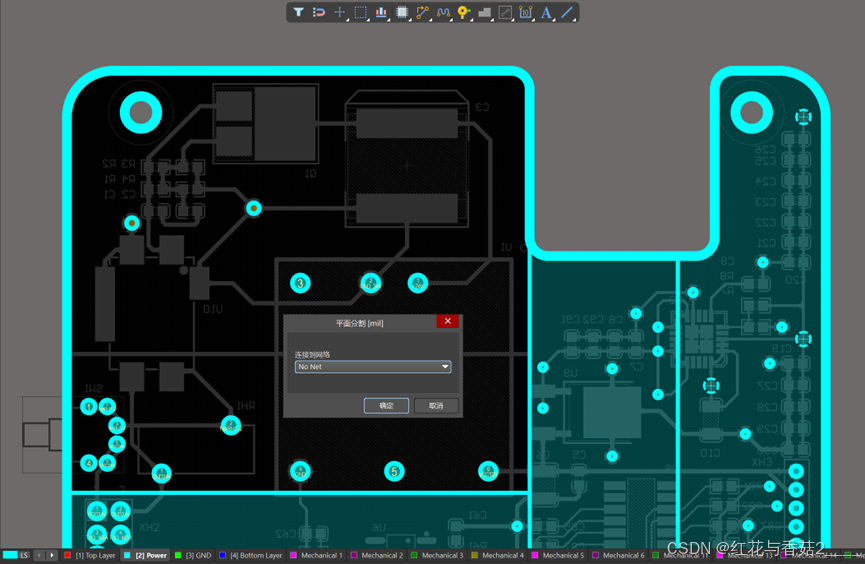

AD24在运行PCB设计规则检查(DRC)后报错:Un-Routed Net Constraint: Split Plane (No Net) on Power Dead Copper - Net Not Assigned.

在 Altium Designer(AD)的原理图库中,“Electrical Type”(电气类型)用于定义元件引脚的电气特性。如果想连接到 GND(地),在 “Electrical Type”(电气类型)中应该选择 “Power”(电源)。在原理图设计过程中,在元器件接线引脚位置出现红色波浪线,显示错误GND contains IO Pin and Power Pin objects。经查明,

内容来自小破站《黑马程序员-产品经理必备技能之数据分析》复习自用

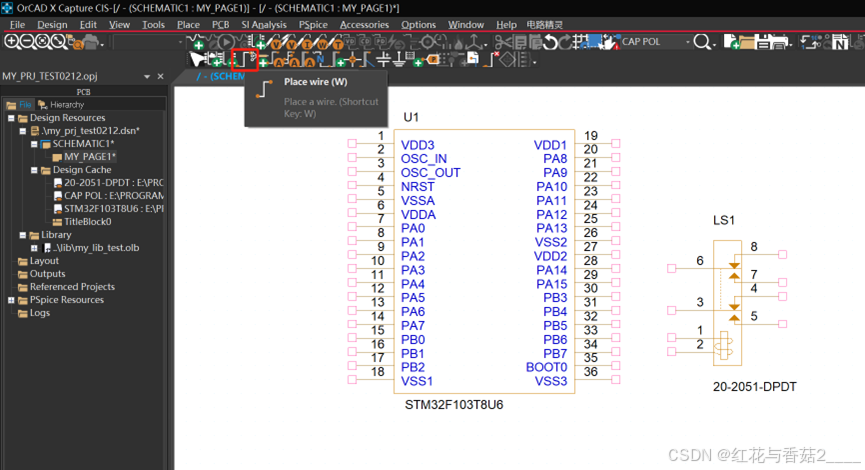

原理图是电路设计的核心,设计时需要遵循一定的规范,以确保图纸的可读性和可维护性。在使用Cadence创建原理图库及原理图时,有许多细节和注意事项需要关注,以确保设计的准确性、可维护性和高效性。

Pin 引脚设置正确在电子电路设计、制造及产品使用的全生命周期中都起着关键作用,确保信号准确传输,引脚类型决定信号流向:引脚类型如输入(Input)、输出(Output)、双向(Bidirectional)等有明确的信号传输规则。实现电路逻辑功能逻辑引脚设置影响逻辑运算。

OrCAD 的核心功能之一是原理图绘制,它提供了直观、易用的界面,方便工程师快速创建电路原理图。拥有丰富的元件库,涵盖了各种通用和专用的电子元件,还支持用户自定义元件,满足不同项目的特殊需求。

Cadence 提供了一套完整的电子设计自动化 (EDA) 工具链,涵盖了从芯片设计到系统设计的各个环节。其生态系统庞大而复杂,以下简要阐述其核心模块及其关系。

Cadence CIS (Component Information System)提供企业级元件库管理,支持与 ERP/PLM 系统集成,确保元件参数的标准化和实时更新。支持 Symbol/Footprint 自动校验,减少人为错误。具有庞大且专业的元件库,涵盖了各种半导体器件、无源元件等,并且支持用户自定义元件库,方便管理和复用。其元件符号的绘制和编辑功能强大,可灵活定制符合特定设计需求的元件

Cadence CIS (Component Information System)提供企业级元件库管理,支持与 ERP/PLM 系统集成,确保元件参数的标准化和实时更新。支持 Symbol/Footprint 自动校验,减少人为错误。具有庞大且专业的元件库,涵盖了各种半导体器件、无源元件等,并且支持用户自定义元件库,方便管理和复用。其元件符号的绘制和编辑功能强大,可灵活定制符合特定设计需求的元件

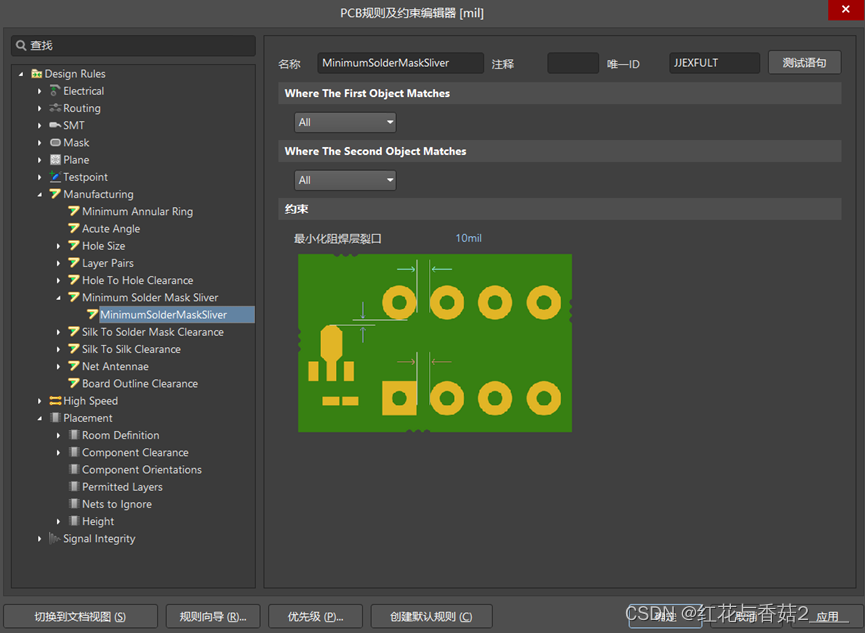

【AD23报错】Minimum Solder Mask Sliver (Gap=10mil) (All),(All),最小阻焊间隙约束,即PCB焊盘阻焊层之间间距小于10mil报错。