简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存或者高速异步数据的交互。这一块是由于仿真器设置导致的,在设置中语言选择的是Verilog和VHDL混合模式,所以会导致这个现象,但不建议直接改为Verilog语言模式,因为在一些IP核的底层是由Verilog和VHDL写好的,如果在这里改过来,虽然这一块波形是好的,但有可能在其他地方出现问题

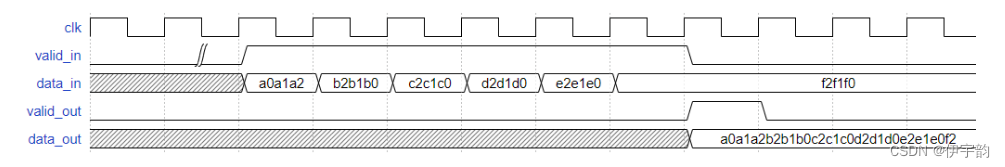

实现数据位宽转换电路,实现24bit数据输入转换为128bit数据输出。其中,先到的数据应置于输出的高bit位。电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号。接口示意图接口时序示意图。

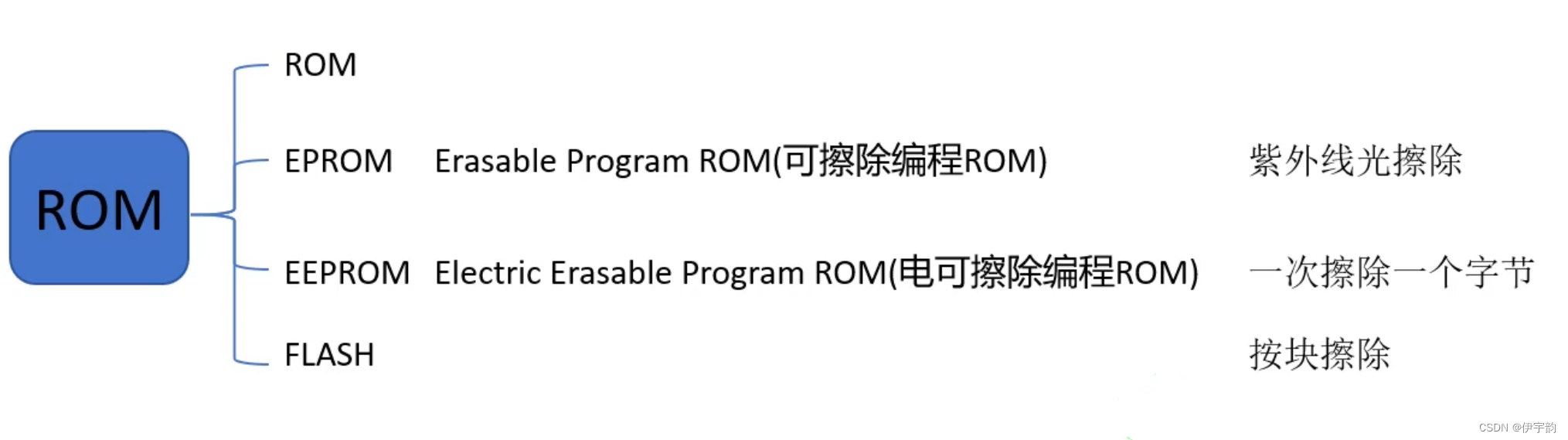

从Distributed Memory Generator 生成的ROM/RAM Core占用的资源是LUT (查找表,查找表本质就是一个小的RAM);从Block Memory Generator生成的ROM/RAMCore 占用的资源是 Block Memory (嵌入式的硬件RAM) ,某芯片,有500个寄存器,需要在上电的时候由FPGA向这些寄存器中写入初始值,初始值已经通过相应的文档给出

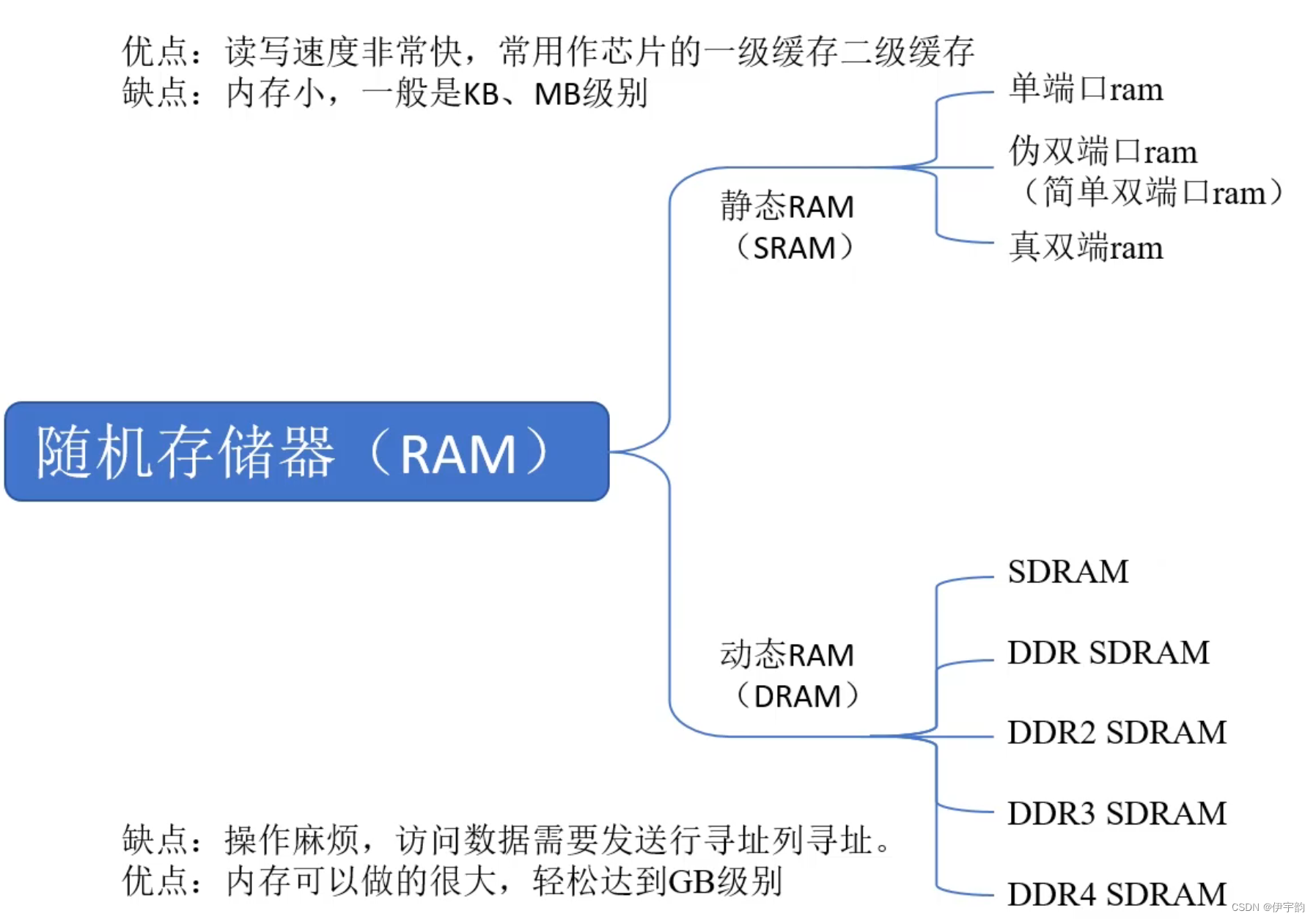

它可以随时把数据写入到任何一指定地址的存储单元。也可以随时从任一指定地址读出数据,其读写速度有时钟频率决定,主要用来存放程序以及程序执行过程中产生的数据,运算结果等。信号源(例如ADC)以1us一个的速率产生12位的数据现要求获得连续1ms内的数据,通过串口以115200的波特率发到电脑。数据量相对较大,数据要求能够重复使用,而且要求能够被更改。读出数据时波形(读使能到数据输出2个时钟周期)rom

2025年1月10日,DeepSeek发布名为R1的大语言模型