简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

电容在ESD测试整改中的选用。

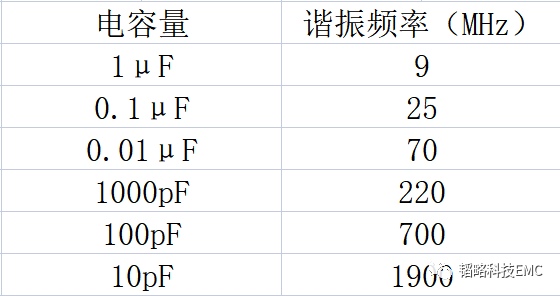

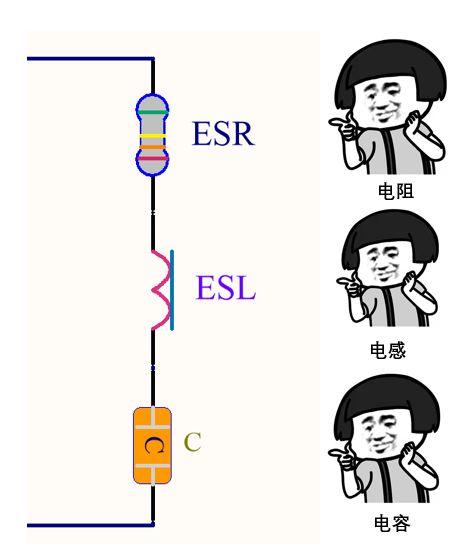

电路设计的每一个器件可以说是都不是没有根据的随便选型,只是可能到你手里之后,已经经过多方验证,是成型的原理图,参数不需要修改,所以关注的也少。等等,怎么我看到有些板子芯片的电源脚旁边的电容是0.1uF的或者0.01uF的,有什么讲究吗。可见当频率很低的时候是电容起作用, 而频率高到一定的时候电感的作用就不可忽视了,再高的时候电感就起主导作用了。所以记住,高频的时候电容就不是单纯的电容了。想必此时不

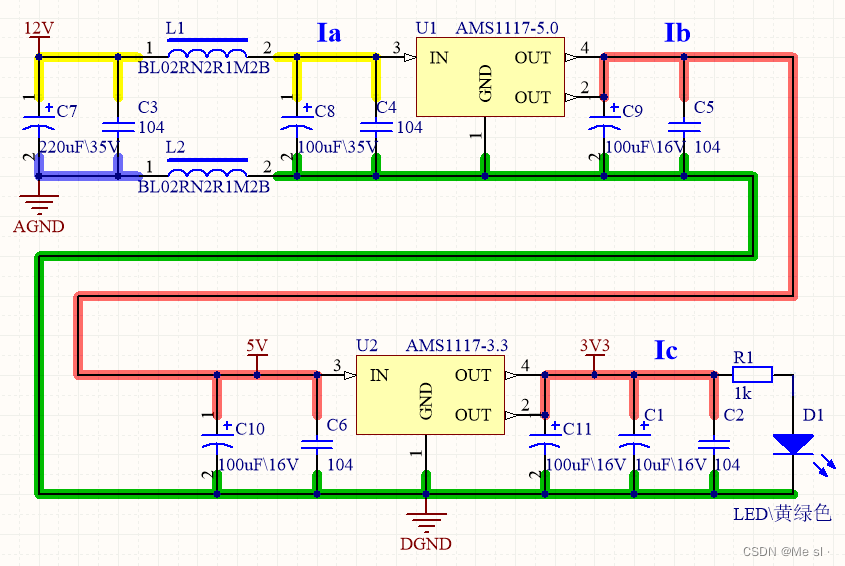

在图1里,Ia = Ib = Ic,芯片U1(AMS1117-5.0)输入输出电压相差12V - 5V = 7V,此时损耗功率至少 7V × 100mA = 0.7W,这就是U1烫手的原因。BUCK电路的开关电源特点:η × 输入功率 = 输出功率,η × 12V × Ix = 5V ×Iy。BUCK电路的开关电源特点:η × 输入功率 = 输出功率,η × 12V × Ix = 5V ×Iy。线

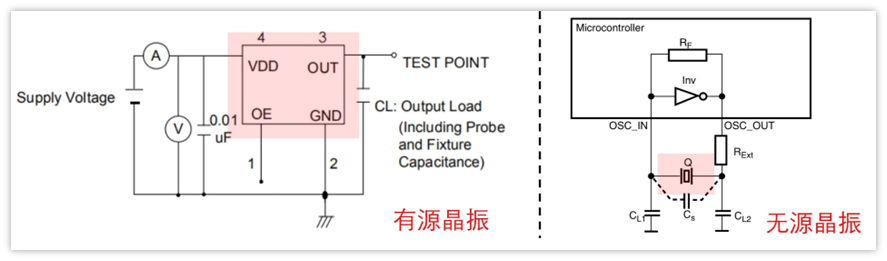

对于晶振电路,我们需要从几个方面考虑设计: 降低寄生电容的不确定性 降低温度的不确定性 减少对其他电路的干扰设计注意点:1. 晶振尽量靠近芯片,保证线路尽量短,防止线路过长导致串扰以及寄生电容。2. 晶振周围打地孔做包地处理。3. 晶振底部不要走信号线,尤其是其他高频时钟线。4. 负载电容的回流地要短。5. 走线时先经过电容再进入晶振。贴片无源晶振及有源晶振的走线方式:两脚贴片无源晶振6.封装较大

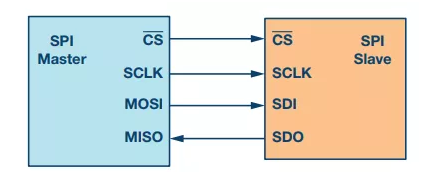

例如在图7所示的8位系统中,为使第3个从机能够获得数据,需要24个时钟脉冲,而常规SPI模式下只需8个时钟脉冲。此模式下的时钟相位为1,表示数据在下降沿采样(由橙色虚线显示),并且数据在时钟信号的上升沿移出(由蓝色虚线显示)。此模式下的时钟相位为1,表示数据在下降沿采样(由橙色虚线显示),并且数据在时钟信号的上升沿移出(由蓝色虚线显示)。当使用多个从机时,主机需要为每个从机提供单独的片选信号。此模

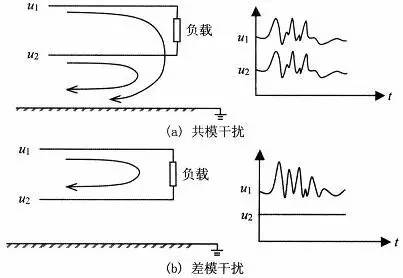

消除共模干扰(1)采用屏蔽双绞线并有效接地(2)布线时远离 高压线,更不能将高压电源线和信号线捆在一起走线(3)采用 线性稳压电源或高品质的 开关电源(纹波干扰小于50mV)(4)使用差分式电路(5)在信号线或电源线中串联共模扼流圈、在地与导线之间并联电容器、组成LC滤波器进行滤波,滤去共模传导噪声。消除差模干扰:(1)前提是减小共模干扰,不然共模干扰可能转化为差模干扰(2)采用差模扼流圈。...

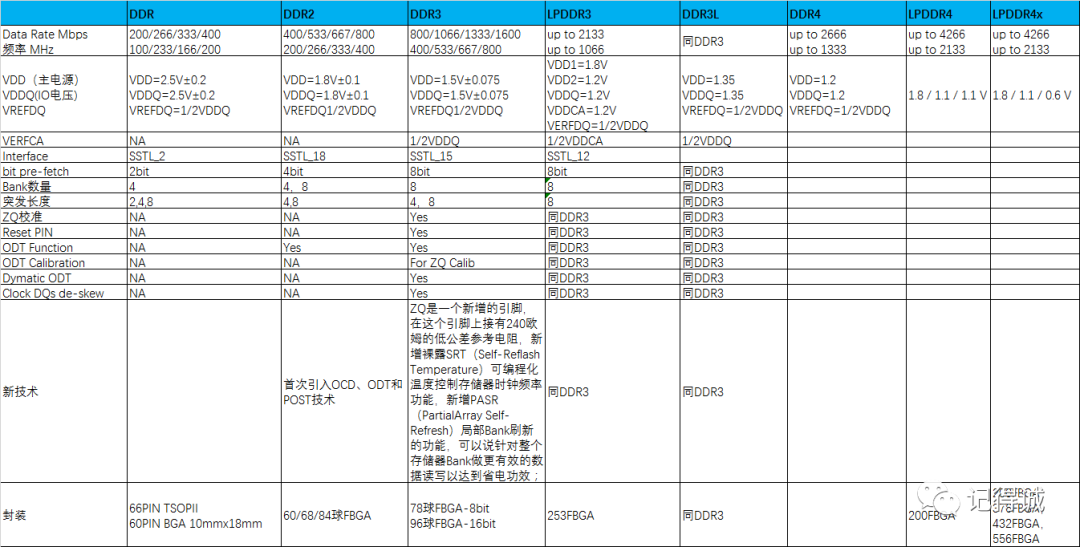

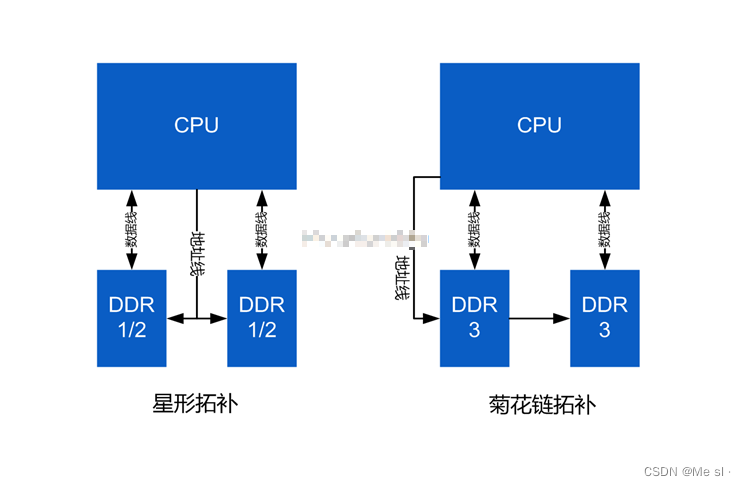

1、DDR系统的三种电源对于电源电压,DDR SDRAM系统要求三个电源,分别为VDDQ、VTT和VREF。A、主电源VDD和VDDQ主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给内核供电。但是一般的使用中都是把VDDQ和VDD合成一个电源使用。有的芯片还有专门的VDDL,是给DLL供电的,也和VDD使用同一电源即可。电源设计时,需要考虑电压、电流是否满足要求

但对于混合电路,包含高速数字电路与射频电路,射频电路比数字电路要重要的多,必须对射频信号做50欧姆阻抗控制,同时射频走线不可能太细,否则会引起较大的损耗,所以在混合电路中,本人往往舍弃数字电路的阻抗控制。Allegro中默认的线宽线距都是5mil,在CPU引脚比较密集的时候,这样的规则是无法满足的,这就需要在CPU或DDR芯片周围设定允许小间距,小线宽的区域规则,如下图。走完地址线和数据后,务必将

● 使用晶体时,环路的传递函数是怎样的?● 为什么只有晶振的固有频率能振荡起来?● 为什么改变匹配电容,就能改变频偏?● 为什么晶振电路有的要串电阻,有的没有?有的要并联1M电阻,有的没有?...

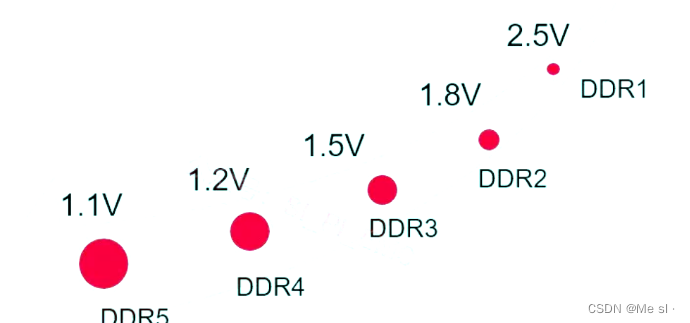

1 什么是DDRDDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。DDR的核心要义是在一个时钟周期内,上升沿和下降沿都做一次数据采样,这样400MHz的主频可以实现800Mbps的数据传输速率。2 每一代DDR的基本区别3 关键技术解释3.1 VTTVTT为