简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

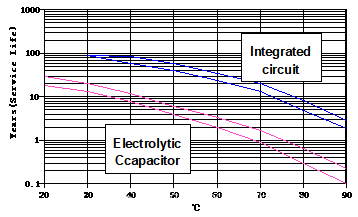

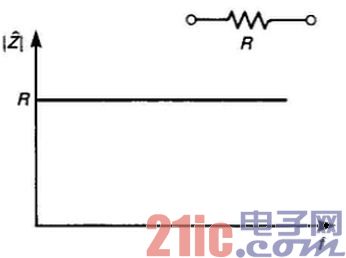

电阻不再是电阻——高频时确实如此许多设计师没有意识到实际元件中的寄生因素会影响它们的值。当频率达到几百兆赫兹时,诸如电阻、电感和电容等基本元件都会呈现出非理想的特性。这种变化在设计滤波器或试电阻不再是电阻——高频时确实如此许多设计师没有意识到实际元件中的寄生因素会影响它们的值。当频率达到几百兆赫兹时,诸如电阻、电感和电容等基本元件都会呈现出非理想的特性。这种变化在设计滤波器或试图优化供电网络、旁路

二、走线拓扑所有信号组,除了数据组外,全部用Fly by结构3、端接匹配端接电阻摆放在末端。时钟comp电容摆放在源端。4、等长原则注意:①.DQSP和DQSN要在同一层进行布线,DQSP/DQSN差分信号和它同一组的数据信号要在同一层进行布线②.差分时钟信号线要在在同一层进行布线5、参考平面地址线与控制线在条件允许情况下,建议以1V5电源为参考。实际设计时参考datasheet。6、

我们采集到的信号总不会是理想波形,例如,在采集交流信号的时候,可能会混入直流分量,而在采集直流信号的时候,也有可能混入交流分量,所以一个待测信号包含交流和直流两部分。耦合是指两个不同介质中通过物理连接时进行的能量传递。

任何物质都具有电阻,只是电阻的大小不同,阻碍电流的能力不同而已,绝缘体阻碍电流的能力最强,因此我们用绝缘体来隔绝导体,起到保护触电的作用,而超导体的电阻几乎为零。容性负载充放电时,电压不能突变,其对应的功率因数为负值,对应的感性负载的功率因数为正值。(1)、阻性负载指的是通过电阻类的元件进行工作的纯阻性负载。显然,感抗的大小不仅与自身因素(L)有关系,还与外部施加的交流电的角频率(ω)或频率(f)

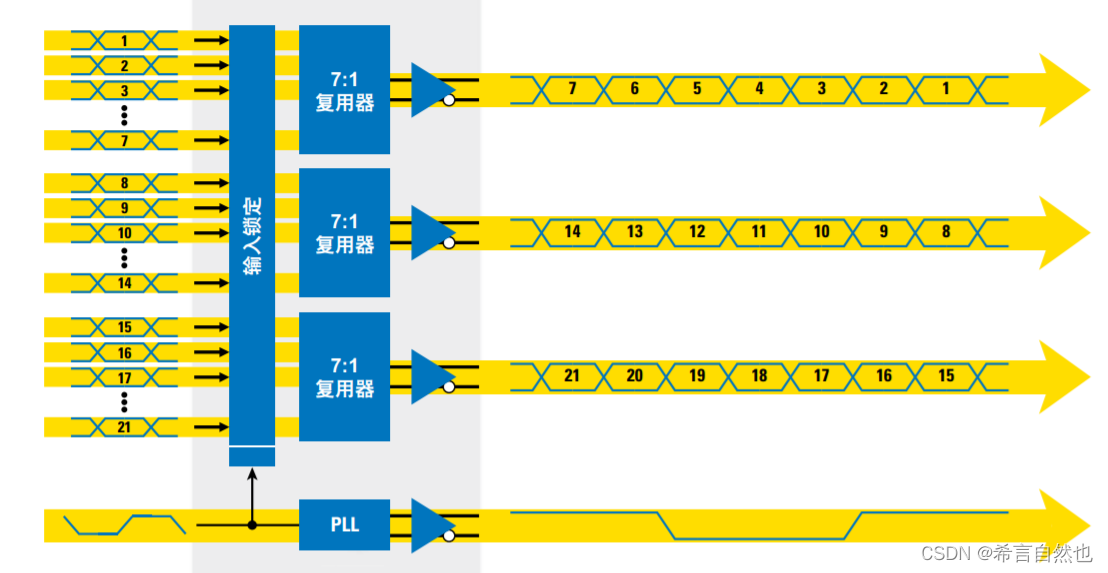

SerDes怎么可以没有传输时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?本篇从一个SerDes用户的角度来理解SerDes技术。

常用信号线宽与过孔为以下内容:1)8/8mil,过孔选择12mil(0.3mm)。2)6/6mil,过孔选择12mil(0.3mm)。3)4/4mil,过孔选择8mil(0.2mm)。4)3.5/3.5mil,过孔选择8mil(0.2mm)。5)3.5/3.5mil,过孔选择4mil(0.1mm,激光打孔)。6)2/2mil,过孔选择4mil(0.1mm,激光打孔)。参考过孔:内径12mil、外径

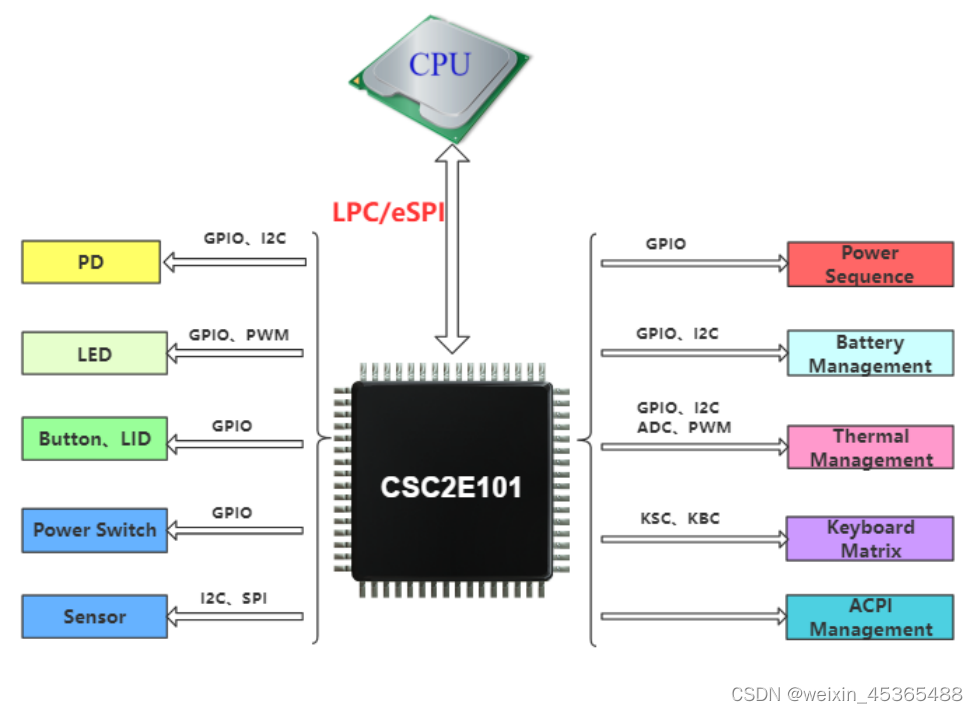

LPC总线,原名叫即精简引脚总线,由Intel在1998年引入PC产品,相较于ISA总线,LPC 引脚少,速度快。BIOS串口并口PS/2的键盘和鼠标软盘控制器,比较新的设备有可信平台模块。LPC总线通常和主板上的南桥物理相连,南桥在IBM PC AT平台上通常连接了一系列的“老旧”设备, LPC总线最大的优点是只需要7个信号,在拥挤的现代主板上是很容易布局的随着超大规模集成电路的不断发展,芯片的

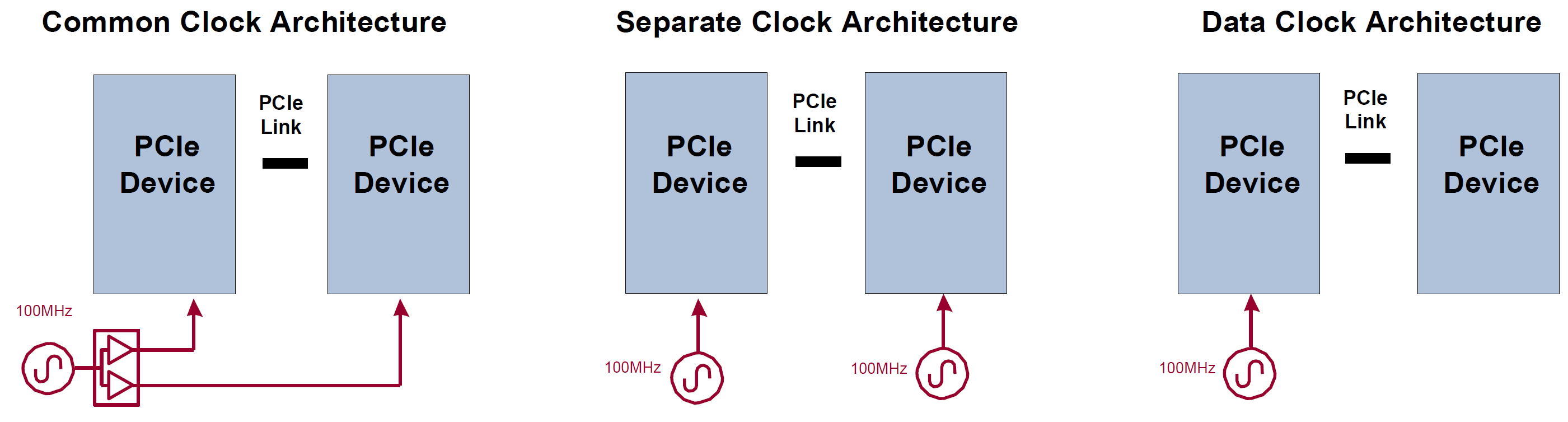

首先先看下PCIE架构组件:下图中主要包括了CPU(ROOT COMPLEX),PCIE SWITCH,BUFFER以及一些PCIE ENDPOINT;而且可知各个器件的时钟来源都是由100MHz经过Buffer后提供。接着上图的架构,我们来简单看下PCIE时钟的三种架构:Common Clock Architecture:所有设备的参考时钟分布必须匹配到15英寸以内在系统板上。在接收端数据和时钟

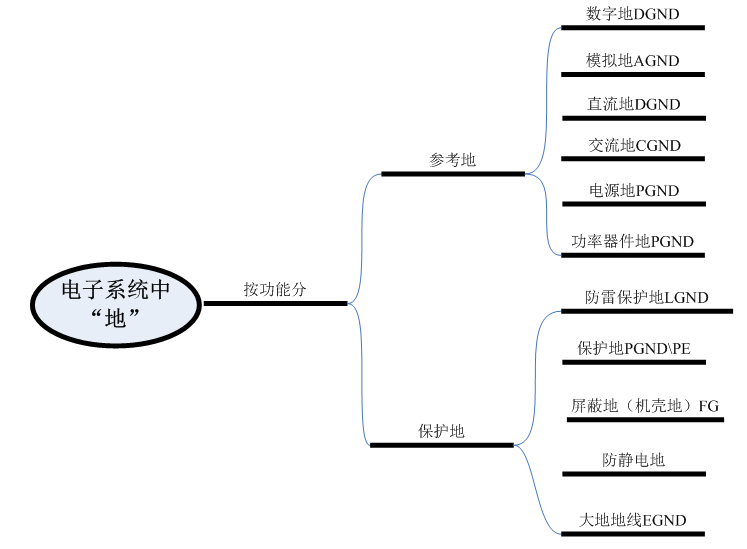

“地”是电子技术中一个很重要的概念。由于“地”的分类与作用有多种, 容易混淆,故总结一下“地”的概念。“接地”有设备内部的信号接地和设备接大地,两者概念不同,目的也不同。“地”的经典定义是“作为电路或系统基准的等电位点或平面”。做硬件设计时,我们经常会接触到诸如“模拟地”、“数字地”、”参考地”、”电源地”、“保护地”、“大地”、“浮地”等各种“地”,这些地有什么区别,又有什么联系,下面我们一起来