简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

文章目录深度学习中的Tensor 数据格式(N,C,H,W)一、深度学习框架中的图像格式2、数据格式3、物理存储3.1、NCHW3.2、NHWC3.3、CHWN:StridesBlocked layout4、RGB图像数据举例5、不同框架的支持深度学习中的Tensor 数据格式(N,C,H,W)参考:数据格式- 图解NCHW与NHWC数据格式NCHW-NHWC-NC/32HW32一、深度学习框架中

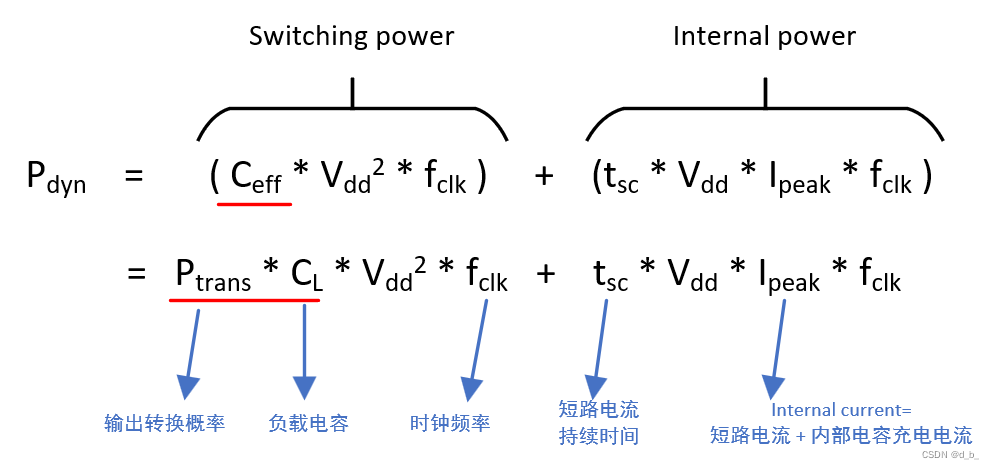

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析。由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具;更精确的功耗分析可以采用PT,关于PT的功耗分析可以查阅其他资料,这里不涉及使用PT的进行功耗分析。 (1)功耗分析与流程概述 上一个小节中讲解了功耗的构成,并且结合工艺库进行简要地介绍了功耗的计算。但是实际上,我们根本不可能人

版权声明:本文为CSDN博主「奇小葩」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/u012489236/article/details/107750942学习完了DDR的基本组成和硬件结构

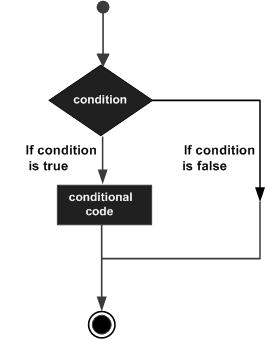

文章目录1、Tcl基本语法2、Tcl命令结构:命令替换变量替换反斜杠替换(转义替换)3、Tcl数据类型简单Tcl对象字符串表示列表 List关联数组句柄4、tcl变量变量命名动态类型数学表达式5、Tcl运算符算数运算符关系运算符逻辑运算符位运算符三元运算符运算符优先级6、Tcl决策?:操作符if语句 / if ... else 语句switch 语句内嵌switch语句7、Tcl 循环while

版权声明:本文为CSDN博主「yuzhong_沐阳」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/zhong_ethan/article/details/104759746文章目录0. 功耗源1. 动态功耗1.1 翻转功耗1.2 短路功耗2. 静态功耗2.1 亚阈值泄漏电流2.2 栅泄漏电流2.3 结泄漏电流

文章目录sdc:基本的时序路径约束1、概念时序路径关键路径路径约束1、路径2(寄存器到寄存器的路径)约束2、路径1(输入到寄存器D端)的约束3、路径3(寄存器到输出端口)的约束4、路径4(输入到输出)的约束**(1)路径4:输入到输出****(2) 纯组合逻辑,内部没有时钟**2、实战设计(约束)规格书:.synopsys_dc.setup文件,设置DC启动环境common_setup.tcldc

版权声明:本文为CSDN博主「奇小葩」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/u012489236/article/details/107730731内存是我们平常嵌入式系统中接触的比

文章目录深度学习中的Tensor 数据格式(N,C,H,W)一、深度学习框架中的图像格式2、数据格式3、物理存储3.1、NCHW3.2、NHWC3.3、CHWN:StridesBlocked layout4、RGB图像数据举例5、不同框架的支持深度学习中的Tensor 数据格式(N,C,H,W)参考:数据格式- 图解NCHW与NHWC数据格式NCHW-NHWC-NC/32HW32一、深度学习框架中

文章目录Abtract1、generate语法2、generate常用的几种情况举例说明1). generate-for循环语句2).generate-conditional条件语句3).generate-case分支语句3、Conclusion4、generate-for 与 常规for 循环不同1)使用举例2)结论参考链接:https://www.cnblogs.com/nanoty/arch

文章目录深度学习中的Tensor 数据格式(N,C,H,W)一、深度学习框架中的图像格式2、数据格式3、物理存储3.1、NCHW3.2、NHWC3.3、CHWN:StridesBlocked layout4、RGB图像数据举例5、不同框架的支持深度学习中的Tensor 数据格式(N,C,H,W)参考:数据格式- 图解NCHW与NHWC数据格式NCHW-NHWC-NC/32HW32一、深度学习框架中