简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

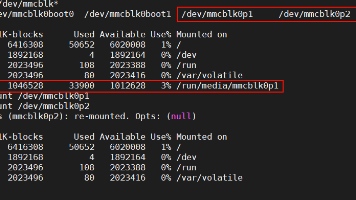

本文介绍了在Ubuntu系统下对SD卡进行分区操作的方法,用于Petalinux开发流程。主要内容包括:通过fdisk工具删除原有分区并创建两个新分区(FAT32格式的启动分区和ext4格式的Linux分区),格式化分区后挂载使用。最后将Petalinux生成的文件分别拷贝到对应分区,实现ZYNQ板卡的SD卡启动。操作涉及终端命令、分区类型选择和格式化等关键步骤。

本文介绍了ZYNQ通过eMMC启动的步骤。由于eMMC是焊接在板卡上的存储芯片,需要先通过SD卡启动Linux系统,在系统内对eMMC进行分区和文件拷贝操作。

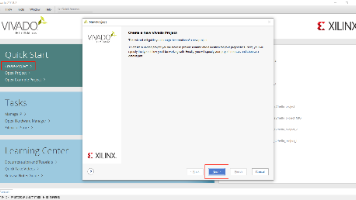

摘要:本文介绍了使用Vivado软件进行FPGA开发的基本流程:1)创建工程并选择FPGA型号;2)添加设计文件、约束文件和仿真文件;3)编写代码后依次执行综合、实现和生成比特流文件;4)连接FPGA板卡并烧录生成的比特流文件。开发过程中需要注意FPGA型号支持包的安装,以及调试信号(ILA核)会生成.ltx调试文件。整个流程涵盖了从工程创建到最终烧录的关键步骤。

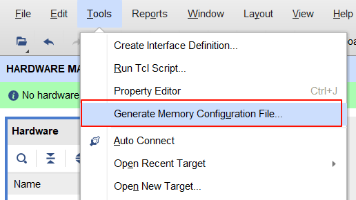

本文介绍了FPGA开发中如何将Bitstream文件转换为MCS文件并烧录到Flash存储器中,实现断电后程序不丢失。主要内容包括:1)在Vivado工具中通过Generate Memory Configuration File"选项生成MCS文件;2)详细说明了MCS文件的配置参数,包括格式选择、Flash型号指定、接口类型等;3)描述了将MCS文件烧录到Flash存储器的具体步骤;4

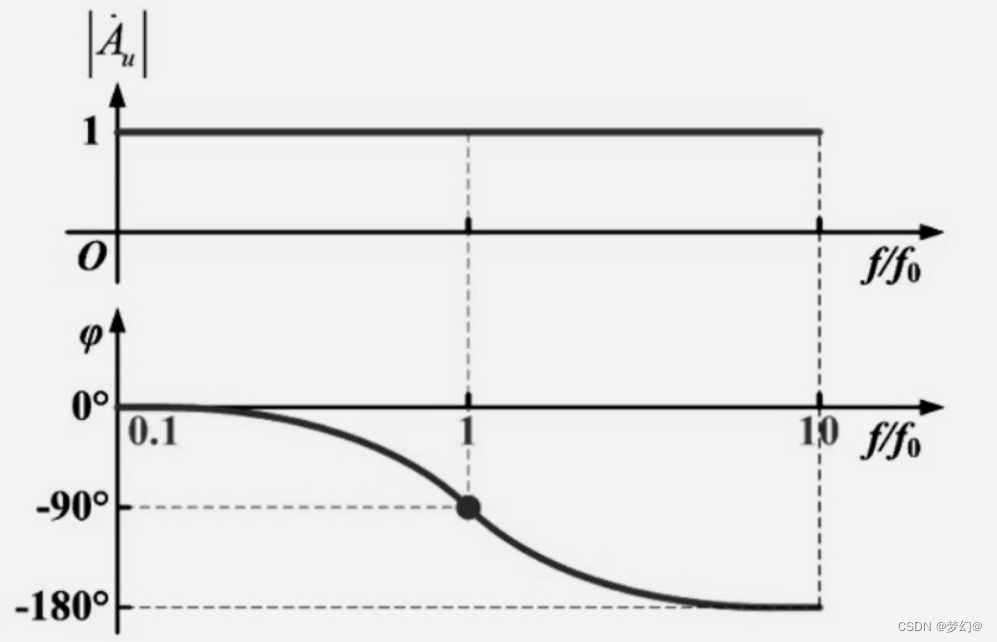

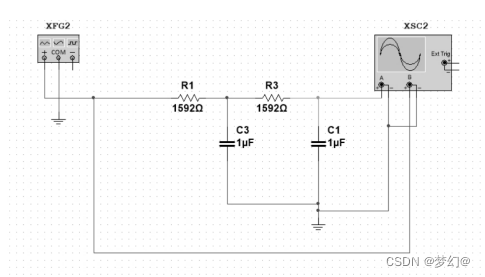

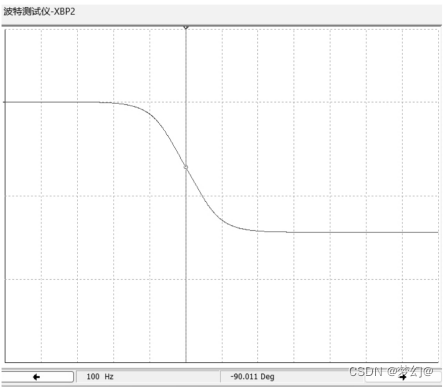

由上图可知,当频率为截止频率100Hz时, 二阶RC滤波器的每一个RC低通电路相移-45°,两个RC低通电路总共相移-90°。RC低通滤波电路由于电阻电容的充放电作用,存在时延,即出现相位偏移,一阶RC低通滤波器随着输入电压频率的增大,输出电压相位会超前于输入电压的相位,最大相位偏移为-90°,一旦相位偏差达到90°,输入电压频率继续增大,输出电压相位将一直保持超前于输入电压90°不变。从图中可看

一阶滞后全通滤波器如图所示,与一阶超前全通滤波器类似,输入为Ui,输出为Uo,电阻R1 = R2 = R3 = R =1k,电容C1 = C = 100nF,求其传递函数,进行如下计算。一阶超前全通滤波器如图所示,输入为Ui,输出为Uo,电阻R1 = R2 = R3 = R =1k,电容C1 = C = 100nF,求其传递函数,进行如下计算。全通滤波器对于频率从0到无穷大的信号具有相同的比例系数