简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

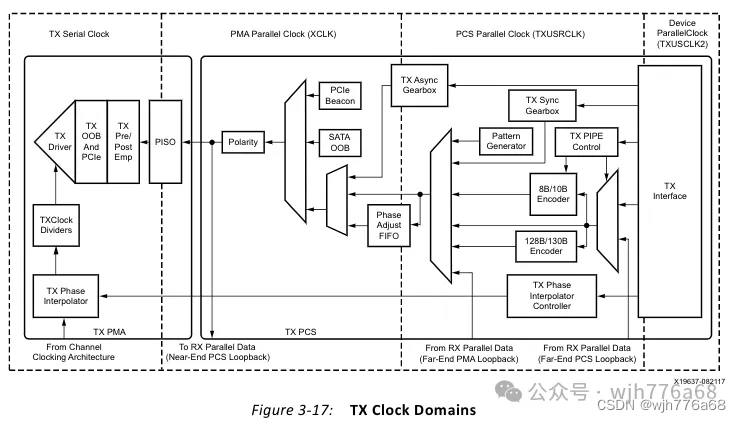

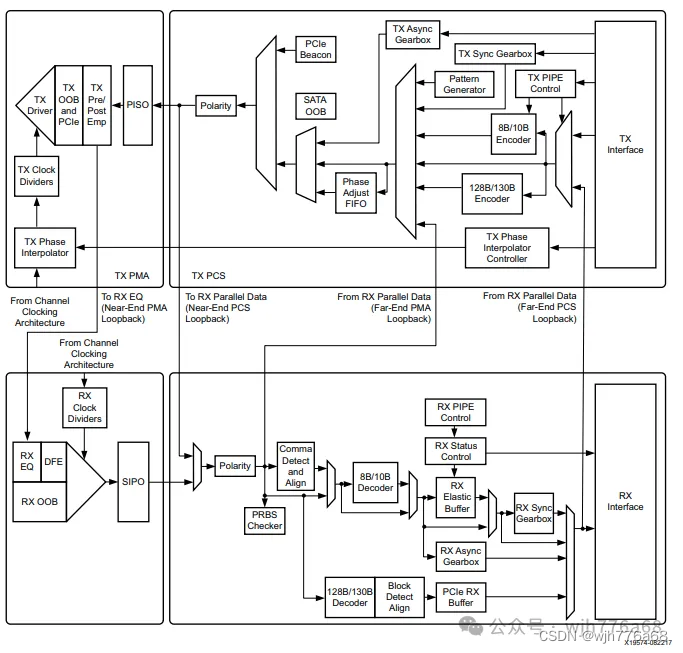

一般情况下,GT的TX和RX中都会存在Buffer用于进行XCLK与TXUSRCLK/RXUSRCLK间的时钟域转换。Buffer的存在会带来较长的逻辑级数进而带来额外的数据路径,进而影响延迟。为此,GT支持选择Buffer Bypass模式,通过相位调整电路和延迟调整电路代替Buffer进行时钟域的转换,如下图所示。GT手册中对于Buffer Bypass的介绍十分详细,在实际使用时,GTY I

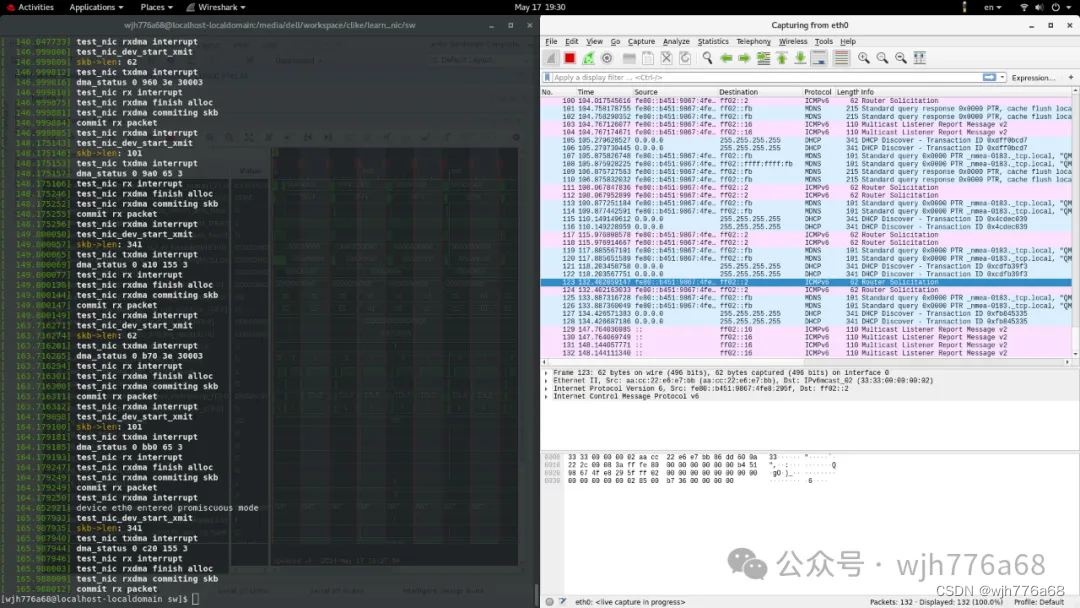

本系列介绍如何利用FPGA实现一个基本的千兆网卡。本文介绍除以太网子系统(Ethernet Subsystem)外其他部分功能设计。FPGA使用Xilinx Ultrascale+ VCU128开发板,操作系统使用RHEL8.8(RedHat)。

本文在前文代码的基础上进行拓展,通过引入40G以太网子系统,简单实现40G万兆网卡。FPGA使用Xilinx Ultrascale+ VCU128开发板,操作系统使用Ubuntu20.04,使用到的驱动代码与RHEL8.8(RedHat)兼容。

Xilinx官方提供了对pl复位的函数,该函数位于[platformproject]/zynqmp_fsbl/psu_init.cunsignedlongpsu_ps_pl_reset_config_data(void),下面函数为对官方函数的简化,在PS端执行pl_resetn()函数即可控制MPSOCIP核的pl_resetn引脚(引脚位置见下图)对PL端进行复位。......

合工大机器人四次作业代码(包括ID3算法)要的话2977295009 两个A+

本文基于Xilinx Ultrascale+HBM VCU128开发板与linux(RHEL8.9),介绍MSIX中断方式的代码实现。本文分为MSIX中断简述、FPGA逻辑设计、驱动程序设计、上板测试四个部分。

本文基于前文配置的8B/10B编码GTY IP核进行数据收发模块编写及仿真测试,并基于Xilinx Ultrascale+HBM VCU128开发板进行上板验证。

本文介绍了Ultrascale+系列GTY高速收发器的基本构成,以及进行8B/10B传输所需的GTY IP核配置,下文将利用本文配置的IP核进行数据收发。

64B/66B仍采用突发数据传输的方式传输数据,一个完整的数据传输过程包含S(起始位)、D(数据位)、T(停止位)三种类型的字符,在空闲时刻,可以发送C / Z(控制类字符)。不同于8B/10B的是,64B/66B会对一个完整的数据流进行分割,变成几个64bit的蓝色小段。几个蓝色小段的格式需要满足如下表格中的某一模式,64B/66B会对这些64bit的小段编码成66bit(加上2bit Sync

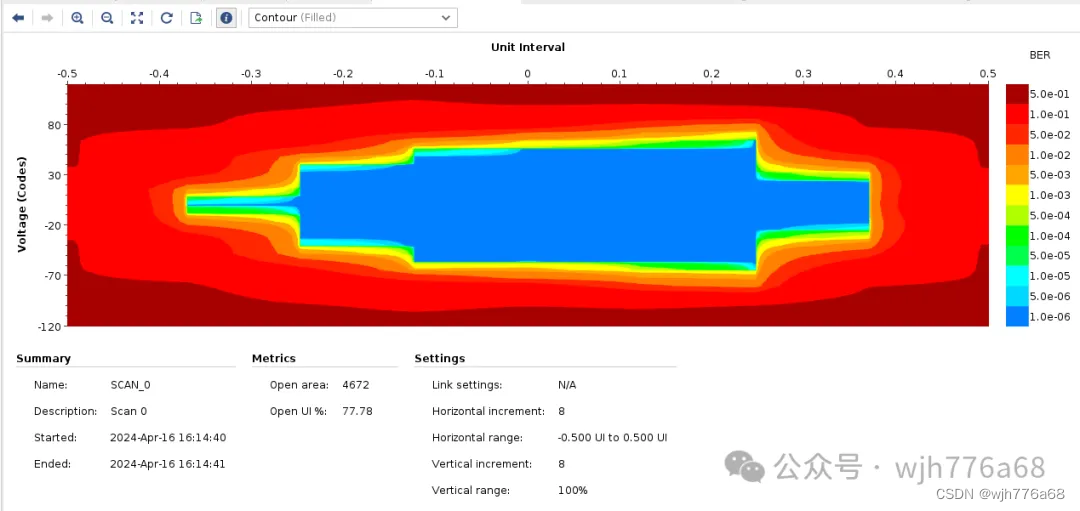

本文介绍使用In System IBERT IP核构建ibert眼图测试,以及通过设置参数以优化信号传输质量的方法。