简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

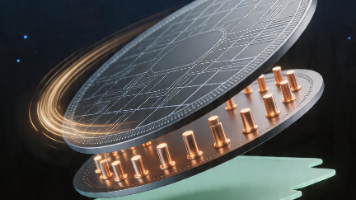

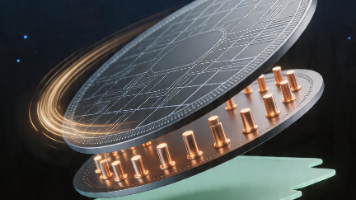

导语: 当你的手机在几秒内完成一次AI图像识别,当数据中心的海量算力支撑起万亿参数的大模型,这些看似平常的体验背后,都离不开一项诞生于60多年前的封装技术——倒装芯片(Flip Chip)。在AI、5G、自动驾驶等新兴应用的驱动下,倒装芯片正与2.5D/3D封装、Chiplet、异构集成等前沿技术深度融合,持续推动着电子设备向更高性能、更小尺寸、更低功耗的方向迈进。倒装芯片技术的核心理念,是将芯片

导语: 当你的手机在几秒内完成一次AI图像识别,当数据中心的海量算力支撑起万亿参数的大模型,这些看似平常的体验背后,都离不开一项诞生于60多年前的封装技术——倒装芯片(Flip Chip)。在AI、5G、自动驾驶等新兴应用的驱动下,倒装芯片正与2.5D/3D封装、Chiplet、异构集成等前沿技术深度融合,持续推动着电子设备向更高性能、更小尺寸、更低功耗的方向迈进。倒装芯片技术的核心理念,是将芯片

毕竟,在芯片行业,质量管理的终极目标不是通过测试验证,而是让测试验证变得多余。芯片项目具有典型的"一次性"特征:一旦进入流片阶段,90%的质量成本已被锁定。文档中明确指出"至少85%的质量成本由管理层负责",这意味着早期阶段的缺陷预防比后期检测重要百倍。面对动辄数百人年的研发投入,芯片项目的质量管理不仅是技术问题,更是一场关乎企业生存的战役。这要求质量管理者既要掌握传统的STA(静态时序分析)、U

在摩尔定律放缓的今天,Partition不仅是一种工程技巧,更是连接"More Moore"与"More than Moore"的桥梁,是延续半导体产业创新的关键基石。Partition设计:切成6-10个约20mm²的模块后,单块仅需30-40GB内存,8-10小时即可完成迭代,实现"日收敛"(Daily Turnaround)无论是正在攻坚5nm以下先进工艺的后端工程师,还是规划下一代AI芯片

理解Skew、Latency、Uncertainty和Jitter这些核心概念及其相互关系,掌握时钟树综合的优化方法,对于实现高性能、低功耗的芯片设计至关重要。本文将深入解析时钟网络中的四大关键参数:Skew、Latency、Uncertainty和Jitter,并探讨它们对时钟树综合和时序收敛的影响。时钟偏差(Clock Skew)是指同一个时钟信号到达不同寄存器时钟端口的相对时间差异,数学表达

导语: 从手机CPU到AI服务器,从汽车电子到航空航天,BGA(Ball Grid Array,球栅阵列)封装几乎无处不在。BGA封装从诞生至今30余年,凭借其高密度、高性能、高可靠性的特点,已成为现代电子产业不可或缺的基石。理解BGA的特性、类型差异和应用要点,结合产品定义、供应链、成本、制造能力等多维度考量,才能做出最优决策,避免"调试生产拍大腿"的尴尬。1990年代初,Motorola与Ci

导语: 从手机CPU到AI服务器,从汽车电子到航空航天,BGA(Ball Grid Array,球栅阵列)封装几乎无处不在。BGA封装从诞生至今30余年,凭借其高密度、高性能、高可靠性的特点,已成为现代电子产业不可或缺的基石。理解BGA的特性、类型差异和应用要点,结合产品定义、供应链、成本、制造能力等多维度考量,才能做出最优决策,避免"调试生产拍大腿"的尴尬。1990年代初,Motorola与Ci

Design for Reliability》不仅是一本技术手册,更是一份工程师的伦理指南——它教会我们如何在设计阶段就"做正确的事",而不是事后"正确地做事"。导语:当特斯拉因为软件故障召回数十万辆车,当波音737 MAX的MCAS系统缺陷酿成空难,当某品牌手机因为电池设计问题在全球"炸机"——这些代价数十亿美元的事故,根源往往不在制造,而在设计。今天推荐的这本书,正是解决这些问题的工程圣经。本

随着芯片工艺进入深亚微米时代(如110nm以下),芯片的工作频率飙升至GHz级别,但传统的“静态测试”就像用慢动作检查高速赛车,难以发现因信号延迟引发的缺陷。未来,随着3D封装和AI芯片的普及,OCC将继续演进,成为芯片设计中不可或缺的“隐形守护者”。类比解释:OCC就像智能红绿灯,在“测试道路”上灵活切换低速ATE时钟(交通疏导)和高速内部时钟(赛车冲刺),确保测试效率与准确性。错误案例:若OC

在AXI总线中,它指的是主设备(Master)能够在从设备(Slave)未返回响应的情况下,连续发送多个请求的能力。如果从设备的Outstanding能力为1,那么主设备必须等待第一个请求的响应返回后,才能发送下一个请求。过小的Outstanding会导致性能不佳,过大的Outstanding则会增加硬件开销和系统复杂度,甚至可能导致总线拥塞。但当从设备的Outstanding能力为N(N>1)时