简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

Zynq芯片的电源分为PS系统和PL逻辑(FPGA)两部分,这两部分的电源区域是完全独立的、被隔离以防止损坏;由于VCCINT_1V0电源电流很大,在靠近电源芯片侧,需要放置2个680uF或4个330uF的电容(由于低气压要求,不能使用钽电容),用于储能;保证100uF、4.7uF、0.47uF电容至少各1个,其余每个电源管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。每个Bank

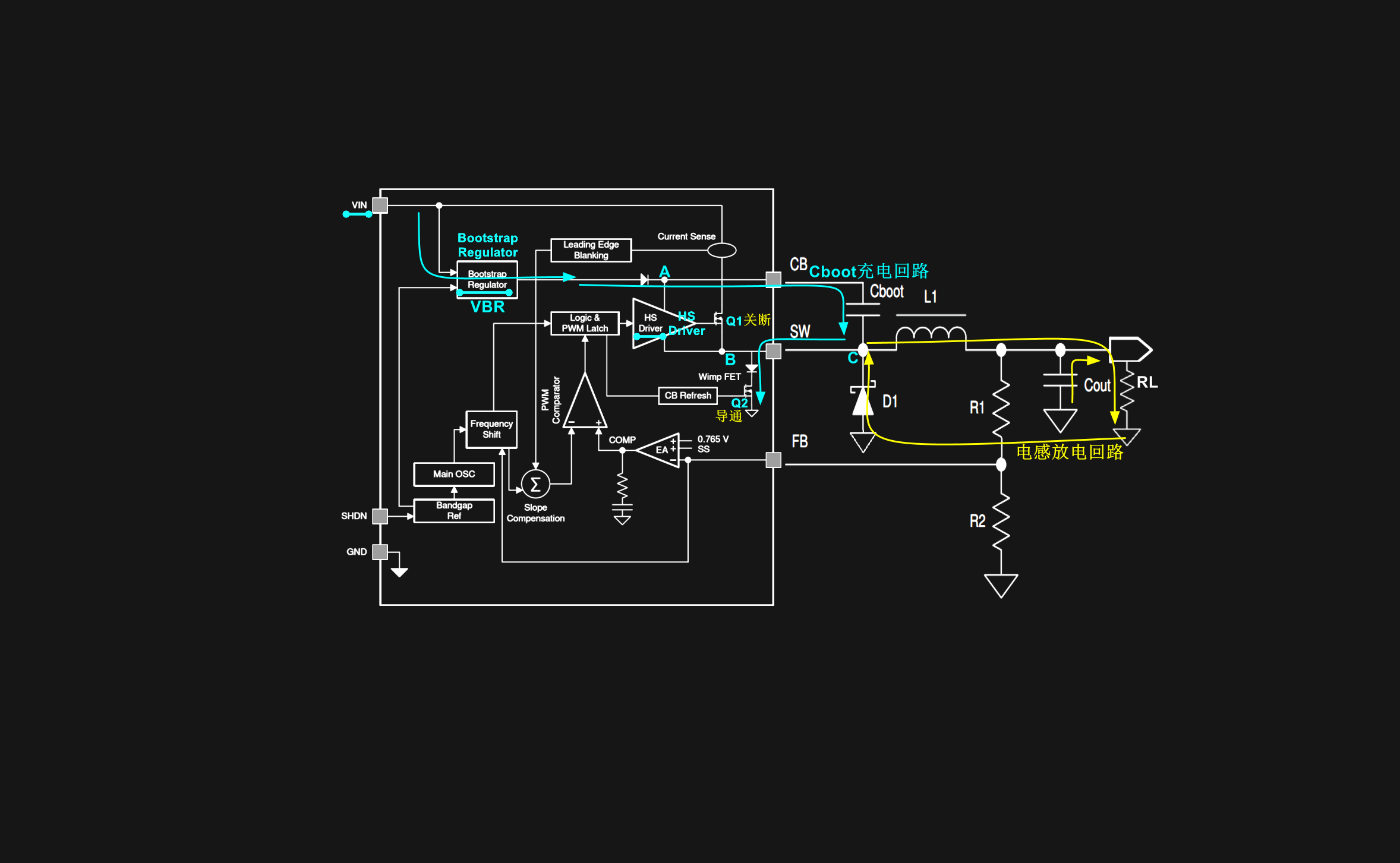

三炮儿每周二早七点 分享/更新一篇硬件开发学习笔记 学习分享以助能力增长♥经验交流以期跻身一流 目录 一、自举电容的作用 二、自举电容的工作原理/过程 三、自举电容选型 ✍ 本周的笔记是关于BUCK电路中自举电容的工作原理与作用、选型应用方面相关的。 在BUCK电路设计中,一般在CB(BST)和SW管脚之间会放置一颗0.1uF的陶瓷电容Cboot,这颗电容被叫做自举电容; 有的设计中BST和SW之

Zynq芯片的电源分为PS系统和PL逻辑(FPGA)两部分,这两部分的电源区域是完全独立的、被隔离以防止损坏;由于VCCINT_1V0电源电流很大,在靠近电源芯片侧,需要放置2个680uF或4个330uF的电容(由于低气压要求,不能使用钽电容),用于储能;保证100uF、4.7uF、0.47uF电容至少各1个,其余每个电源管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。每个Bank

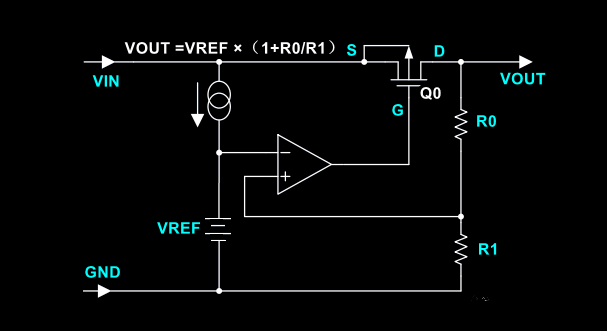

压降电压 Vdrop是指为实现正常稳压,输入电压 VIN必须高出所需输出电压 VOUT 的最小压差,其最小压差是由其架构和工艺决定的,现在的的 LDO 一般采用 CMOS 工艺,压降大大降低,通常为数百毫伏。根据基尔霍夫电压定律,在整个回路中,VIN -VOUT =VSD,即 VIN -VOUT = -VDS,当VOUT 减小时,则 (-VDS)随之增大,工作点由A点移向B点,负载调整率越小越好。

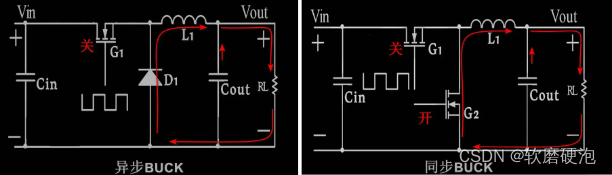

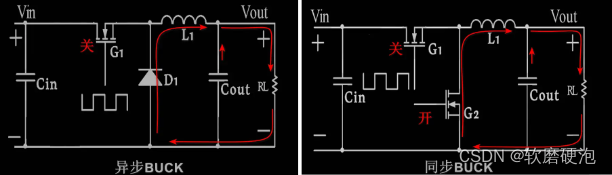

(Force Continuous Conduction Mode):在同步Buck中,用MOSFET替代了二极管,当下管MOSFET导通时,电流从负载瞬间移除,但此时的输出电容在反向放电,负电流由此产生,当输出电流减小时,变换器不会切换到DCM模式,而是转换到强制连续导通模式(FCCM)电流流动如下图,二极管正向导通(开关管G2导通),输入电源Vin不能为负载RL供电,由电感L1、电容Cout向

(Force Continuous Conduction Mode):在同步Buck中,用MOSFET替代了二极管,当下管MOSFET导通时,电流从负载瞬间移除,但此时的输出电容在反向放电,负电流由此产生,当输出电流减小时,变换器不会切换到DCM模式,而是转换到强制连续导通模式(FCCM)电流流动如下图,二极管正向导通(开关管G2导通),输入电源Vin不能为负载RL供电,由电感L1、电容Cout向