简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

人工智能技术正以前所未有的速度从实验室走向产业化,催生了从云端到终端的全方位算力需求。这一变革的核心驱动力,是以ChatGPT、DeepSeek等为代表的大模型技术的突破与普及,它们不仅重塑了人机交互的方式,更引爆了对底层算力基础设施——AI芯片的庞大需求。

一块小小的芯片,如何实现百倍增长的计算能力?答案不在缩小的晶体管,而在颠覆性的封装技术。

全球半导体封测行业迎来涨价扩产潮。受AI芯片和存储需求推动,力成、南茂等厂商产能满载,部分封测价格涨幅达30%。台积电、SK海力士加速扩产先进封装产能,通富微电、长电科技等国内企业也积极布局。行业面临微米级气泡等工艺挑战,屹立芯创的真空贴压膜系统等创新技术为良率提升提供解决方案。IDC预计2025年全球半导体市场持续增长,先进封装技术将成为性能提升的关键,产业链协同创新将推动行业发展。

人工智能技术正以前所未有的速度从实验室走向产业化,催生了从云端到终端的全方位算力需求。这一变革的核心驱动力,是以ChatGPT、DeepSeek等为代表的大模型技术的突破与普及,它们不仅重塑了人机交互的方式,更引爆了对底层算力基础设施——AI芯片的庞大需求。

先进封装技术通过RDL、TSV、Bump和Wafer四大核心要素实现芯片高效互联,显著提升封装密度与性能。关键技术包括:凸块作为电气连接点接口,倒装芯片实现紧凑结构,晶圆级封装分扇入/扇出型满足不同需求,RDL技术重布I/O端口,TSV实现垂直互联。封装设备向高精度发展,键合技术从引线到混合键合持续升级,互联密度提升1000倍以上,能耗大幅降低。预计2025年封装设备市场规模达417亿元,固晶机、

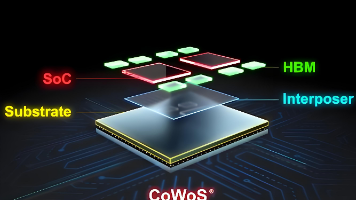

CoWoS(全称 Chip-on-Wafer-on-Substrate,即 “芯片 - 晶圆 - 基板封装”)是由台积电(TSMC)开发并主导的革命性先进封装技术,属于 2.5D 封装的核心代表。它通过在硅中介层(Silicon Interposer)上集成多颗异构芯片(如高性能逻辑芯片与高带宽存储器),并将整个堆叠结构与有机基板互连,实现超高密度、超低延迟的系统级集成,成为推动人工智能(AI)、

人工智能技术正以前所未有的速度从实验室走向产业化,催生了从云端到终端的全方位算力需求。这一变革的核心驱动力,是以ChatGPT、DeepSeek等为代表的大模型技术的突破与普及,它们不仅重塑了人机交互的方式,更引爆了对底层算力基础设施——AI芯片的庞大需求。

先进封装技术路线之争聚焦四大核心命题:性能极限、成本控制、供应链安全和生态主导权。台积电CoWoS以2.5D封装实现高性能但成本高昂;3DIC通过垂直堆叠突破空间限制却受限于良率;Chiplet凭借异构集成降低成本并分散供应链风险。三大技术各具优势:CoWoS垄断高端AI芯片市场,Chiplet在消费电子快速普及,3DIC主导存储领域。当前技术路线正向融合方向发展,台积电3DFabric、英特尔混

半导体测试设备市场迎来AI驱动新机遇。SoC测试机和存储测试机占据主要市场份额,2022年占比分别达60%和21%。AI芯片发展推动SoC测试机需求激增,测试复杂度、时间及性能要求显著提升。HBM技术突破带来存储测试机升级需求,对电流承载、测试精度和并行能力提出更高要求。测试板卡作为核心硬件,其专用芯片仍被国际巨头垄断。国内企业在模拟测试机领域已实现90%国产化,但在高端SoC和存储测试机领域仍有

人工智能技术正以前所未有的速度从实验室走向产业化,催生了从云端到终端的全方位算力需求。这一变革的核心驱动力,是以ChatGPT、DeepSeek等为代表的大模型技术的突破与普及,它们不仅重塑了人机交互的方式,更引爆了对底层算力基础设施——AI芯片的庞大需求。