vitis简介

Vitis是Xilinx推出的统一软件开发平台,基于堆栈架构,支持与开源开发系统无缝集成。该平台整合了原Xilinx SDK,提供C/C++/Python开发环境,适用于FPGA、SoC和Versal ACAP等异构平台的嵌入式系统和加速应用开发。Vitis通过丰富的优化库和高级框架集成,使开发者无需深入硬件知识即可利用Xilinx硬件架构。开发流程包括:使用Vivado进行硬件设计生成XSA文件

Vitis 软件平台作为 Xilinx 公司新的开发软件,是构建在基于堆栈的架构之上,可以无缝的插入到开源的标准开发系统与构建环境。最重要的是, Vitis 包含一套丰富的标准库,使软件开发人员无需深入掌握硬件专业知识,即可根据软件或算法代码自动适配使用 Xilinx 硬件架构

一. vitis简介

Vitis 统一软件平台的前身为 Xilinx SDK,从 Vivado 2019.2 版本开始, Xilinx SDK 开发环境已统一整合

到全功能一体化的 Vitis 中。 Vitis 开发平台除了启动方式、软件界面、使用方法与 SDK 开发平台略有区别,其他操作几乎一模一样。 Vitis 可以采用 C、 C++或 Python 开发以嵌入式处理器为核心的嵌入式系统, 可实现在 Xilinx 异构平台(包括 FPGA、 SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。 它可为边缘、云和混合计算应用加速提供统一编程模型。 Vitis 可以利用与高层次框架的集成,通过加速库采用 C、 C++或Python 进行开发,或者使用基于 RTL 的加速器和低层次运行时 API 对实现方案进行粒度更精确的控制. Vitis是应用 IDE( 集成开发环境). 可实现真正的同构及异构多处理器设计、调试和性能析。

Vitis 统一软件平台是一种新增工具,用于将赛灵思软件开发的方方面面全部组合到统一的环境内。

Vitis 软件平台支持 Vitis 嵌入式软件开发流程以满足希望迁移至下一代技术的赛灵思软件开发套件

(SDK) 用户的使用需求,也支持 Vitis 应用加速开发流程,以满足希望使用基于赛灵思 FPGA 的最新软件加

速功能的软件开发者的需求。

现实生活中各个领域所需的系统都是十分庞大且完整的,通常包含主控制器、存储器、数字信号处理

模块、以及与外部通信的各种接口协议模块等。在基于 FPGA 的系统开发过程中,如果采用纯硬件描述语

言( Verilog/VHDL)去实现这些比较复杂的系统,工作量是十分巨大的,因此可以通过搭建嵌入式系统的

方式去开发功能较为复杂的系统。 为了方便进行嵌入式系统开发, Xilinx 推出了 Vitis 统一软件平台。

Vitis 统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思

硬件架构。此外, Vitis 平台不限制使用专有开发环境,而是可以插入到通用的软件开发工具中,并利用丰

富的优化过的开源库,使开发者能够专注于算法的开发。 Vitis 独立于 Vivado 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是, Vitis 也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率

二. Vitis 开发的流程

使用 Vitis 进行嵌入式设计开发包括两部分,分别是硬件设计和软件设计。硬件设计使用到的工具是

Xilinx 提供的 Vivado 套件,软件设计使用 Xilinx 提供的 Vitis 统一软件平台。

在 Vivado 中我们可以在 Block Design 中搭建嵌入式处理系统,然后生成包含硬件信息的 XSA( Xilinx

Shell Archive)文件。利用 XSA 文件在 Vitis 软件中搭建硬件平台,进行软件设计和调试。

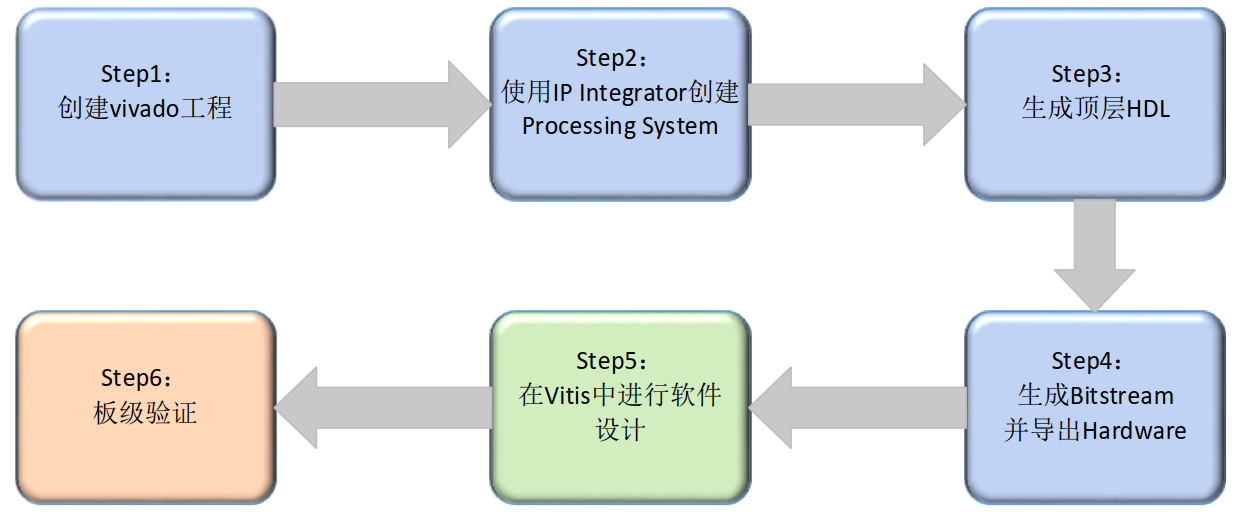

下图是 Vitis 统一平台的嵌入式系统开发流程图:

第一步: 创建 Vivado 工程, 创建方法和《ZYNQ 之 FPGA 开发指南》中描述的步骤一致。

第二步:使用 IP 集成器创建嵌入式处理系统,包括配置 Processing System IP、其他需要的 IP 核以及外

围设备。

第三步:对已经验证好的 Block Design 设计生成顶层 HDL。

第四步:与普通的 FPGA 开发一样,进行综合、实现并生成 Bitstream 文件和 XSA 文件,将生成的硬

件设计文件导出到 Vitis 开发平台下。

第五步:启动 Vitis,创建硬件平台工程和应用工程并完成相关程序的编写、调试、编译。

第六步:进行软硬件联调、完成功能的验证。

如上图所示,开发流程大体上可以分为 6 步。其中 step1 至 step4 为硬件设计部分,在 Vivado 软件中实

现; step5 为软件设计部分,在 Vitis 软件中实现; step6 为功能的验证。复杂的程序还涉及 Debug,这个也是在 Vitis 中实施,具体每一步的操作我们会在后面的例程实验章节中详细介绍。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)