Mit6.004-05-Sequential Logic

1.某些我们仍无法构建的组合设备:输出仅取决于此时输入灯开,按钮按下后,灯变关灯关,按钮按下后,灯变开输入:按钮,输出:灯,输出取决于设备当前状态以及输入2.数字状态:我们想要构建的这种组合逻辑和内存组件组成的电路称为时序逻辑本章主要目的是构建内存组件3.内存:使用电容电压用来编码信息,电容用来存储电压写:bitLine设置为要写入的电平,wordLine设高电平打开FET开关,让电容变为与bit

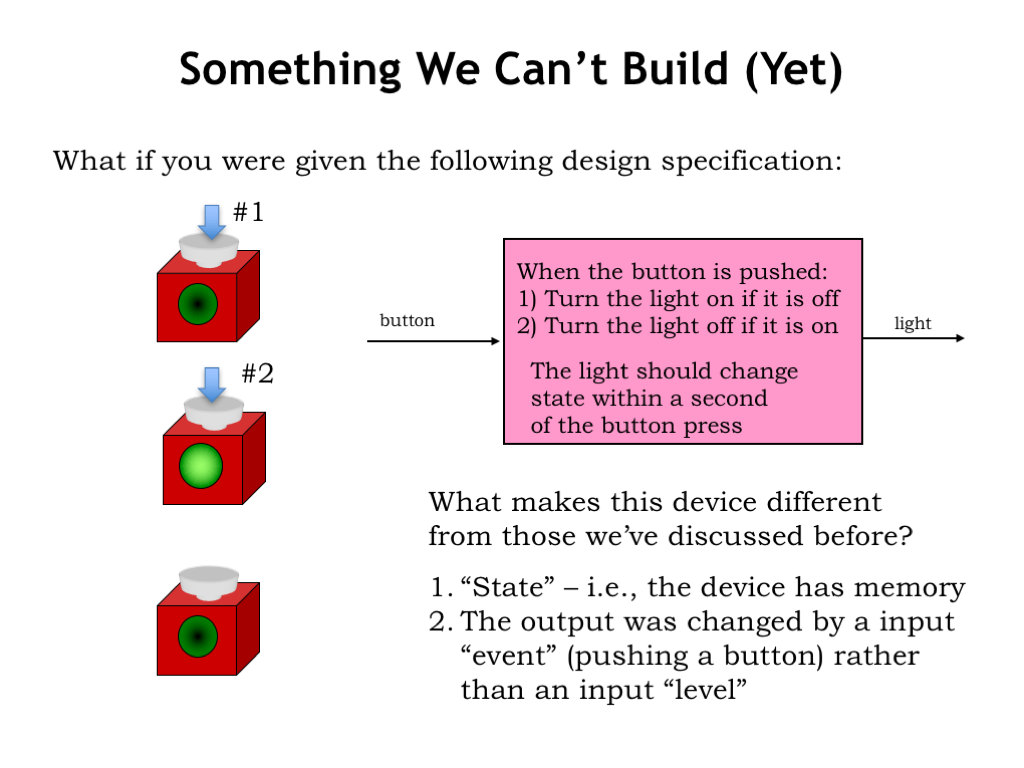

1. 某些我们仍无法构建的

组合设备:输出仅取决于此时输入

灯开,按钮按下后,灯变关

灯关,按钮按下后,灯变开

输入:按钮,输出:灯,输出取决于设备当前状态以及输入

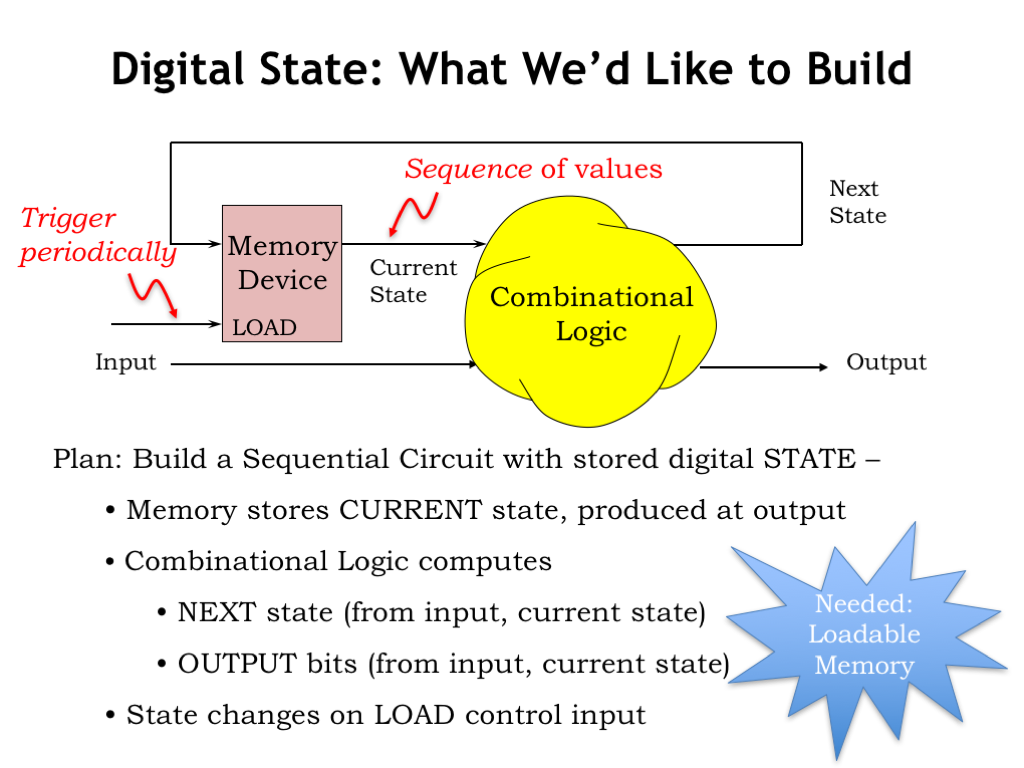

2. 数字状态:我们想要构建的

这种组合逻辑和内存组件组成的电路称为时序逻辑

本章主要目的是构建内存组件

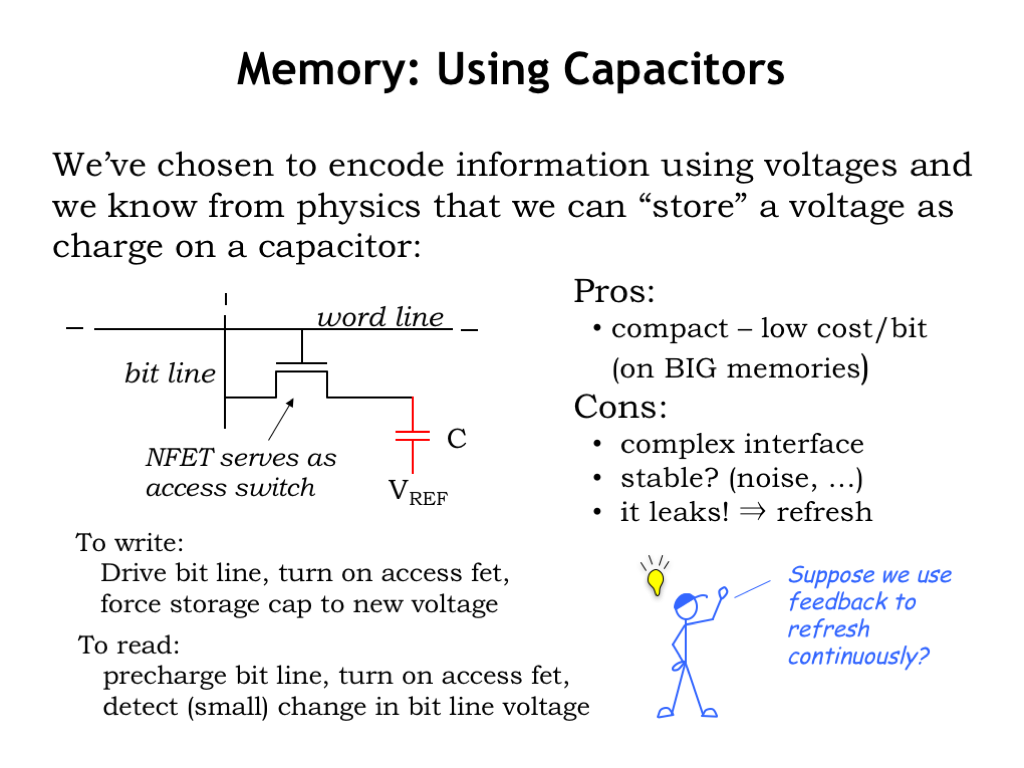

3. 内存:使用电容

电压用来编码信息,电容用来存储电压

写:bitLine设置为要写入的电平,wordLine设高电平打开FET开关,让电容变为与bitLine一样的电压

读:bitLine预先设置为某个电压,wordLine设高电平打开FET开关,通过bitLine电压变化判断高低电压

因FET并不理想,关状态也有电流通过,因此电容电荷会衰减,需要电容失效前,重写

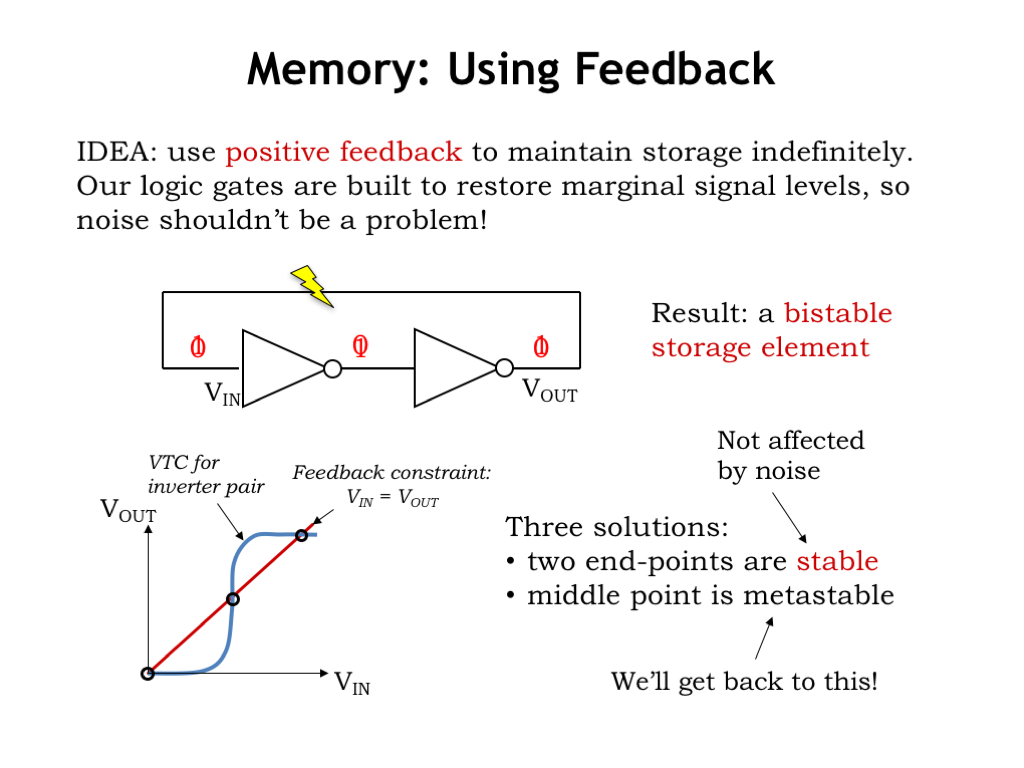

4. 内存:使用反馈

两个反相器一个正反馈电路

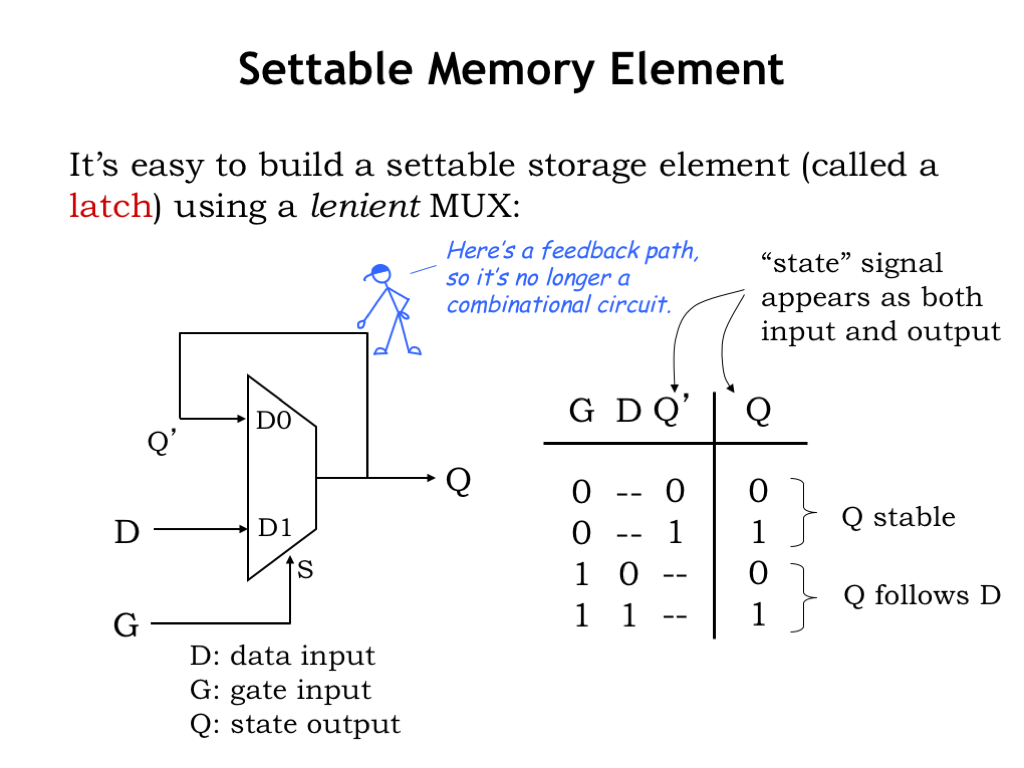

5. 可设置的内存元素

G设置低电平,电路为一稳态电路,输出取决于Q’

G设置高电平,电路输出取决于D

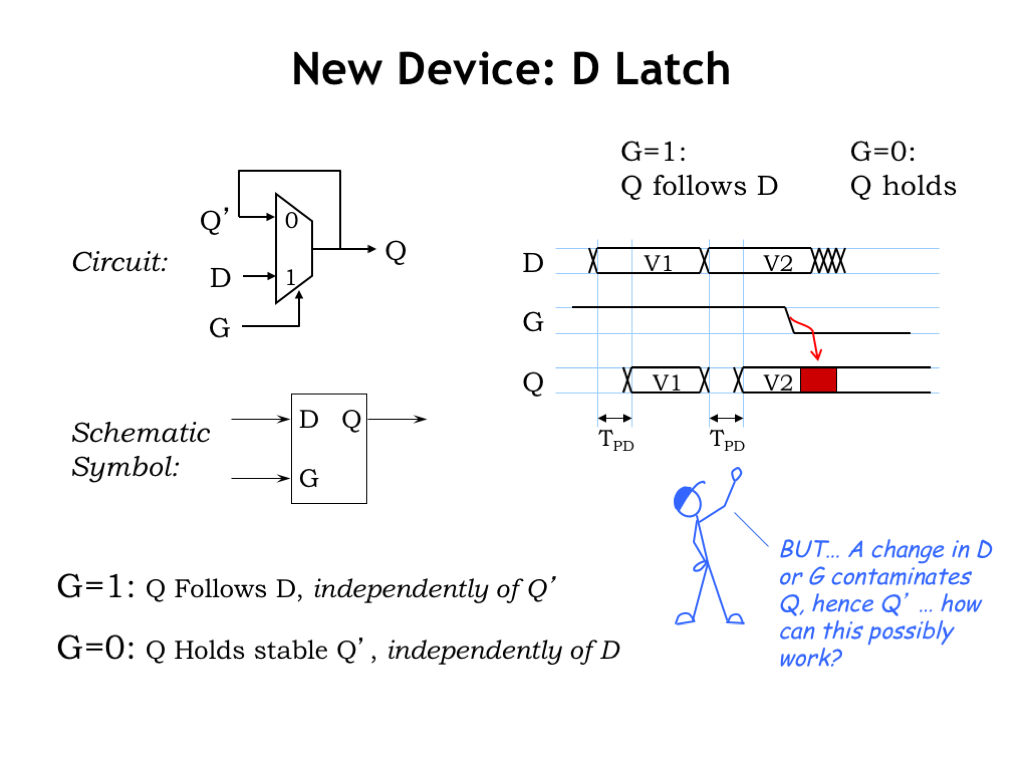

6. 新设备:D门闩

Q输出取决于G从高电平变为低电平时,D的状态

G位于高电平时,D的电压变化,体现在Q上时,有TPD延时

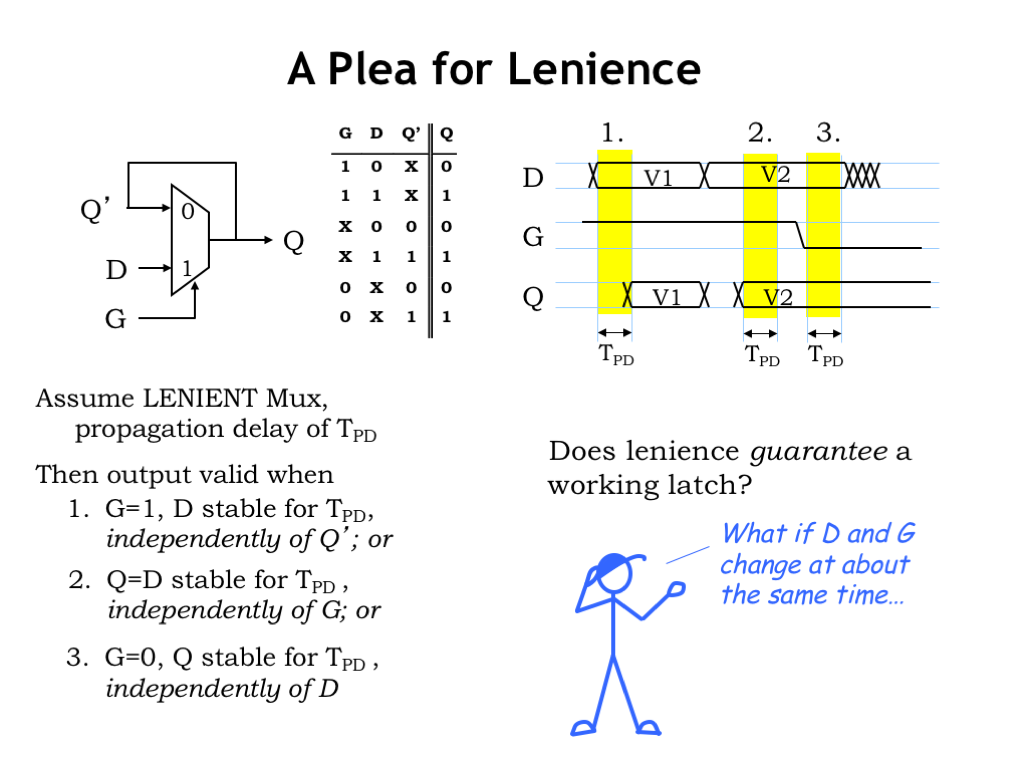

7. 宽容请求

(1) G=1,D有效TPD时间后,Q输出为D,无论Q’是什么

(2) Q=D稳定TPD时间后,无论G是什么,Q=D

(3) G=0且Q稳定TPD后,输出不会受D影响

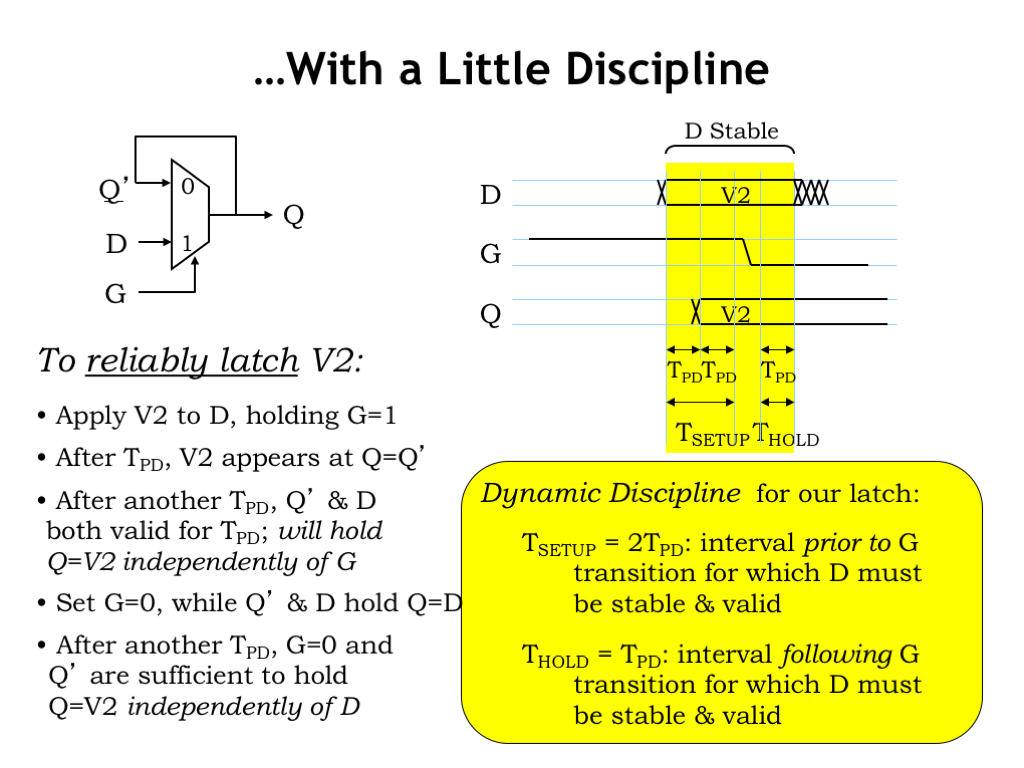

8. 一小点规则

动态规则:在G从高电平到低电平,之前2*TPD,之后TPD,保证输入D有效且稳定

遵循动态规则,则可以保证内存组件将可靠地存储D上的信息,在门从高到低传递期间

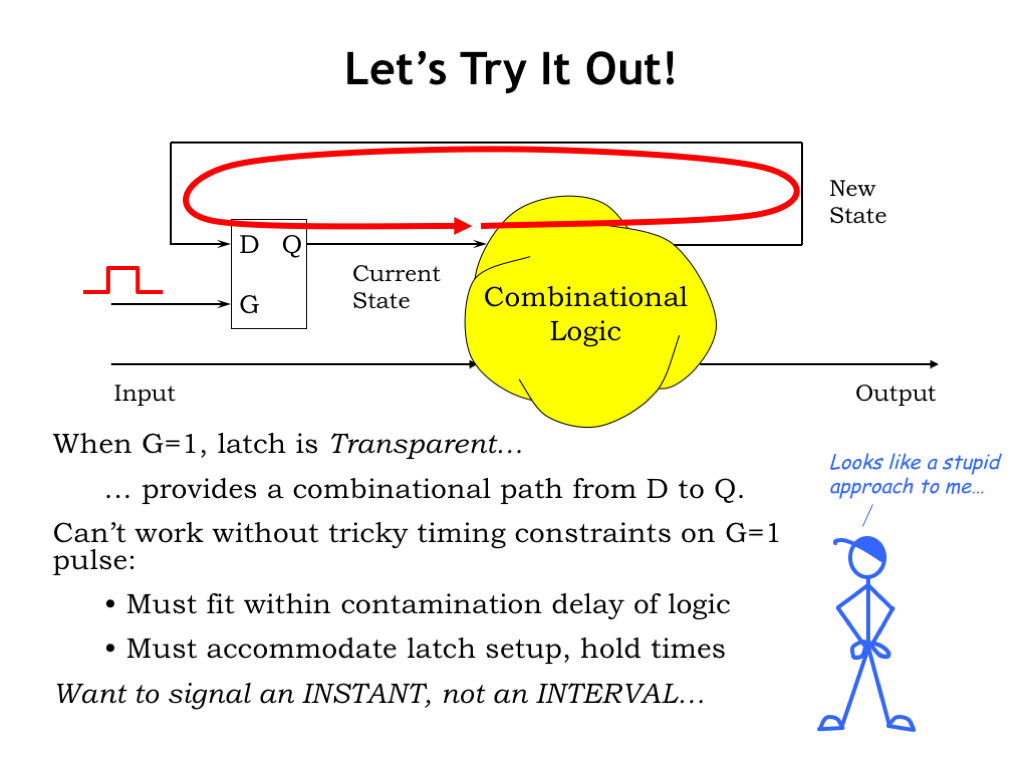

9. 试试看

G高电平持续时间不能过长,不能过短

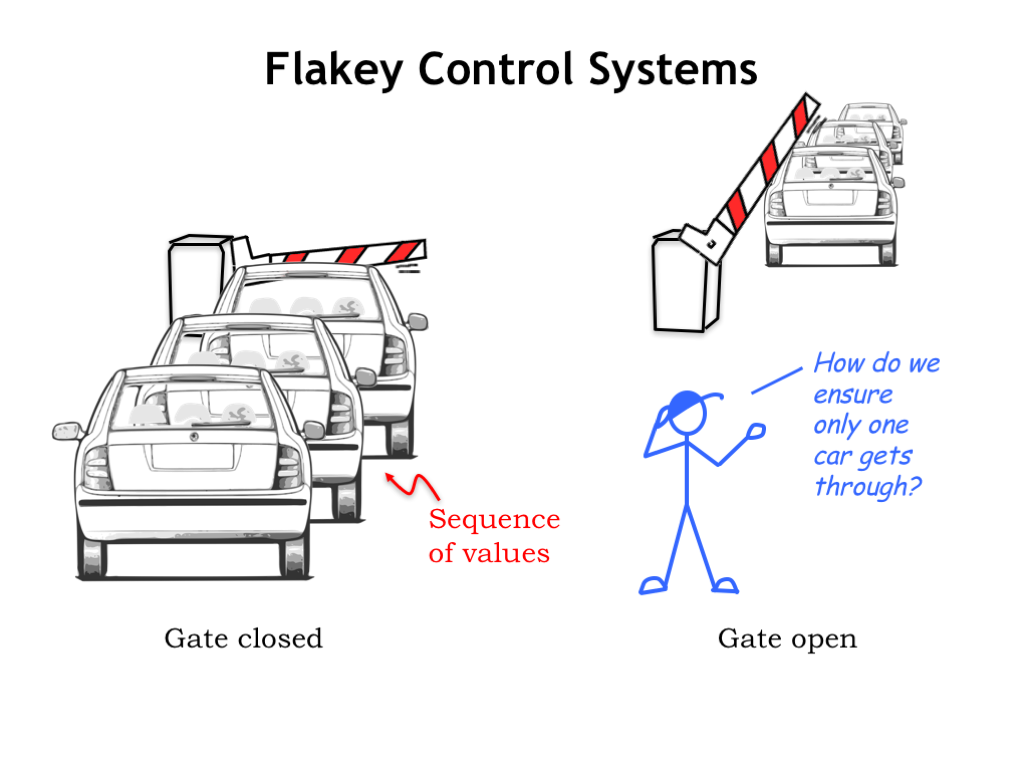

10. 片状控制系统

一排汽车排队等着过收费站,如何保证每次只有一个汽车过去,收费站打开时间不能过长,也不能过短

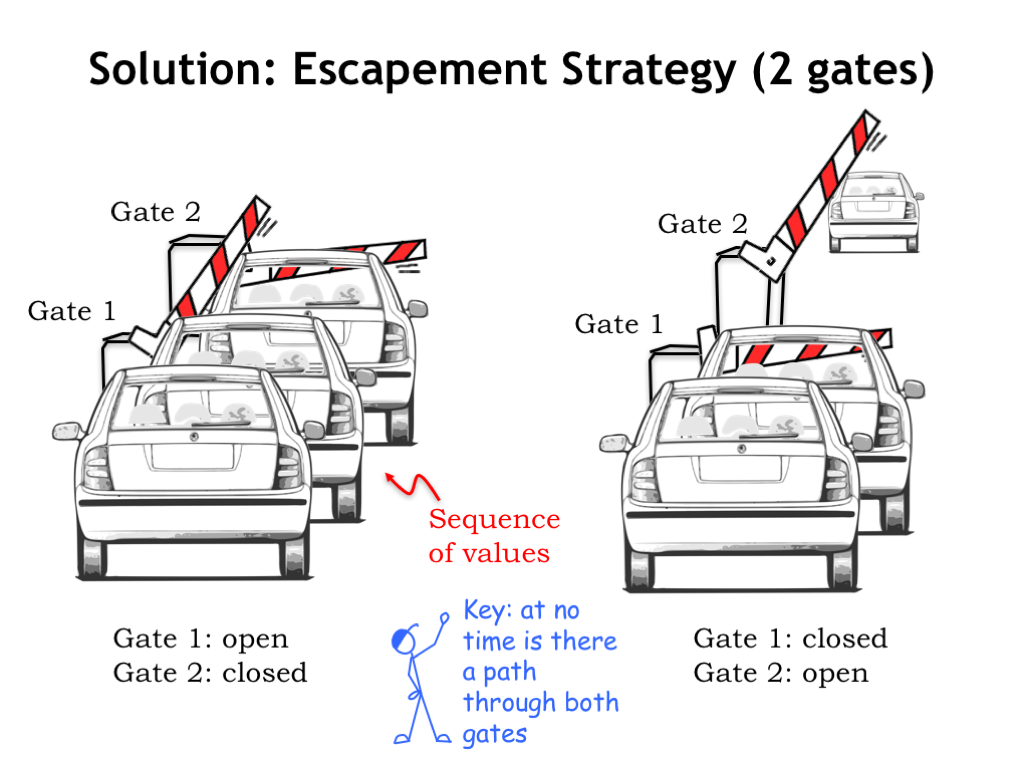

11. 擒纵策略

1门开,2门关,收费站进入一个车,1门关,2门开,收费站中的车出去。同一时间,门1、2不会同时开

2门打开的频率,即收费站处理速度

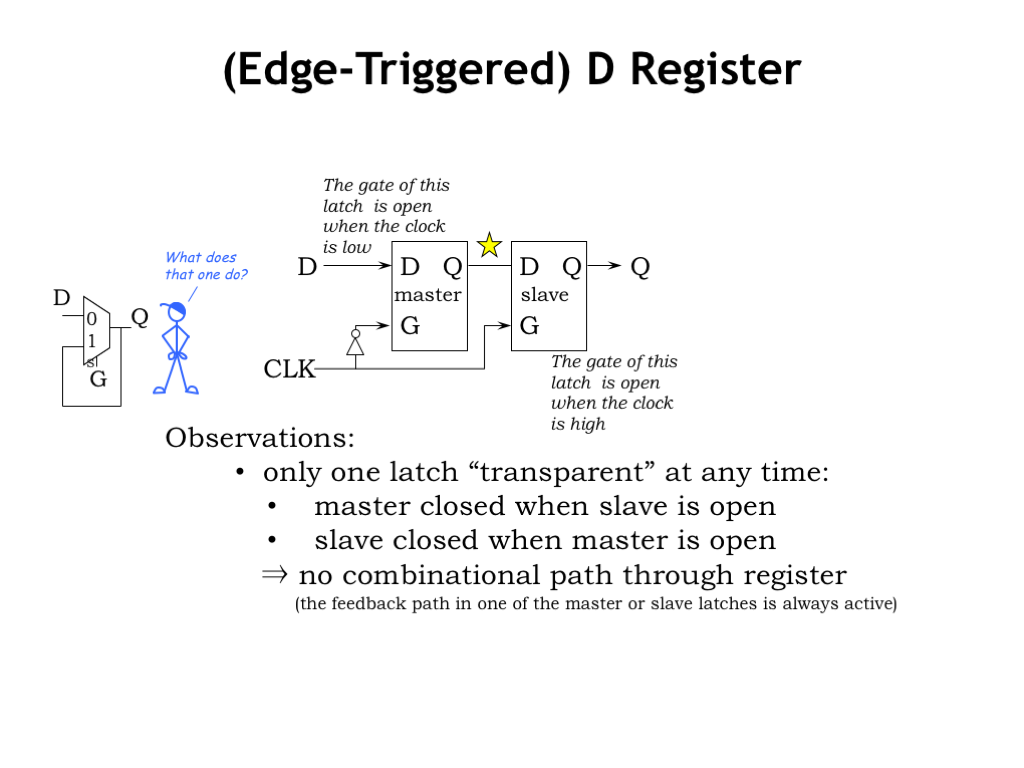

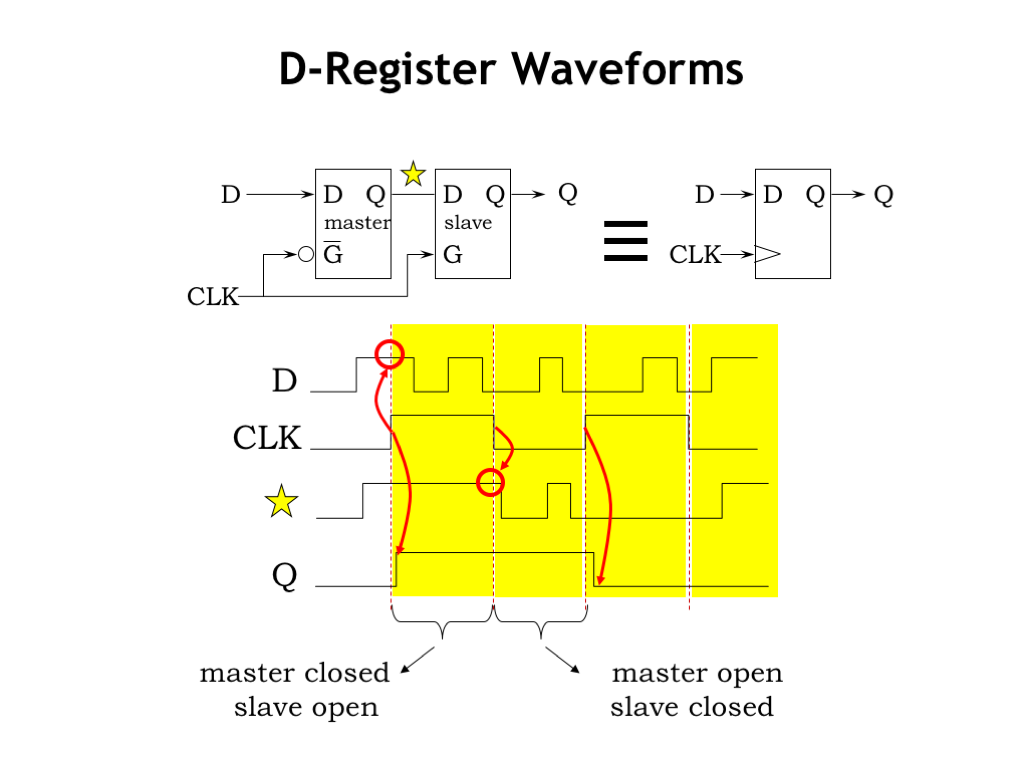

12. 边沿触发 D寄存器

master latch有无反相器实现

13. D寄存器波形

CLK低电平时,主开从关,星处波形随D而改变

CLK高电平时,主关从开,输出Q变为星处电平

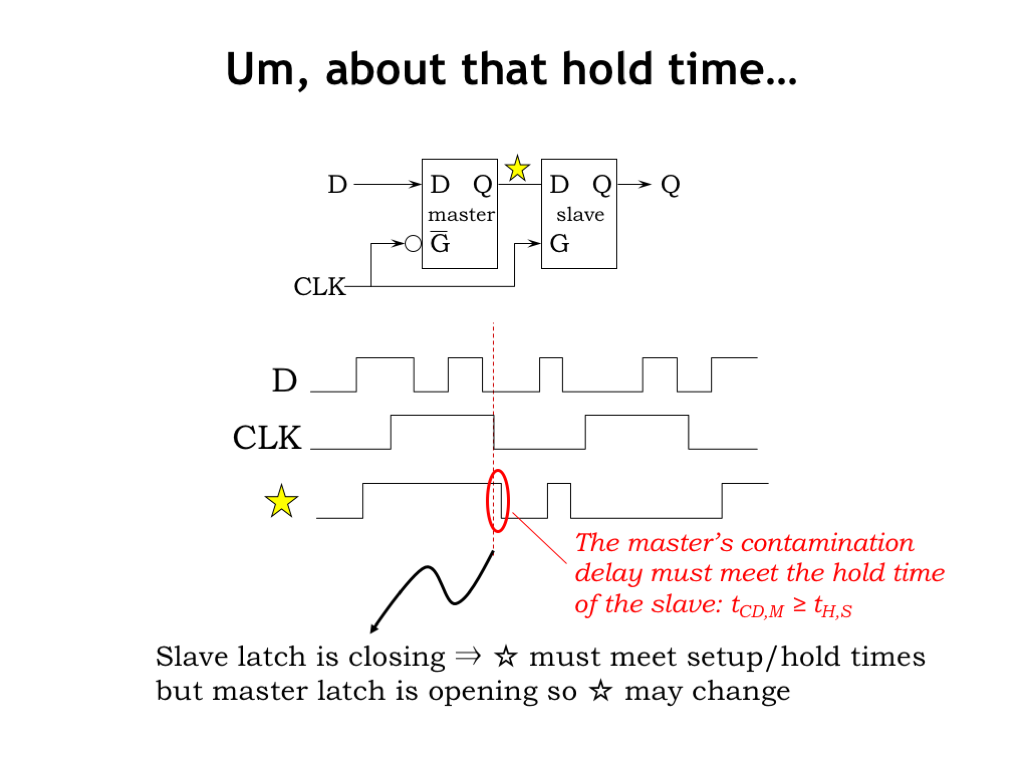

14. 有关持有时间

Tcd,m>=Th,s

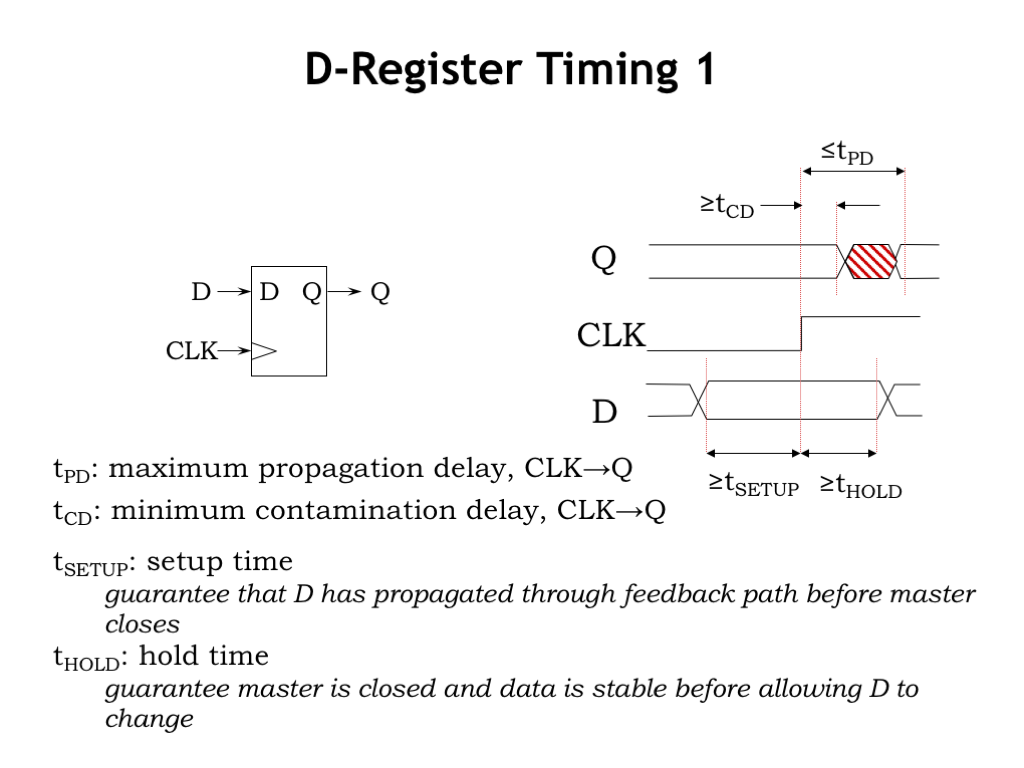

15. D寄存器时间1

Tpd:上升沿到Q输出有效的时长

Tcd:上升沿到Q保持之间值有效的时长

寄存器是宽容的,所以Tpd、Tcd仅存于Q真发生改变的时候

Tsetup:保证latch在关闭之前,Q已经到达输入Q’

Thold:保证latch在开启之前,已经将电压保存了下来

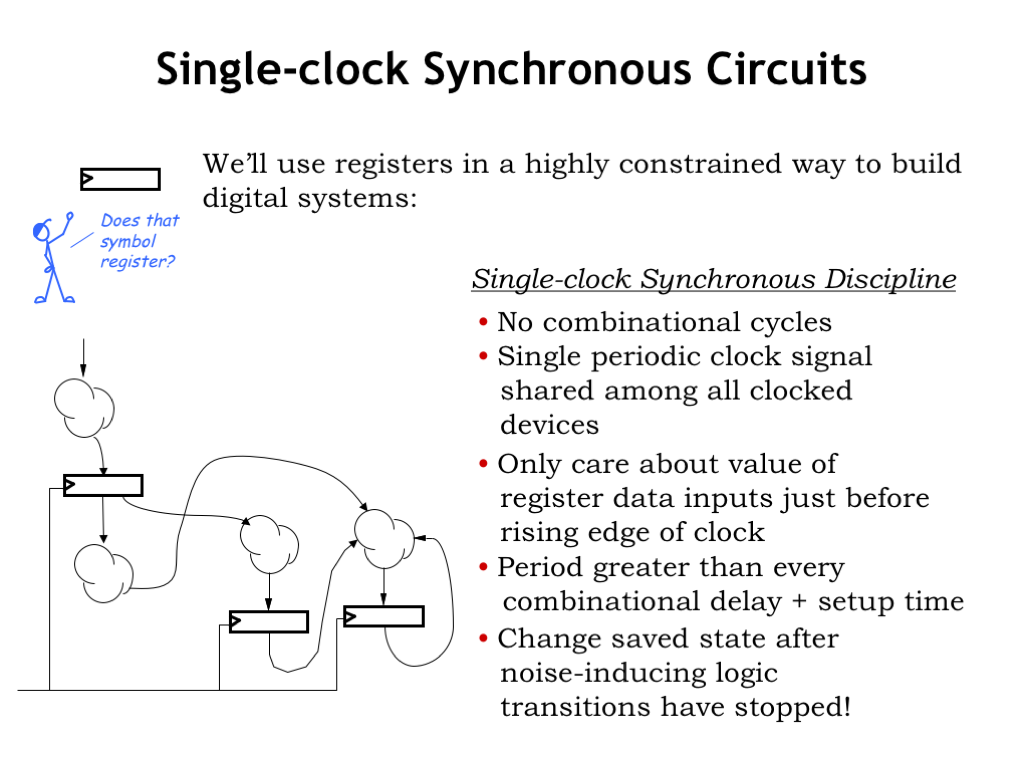

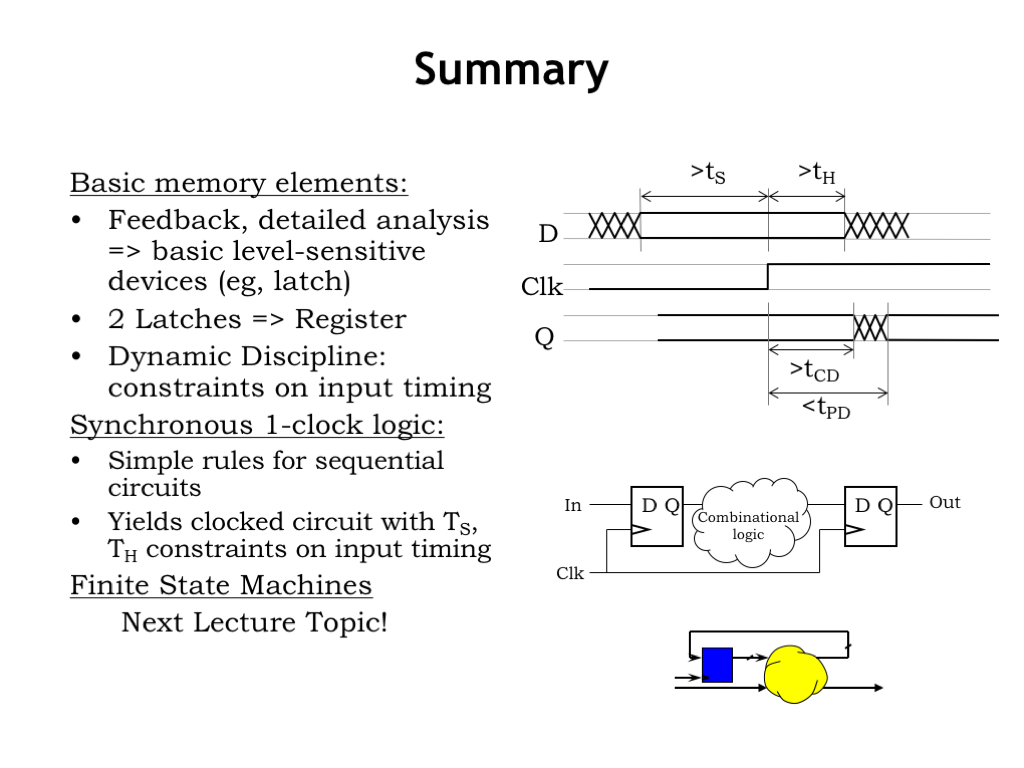

16. 单时钟同步电路

所有时钟设备共享同一时钟信号

时钟周期大于:每个寄存器输出到寄存器输入的时间+寄存器设置时间

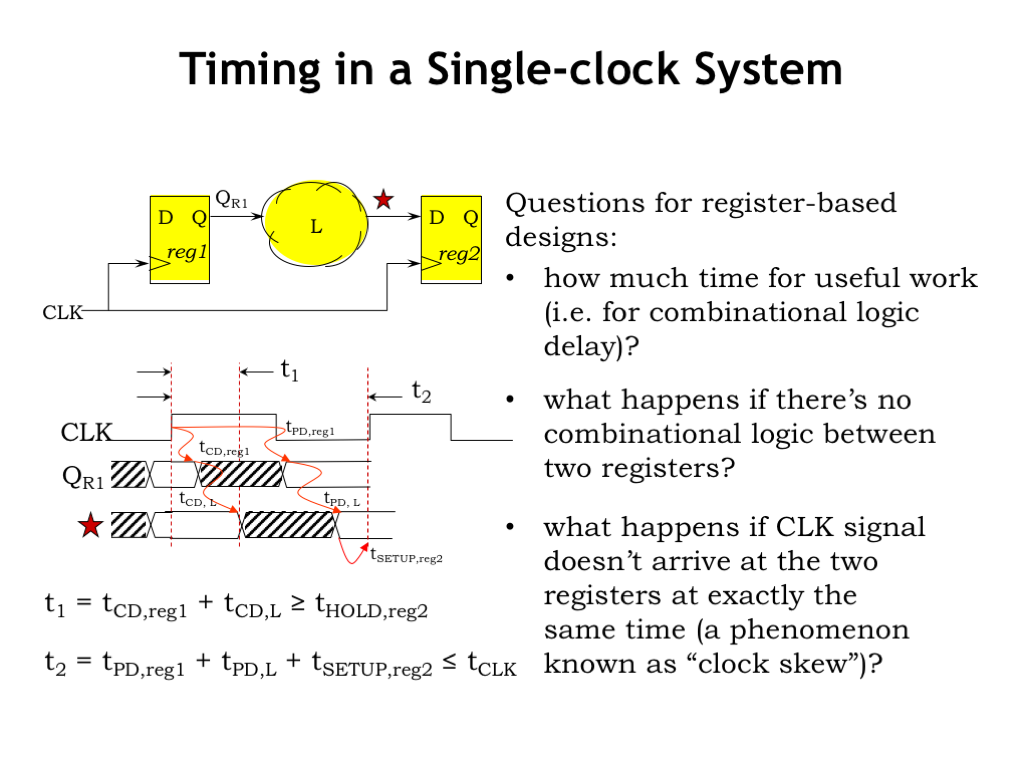

17. 单时钟系统时序

tCLK一般称作时钟周期,寄存器tpd和tsetup越小,时钟周期可以越小

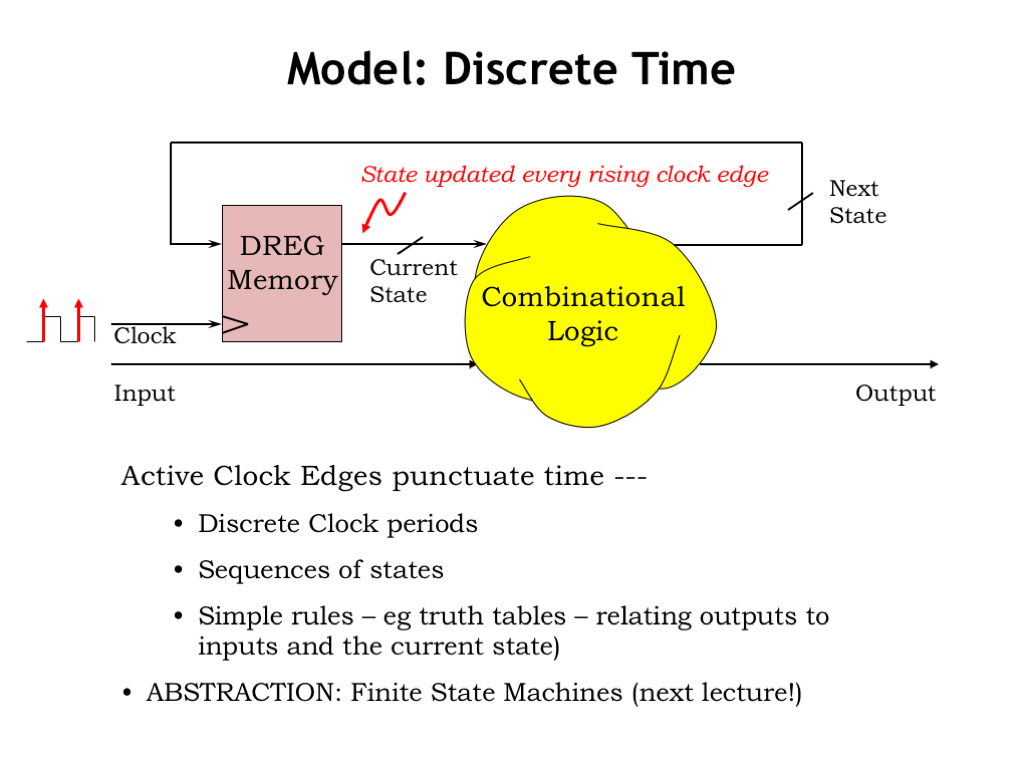

18. 离散时间

每次上升沿之后,时钟周期剩余时间内,内存组件的输出作为当前状态,经过组合逻辑形成输出

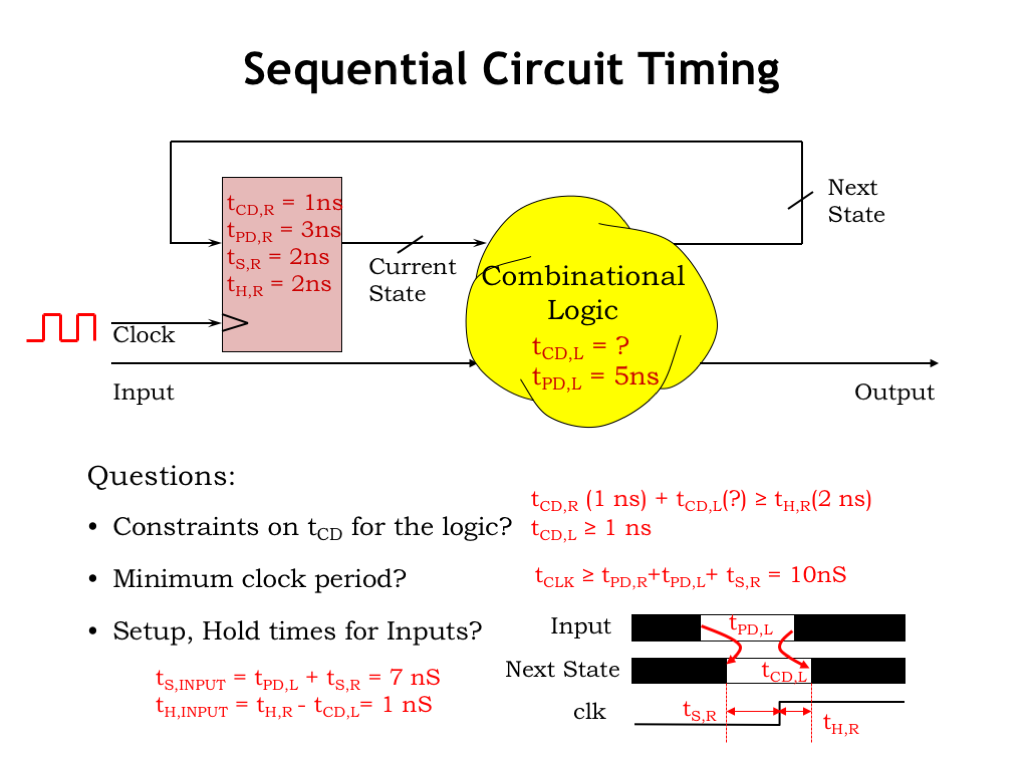

19. 时序电路时间

20. 总结

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)