简介

该用户还未填写简介

擅长的技术栈

未填写擅长的技术栈

可提供的服务

暂无可提供的服务

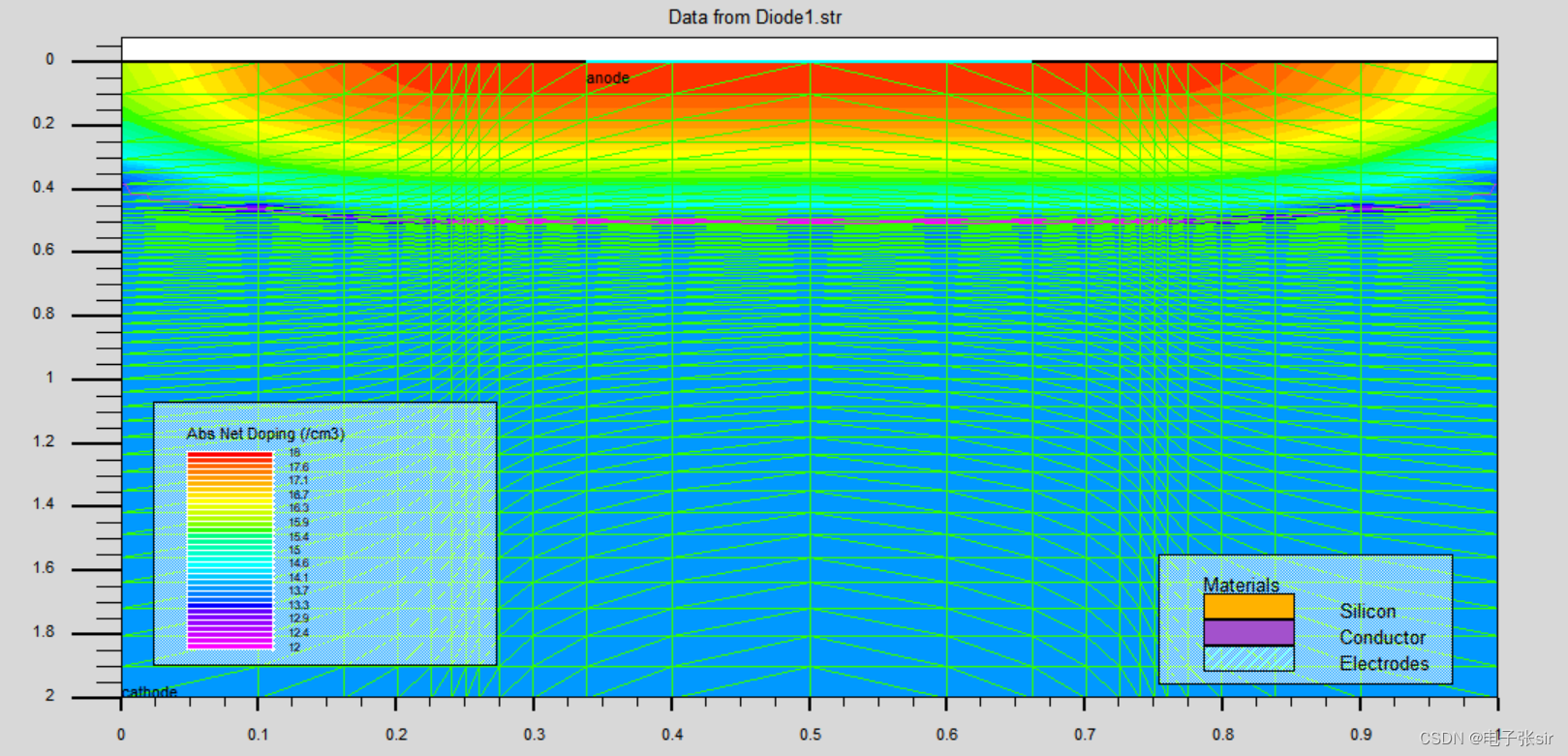

sivalco使用测试pin正向导通

在学完功率半导体器件后,为了能够更好的了解功率半导体器件内部的相关性质,于是利用sivalco软件进行仿真,对于器件工作时相关数据进行分析,对于相关语句进行学习,这里以PN结模型仿真,PIN正向导通和反向阻断为例。

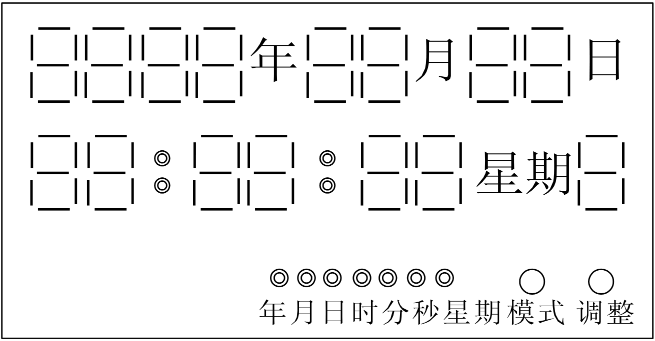

[EDA] 综合计时系统设计 【VHDL】

设计综合性的计时系统,能实现年、月、日、时、分、秒及3星期的计数等综合计时功能,并且将计时结果通过三次显示至开发板上,通过设计俩个按键,在计时过程中,对计时系统的有关参数进行调整。

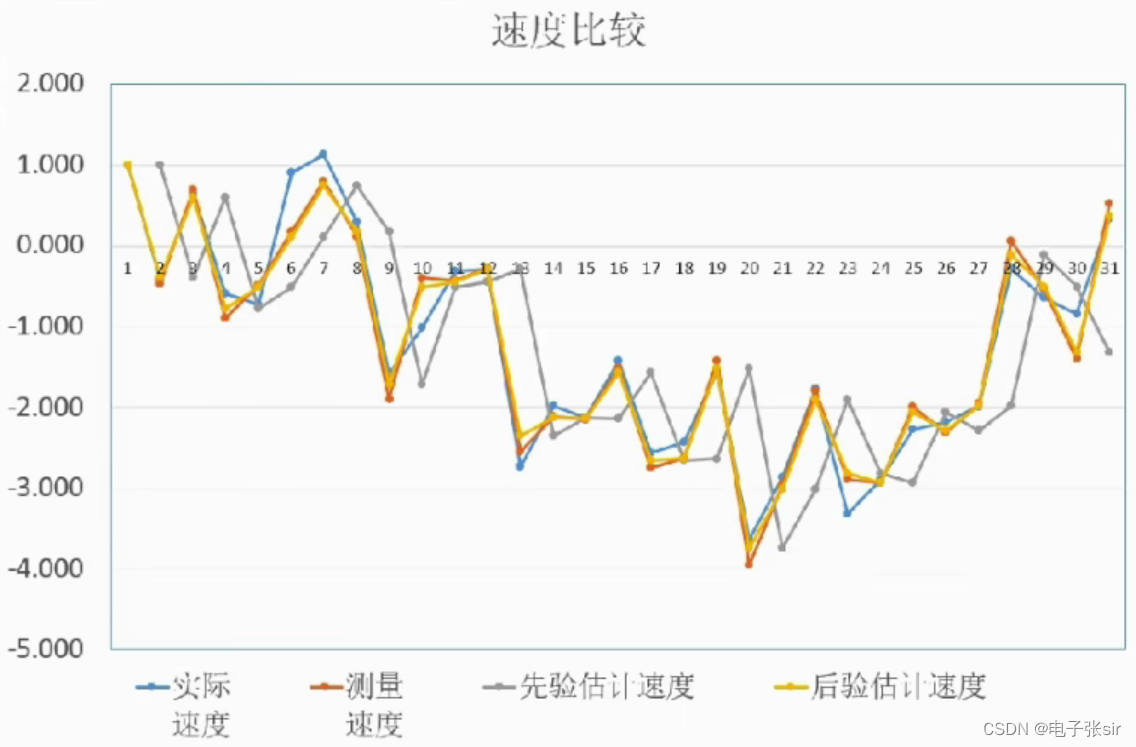

卡尔曼滤波原理公式详细推导过程[包括引出]

将从最初的递归算法,利用数据融合,协方差矩阵,状态空间方程等基础推导,最终分析卡尔曼滤波5个方程全部的推导过程,其过程有很多晦涩难懂的公式,我会尽量的表达清楚和加入一些个人理解,从而使得较为便于理解

【EDA实验DTCNT9999及DTCNT999999999999】

本实验基于VHDL语言设计一个能够动态的显示0-9999的4位十进制计数电路,在不同频率下不同速率的显示。对DTCNT9999的扩展到12个9的程序解析。

到底了